DER AD Adam Valance - 1111 - ---

in the second

Ò . .

To be provided.

$\bigcirc$

•

| 1 | SYSTEM OV  | RUEW                                 |      |

|---|------------|--------------------------------------|------|

|   |            | System Configurations                | 1-4  |

|   |            | CPE Overview                         | 1-6  |

|   |            | Memory Overview                      | 1-13 |

|   |            | Input/Output Subsystem Overview      | 1-16 |

| 2 | MEMORY     | NOSPE                                |      |

| 3 | CPU        | O ARE                                |      |

| 4 |            | JT SUBSYSTEM                         |      |

| - |            |                                      |      |

|   |            | Basic Architecture                   | 4-1  |

|   |            | IOBB                                 | 4-2  |

|   |            | Communications                       | 4-5  |

|   |            | IOS-supported Peripheral Controllers | 4-7  |

| 5 | PERIPHERAL | DEVICES                              |      |

| TD-2 Tape Drive       | 5-3  |

|-----------------------|------|

| TD-3 Tape Drive       | 5-5  |

| Disk Array Controller | 5-15 |

| Diagnostics           | 5-17 |

# **6 DIAGNOSTICS**

| Online Diagnostics  | <br>6-1 |

|---------------------|---------|

| Offline Diagnostics | <br>6-4 |

## 7 POWER AND CONTROL SYSTEMS

# 8 UNICOS ADMINISTRATION

#### 9 MWS ADMINISTRATION

#### **10 FIELD REPAIR PROCEDURES**

#### **APPENDIX A**

#### **APPENDIX B**

#### **APPENDIX C**

#### FIGURES

| Figure 1-1. Left Side View (Maximum configuration) | 1-1  |

|----------------------------------------------------|------|

| Figure 1-2. Front-Right View, Cabinet A            | 1-2  |

| Figure 1-3. Remote Seismic System                  | 1-5  |

| Figure 1-4. Departmental System                    | 1-5  |

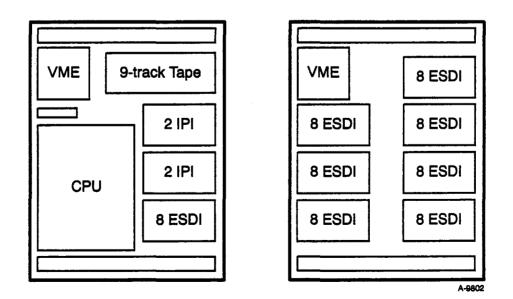

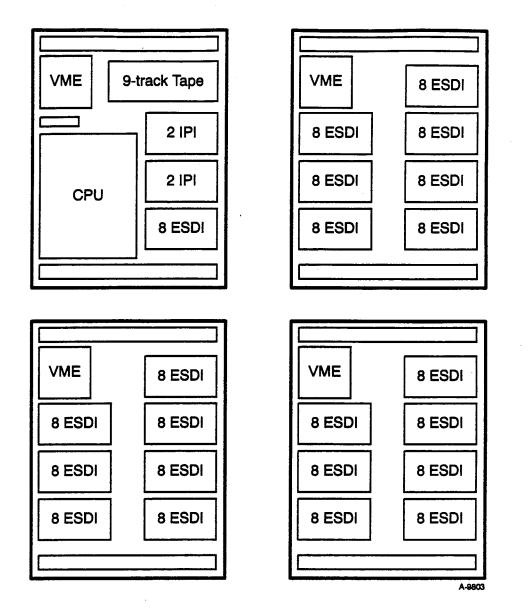

| Figure 1-5. File Server System                     | 1-6  |

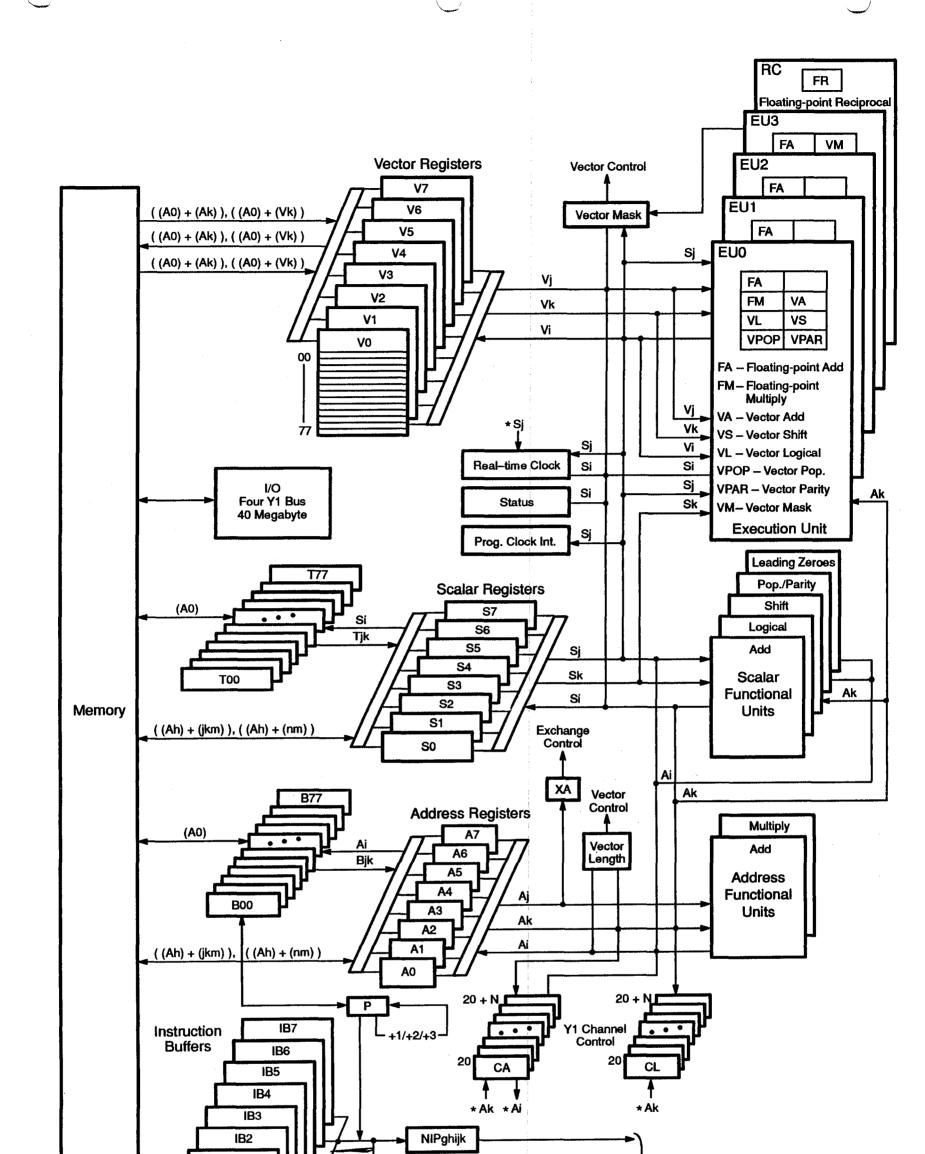

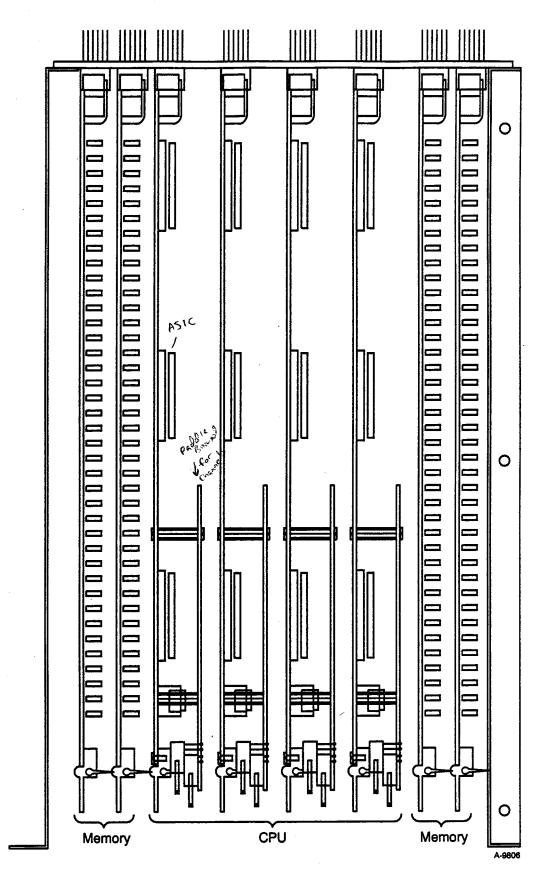

| Figure 1-6. CPU/Channel Module                     | 1-8  |

| Figure 1-7. CRAY Y-MP EL Block Diagram             | 1-11 |

| Figure 1-8. Memory Module                          | 1-14 |

| Figure 1-9. Chassis, Top View                      | 1-15 |

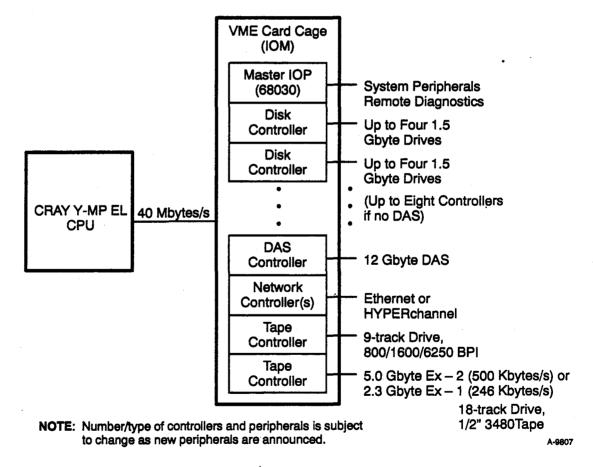

| Figure 1-10. IOS Configuration                     | 1-16 |

| Figure 2-1. Memory Module                          | 2-2  |

| Figure 2-2. Address Bit Assignments                | 2-3  |

| Figure 2-3. Mainframe Chassis, Front View          | 2-4  |

| Figure 2-4. Example of Address Decode              | 2-6  |

| Figure 2-5. Memory Block Diagram                   | 2-9  |

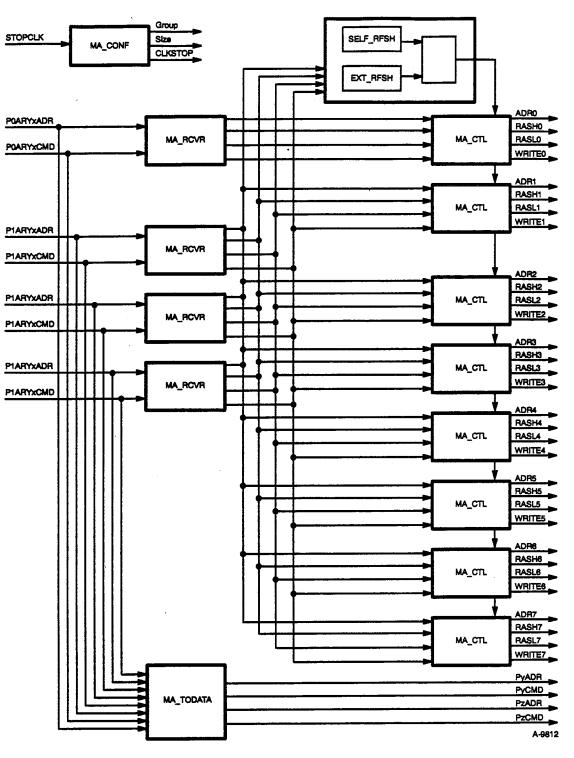

| Figure 2-6. Memory Array Data Block Diagram                          | 2-11 |

|----------------------------------------------------------------------|------|

| Figure 2-7. Memory Array Control Block Diagram                       | 2-12 |

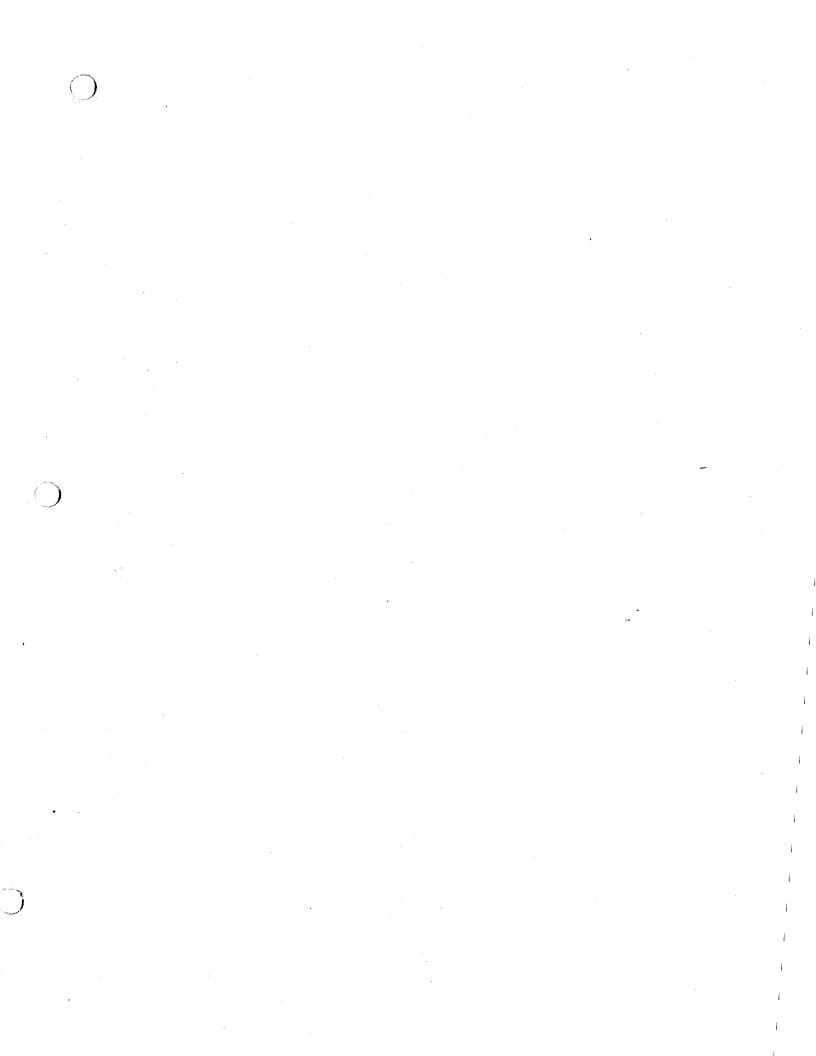

| Figure 3-1. CRAY Y-MP EL Block Diagram                               | 3-5  |

| Figure 3-2. CPU Bus Block Diagram                                    | 3-7  |

| Figure 3-3. CPU/Channel Module                                       | 3-9  |

| Figure 3-4. Exchange Package                                         | 3-11 |

| Figure 4-1. IOBB Communication                                       | 4-4  |

| Figure 4-2. IOBB Block Diagram                                       | 4-5  |

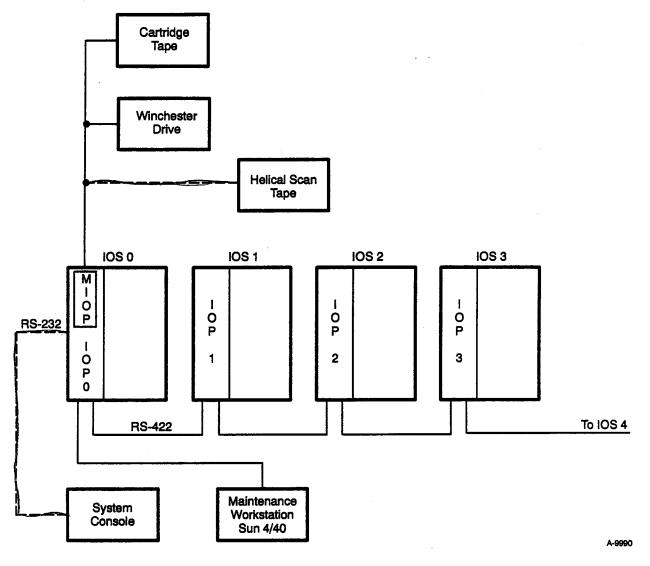

| Figure 4-3. IOP Daisy Chain Configuration                            | 4-6  |

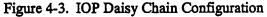

| Figure 4-4. IOS Specifications                                       | 4-8  |

| Figure 5-1. Example of Cabinet Layout for the CRAY Y-MP EL<br>System | 5-3  |

| Figure 5-2. TD-3 Tape Drive (Power Supply)                           | 5-6  |

| Figure 5-3. TD-3 Tape Drive (FRUs)                                   | 5-7  |

| Figure 5-4. TD-3 Tape Drive (FRUs)                                   | 5-8  |

| Figure 5-5. TD-3 Tape Drive Front Panel                              | 5-10 |

| Figure 5-6. Basic 4280 Menus with a SCSI Interface                   | 5-11 |

| Figure 5-7. TD-3 Tape Drive Controller Module FRUs (Front View)      | 5-12 |

| Figure 5-8. TD-3 Tape Drive Controller Module FRUs<br>(Rear View)    | 5-13 |

| Figure 5-9. TD-3 Chassis                                             | 5-14 |

| Figure 5-10. DAC Printed Circuit Board Locations                     | 5-16 |

## TABLES

| Table 2-1. DRAM Locator Chart                  | 2-5 |

|------------------------------------------------|-----|

| Table 6-1. Online Diagnostics                  | 6-2 |

| Table 6-2. Down Device Programs                | 6-4 |

| Table 6-3. Offline Diagnostics - Level 0 Tests | 6-5 |

| Table 6-4. Offline Diagnostics - Monitors      | 6-5 |

| Table 6-5. Offline Diagnostics - Level 1 Tests | 6-6 |

0. )

# SYSTEM OVERVIEW

The CRAY Y-MP EL computer system is a completely self-contained system. This means that the central processing unit (CPU), input/output subsystem (IOS), and all peripherals are contained in one easily moved cabinet. The cabinet can be moved easily to most general office environments equipped with a 200- to 250-Vac power source and be operational.

One to four CPU boards can be installed in the CRAY Y-MP EL system cabinet. This cabinet also holds four memory boards, an IOS contained within a VMEbus based assembly, and the optional peripherals requested by the customer. Another area in the frame contains the small computer system interface (SCSI) subsystem. The SCSI subsystem consists of a cartridge-type streaming tape drive, a 780-Mbyte hard disk drive, and an optional 8-mm helical scan tape drive. This SCSI subsystem is analogous to the expander chassis that formed part of the CRAY X-MP computer system. The SCSI is used to install any new releases of software as they become available. It also has the capability of performing data transfers and being the system backup and boot device.

The primary frame is constructed so that another standard frame can be bolted to the primary frame to expand the system. It is possible to connect as many as three secondary frames to the primary frame; thus, the CRAY Y-MP EL system can contain as many as 16 IOSs and additional peripheral devices.

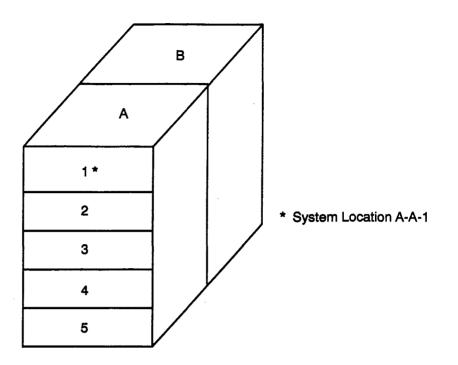

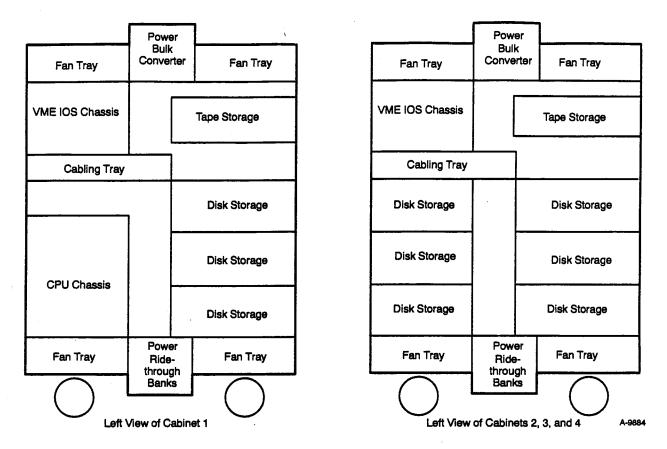

Figure 1-1 and Figure 1-2 can be used to locate the four cabinets that can be configured and the various subassemblies within the CRAY Y-MP EL system.

Figure 1-1. Left Side View (Maximum configuration)

Figure 1-2. Front-Right View, Cabinet A

All of the frames forming the CRAY Y-MP EL system are air cooled by integrated fans at both the top and bottom of the frame. This form of cooling is referred to as vertical cooling.

The peripheral devices available on the CRAY Y-MP EL system and their characteristics are listed below.

- DS-3 Disk Storage System

- 5.25-inch format Winchester disk drive

- Holds 1.5 Gbytes of unformatted data per drive

- Transfer rates are between 1 and 1.75 Mbytes/s

- Average seek time is 15 milliseconds

- Mean time between failures (MTBF) is estimated at 150,000 hours

- DC-3 controller controls up to four enhanced serial drive interface (ESDI) disk drives

- Each disk controller provides error correction code (ECC) and media defect management

- DD-3 low performance disk unit

- 1.5 Gbytes; 5.25 inch ESDI drive

- 2.75-Mbyte/s transfer rate

- Packaged ten drives per drawer with a shared power supply

- DS-4 disk storage system

- DD-4 medium performance disk unit

- 3.0 Gbyte 8-inch two-head IPI dual port disk drives

- 9.34 Mbytes/s transfer rate

- Packaged two disk drives per drawer with one per drive

- DC-4 controller controls intelligent peripheral interface (IPI-2) containing two IPI channels; each channel can handle two DD-4 drives

- DAS-2 disk array subsystem

- Intelligent disk array controller

- Bank of eight 1.5-Gbyte ESDIs for storage plus one for parity and one spare

- Hardware striping used to distribute data evenly across all drives

- Sustained transfer rate of 13 Mbytes/s

- Has 12-Gbyte unformatted capacity

- Tape units

- 9-track tape drive subsystem

- One TCU-2 tape controller unit

- One TD-2800 bpi (NRZI), 1600 bpi (PE), 6250 bpi (GCR)

9-track low profile tape drive, 125 ips

- Cartridge tape drive (EXABYTE) models

- EX-1 2.3 Gbyte, EXB-200 246K/s 8-mm tape drive

- EX-2 5.0 Gbyte, EXB-850 500K/s 8-mm tape drive

- TD-3 .5-inch cartridge tape drive; 3480-type tape

- DR-1 removable disk system

- Dual 5.25-inch disks in easily removable cartridges designed to protect data from damage during transport

- DR-2 removable IOS disk drive

- TD-2 autoloading low profile 9-track tape drive

- TD-3 .5 inch cartridge; 3480-type tape drive

Customers select peripheral devices according to their requirements, some of which are dictated by the system requirements.

## System Configurations

Three system configuration examples are offered to fill the specific needs of the customer. In many cases, the configuration defines the peripheral options selected. The three configurations are: remote seismic option, departmental system, and file server system. The characteristics of each of these configurations are listed below.

- Remote seismic system (refer to Figure 1-3).

- Low overall system cost

- 9-track tape capability

- 2 to 4 VMEbus channels

- Minimum disk space required (10 to 20 Gbytes)

- Single 19-inch frame

- Departmental supercomputer system (refer to Figure 1-4).

- Compatible with office environment

- Compact size

- Low power consumption

- Minimal heat dissipation

- Quiet operation

- Easy to network

- 4 to 8 VMEbus channels

- Customer-specified disk capacity

- 32 to 64 Gbytes of ESDI disk drive storage

- Higher performance DAS or IPI drives

- Tape backup system

- 1 or 2 19-inch frames

- File server system (refer to Figure 1-5).

- Computer room environment

- Significant disk storage space (200 to 400 Gbytes)

- 8 to 16 VMEbus channels

- Up to 4 racks per system

Figure 1-3. Remote Seismic System

Figure 1-4. Departmental System

# **CPU Overview**

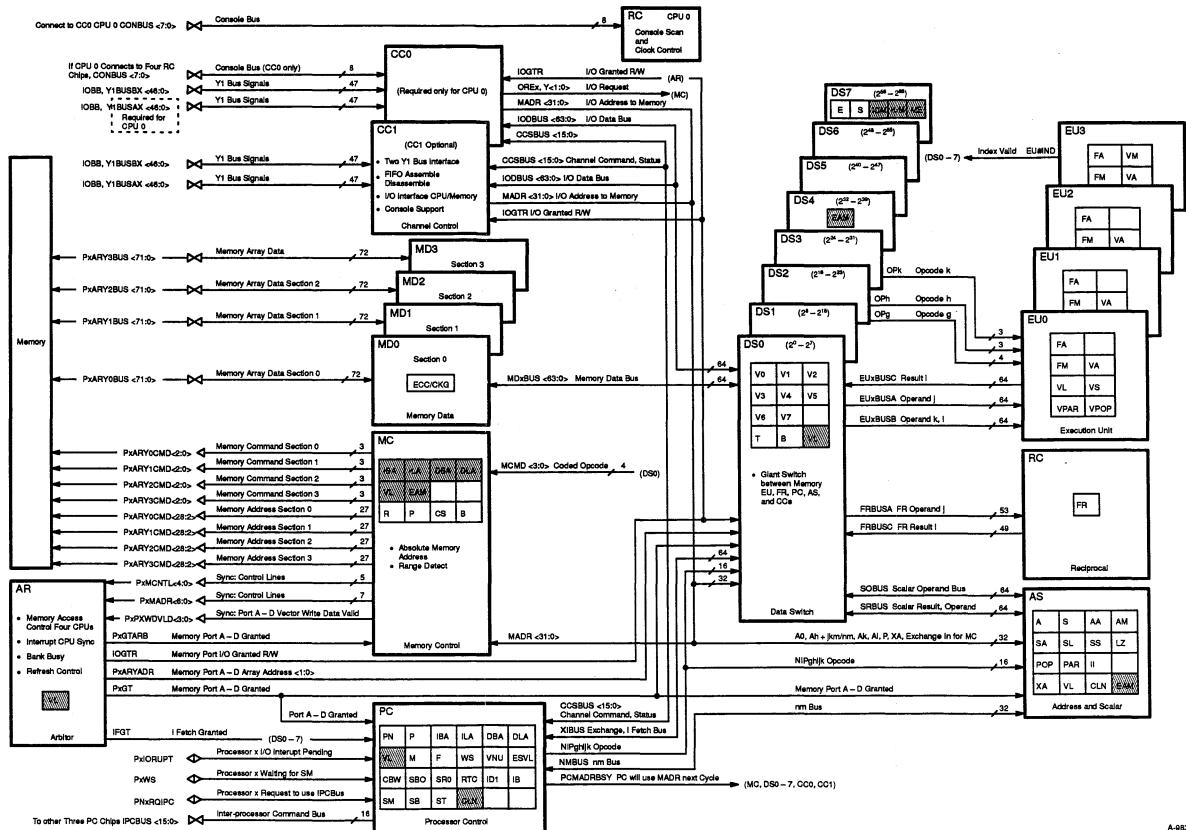

The CPU in the CRAY Y-MP EL computer system is constructed on a single 16 x 22 inch printed circuit (PC) board. This PC board contains all of the logic associated with the CRAY Y-MP EL system CPU. Very large scale integration (VLSI) solid-state technology enables a relatively small PC board to contain an entire CPU.

The VLSI chips used in the CPU are application-specific integrated circuits (ASICs). They are constructed using complementary metal oxide semiconductors (CMOS). The ASICs are available in two package sizes; one has 299 pins and one has 223 pins. The internal construction

of the ASIC forms 100,000 undefined gates. This massive number of gates is contained in a  $2 \times 2$  inch or a  $1.88 \times 1.88$  inch package, which consumes an average of 5 watts at + 5 volts.

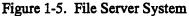

The CPU contains nine ASIC chip types; there are 23 ASIC chips per CPU. Figure 1-6 shows the chip layout for the CPU of the CRAY Y-MP EL system.

The nine types of ASICs that form the CPU are:

- 1 arbiter (AR) ASIC, used for memory access control and for inter-CPU synchronization.

- 1 address and scalar (AS) ASIC, containing the address registers and address functional units and the scalar registers and scalar functional units.

- 2 channel control (CC) ASICs. Each CC supports two Y1 channels, which are the 40 Mbyte/s channels that connect to the VMEbus sybsystem. The CC option is also used for control support.

- 8 data switch (DS) ASICs, which perform the major data steering between memory, channel, and functional units; they contain the vector registers and B/T registers.

- 4 execution unit (EU) ASICs. Each EU contains all of the vector and floating-point functional units, except the floating-point reciprocal. All of these functional units are fully pipelined, but only one functional unit can be active per EU at any one time. Vector mask (VM) operations can only be performed on EU3.

- 1 memory control (MC) ASIC, which provides memory address generation for a maximum of 512 Mwords of memory. The MC also performs operand and program range error detection.

- 4 memory data (MD) ASICs, which perform single-error correction/double-error detection (SECDED<sup>†</sup>) and generate check bits. The MDs also support any memory maintenance instructions.

- 1 processor control (PC) ASIC. This device contains eight 32-word instruction buffers(IB), performs shared register (SR) access control, and supports 7 shared register clusters. Also included are the instruction issue control circuits, including the instruction and functional unit scoreboard, and I/O interrupt handling circuits.

- <sup>†</sup> Hamming, R. W. "Error Detection and Correcting Codes." Bell System Technical Journal. 29.2 (1950): 147–160.

1-7

1 reciprocal and console (RC) ASIC. The RC performs floating-point reciprocal approximations and contains CONBUS interfaces, scan control and clock control hardware, and console registers.

The interconnection of these CPU components is shown by the block diagram in Figure 1-7.

The CRAY Y-MP EL system is designed to contain up to four independent CPUs. However, the four CPUs can work in conjunction by using shared registers. The CPU runs on a 30 nanosecond (ns) clock. Each CPU connects to the system backplane using 1230 signal pins. . .

·

· · ·

CMM-xxx-PR2

Cray Research Proprietary Preliminary Information CRAY Y-MP EL Troubleshooting and Maintenance Manual

Figure 1-7. CRAY Y-MP EL Block Diagram

System Uverview

A-9831

#### Memory Overview

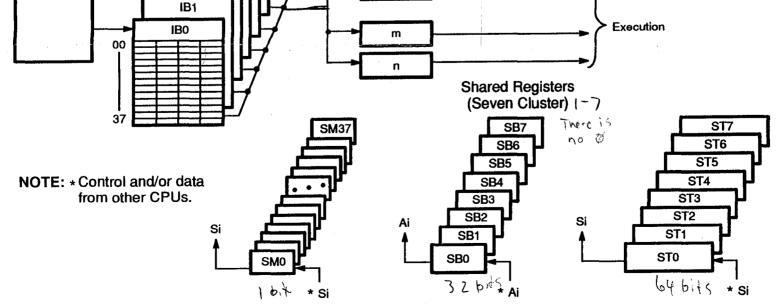

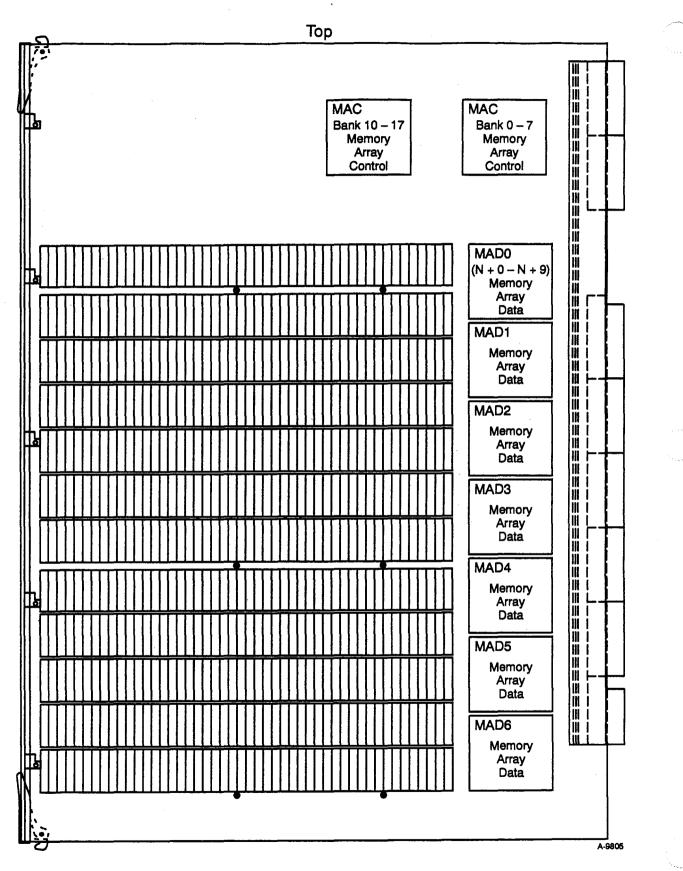

Central memory within the CRAY Y-MP EL system is contained on four PC boards. Each of these boards is 16 x 22 inches (the same size as the CPU board) and is composed of two ASIC types, with a total of nine ASICs per board and a specific number of 1M x 4 dynamic random access memory (DRAM) integrated circuits. The number of DRAMs depends upon the customer's choice of available memory options. The CRAY Y-MP EL system can be ordered with either 64 Mwords or 128 Mwords of central memory. When the 64 Mword option is selected, the memory module contains 16 Mwords of memory supplied by 288 DRAMs. This is a half-populated module. The larger memory, 128 Mwords, consists of 576 DRAMs mounted on each module, creating 32 Mwords per module and 128 Mwords per system. This option uses fully populated modules.

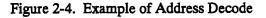

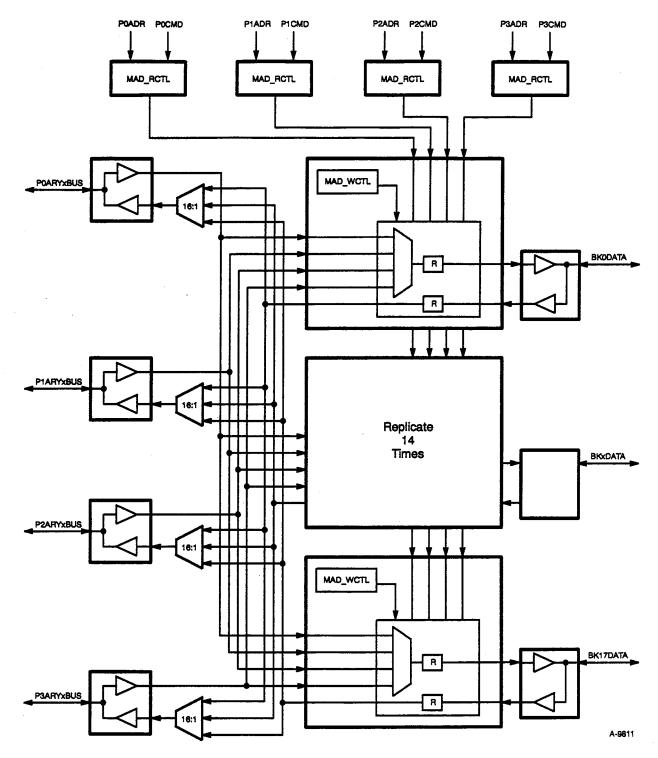

The layout of the memory board is shown in Figure 1-8. The two ASIC types used on the memory board are:

- 2 memory array control (MAC) ASICs support the four memory functions. These ASICs contain an address crossbar which allows access to memory from each of the four CPUs as well as refresh address counters for the local refresh function. The MAC ASIC also contain DRAM address and control circuitry, which provides control to all MADs.

- 7 memory array data (MAD) ASICs. These contain a data crossbar that connects the four CPUs to the 16 banks contained on each memory board. The MAD ASICs handle a portion of the 72-bit memory data word.

The CRAY Y-MP EL system central memory contains a total of 64 banks spread across the four modules. Each module contains 16 banks and is considered a memory section. These 16 banks are separated into lower and upper banks on each board. Thus, a half-populated memory board uses only the lower bank, but still retains the full 16 banks of memory. This means that a fully populated memory module uses both upper and lower banks.

Figure 1-9 shows the chassis locations of the eight boards that form the CRAY Y-MP EL computer system. Note that this represents a top view, with the front of the chassis at the bottom of the diagram.

- 32 mw = hait provised 1 mx4 25 address bits used

- 64 mil = half populated 1 mil 4 26 address bits used

128 mu = fully popularia 1 mil

Figure 1-9. Chassis, Top View

# Input/Output Subsystem Overview

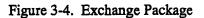

The IOS for the CRAY Y-MP EL system was selected to provide customers with the maximum choice of peripheral equipment. The IOS is a VME-based system that communicates with the CPU via the Y1 bus (a 40-Mbyte/s channel) using a Cray Research, Inc. (CRI) proprietary module, the input/output buffer board (IOBB). The IOBB is the only CRI proprietary board within the IOS. All other functions within the IOS are performed using vendor-supplied VME boards.

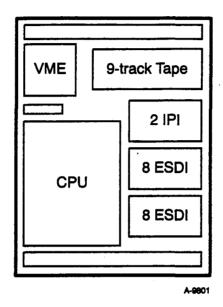

The restrictions of the IOS configuration require use of a 68030-type processor that is capable of processing 32 bits, and as many as eight peripheral controllers to handle data transfers. A possible IOS configuration is represented in Figure 1-10. The types of controllers used are defined by the customer's choice of system peripherals.

Figure 1-10. IOS Configuration

There are several other considerations pertaining to the VMEbus system. The standard VME mechanical chassis is a 19-inch rack mount chassis that is air cooled, supports standard  $64 \times 160 \text{ mm VME}$  boards, and requires a 750-watt power supply. The backplane is a modular design based on a 10-slot system. The backplane configurations include:

- 10-slot, 10-slot option

- 10-slot, 6-slot, 4-slot option

- 6-slot, 4-slot, 6-slot, 4-slot option

$\sum_{i=1}^{n}$

•

$\bigcirc$ • .

•

,

# 2 MEMORY

The memory portion of the CRAY Y-MP EL computer system consists of four modules. These modules currently are provided in two types: a fully populated module and a half populated module. Both module types are constructed on  $16 \times 22 \times .093$  inch printed circuit (PC) boards consisting of 16 circuit layers. These 16 layers are:

- 1 top pad

- 1 bottom pad

- 4 ground (Vss) layers

- 4 power layers: 5-volt application-specific integrated circuit (ASIC); &volt dynamic random access memory (DRAM)

- 6 signal layers

The logic portion of a memory PC board comprises two types of ASICs and a group of DRAM chips. There are nine ASICs on each memory board: two memory array control (MAC) ASICs and seven memory array data (MAD) ASICs. The number of DRAM chips on each memory PC board is determined by the memory size selected by the customer. Currently, the CRAY Y-MP EL system can be supplied with either a 64-Mword memory or a 128-Mword memory.

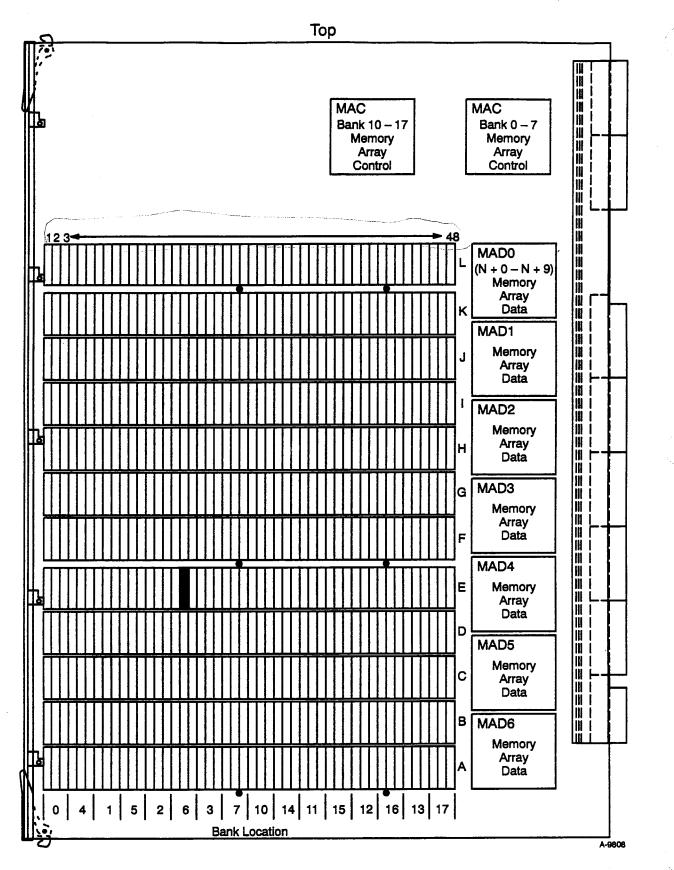

The 64-Mword memory option is a half-populated memory board that contains 288 DRAM chips. Each of these DRAM chips is a  $1M \times 4$ memory chip with a 70 nanosecond (ns) access time. The same DRAM chip is used with the 128-Mword memory, but there are 576 memory chips mounted on the fully populated memory board. Refer to Figure 2-1 for a diagram of a fully populated memory module.

Figure 2-1. Memory Module

Memory is divided into 16-banks for addressing whether the module is half populated or fully populated. The fully populated module contains an upper 16 banks and a lower 16 banks of addressable memory; the half populated module uses only the lower 16 banks. There are 16 banks of memory on each memory module, providing the mainframe with a total of 64 banks of memory. The memory is also separated into sections; each memory module is one section. This arrangement provides the mainframe with four memory sections, each consisting of 16 banks.

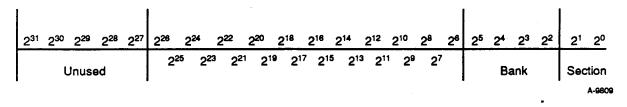

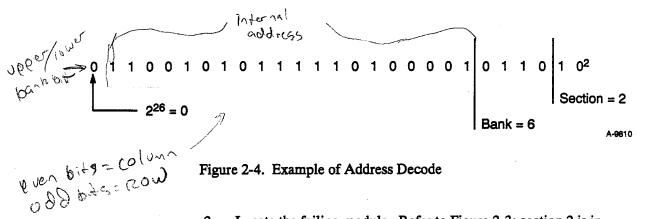

The addressing method used by the CRAY Y-MP EL system is a 32-bit address scheme, of which 27 bits (0 through 26) are used. The bits are assigned as shown in Figure 2-2. Bits  $2^0$  and  $2^1$  are used to select the appropriate section and bits  $2^2$  through  $2^5$  are used for bank selection.

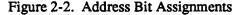

The remainder of the address bits, with one exception, are used to select the actual memory location. The exception is bit  $2^{26}$ , which is used as the upper/lower bank select bit. This bit is only necessary on a fully populated 128-Mword memory module. The internal addressing scheme, represented by bits  $2^{6}$  through  $2^{25}$ , uses a row and column scheme. The odd numbered bits are used to count the rows of memory, while the even numbered bits are used to locate the column. It is possible to determine the exact DRAM chip that contains a failing bit by first decoding bits  $2^{0}$ and  $2^{1}$  to determine which section is in error. This corresponds to a specific memory module. The locations of the memory sections is shown in Figure 2-3, which is a representation of the eight-slot mainframe card cage. All of the memory modules are interchangeable, so swapping the suspected failing module with a good module can help isolate the failure.

\* The CPU slots are double wide to accomodate paddle boards.

A-9813

#### Figure 2-3. Mainframe Chassis, Front View

The next step in the failure isolation procedure is to decode bits  $2^2$  through  $2^5$  from the failing address. Once the failing bank has been identified, use Figure 2-1 to identify the location of the failing bank on the PC board. Next, locate the failing data bit in the center section of Table 2-1 as well as the column representing the failing bank. The bank selection will partially depend on the condition of address bit  $2^{26}$ . If  $2^{26}$  is zero, the failing bank is located to the right of center. When  $2^{26}$  is one, the failing bank is located to the left of center. Once the two starting coordinates have been located, draw lines to the left or right from the failing data bit and down under the failing bank. The point at which these two lines intersect represents the board coordinates of the failing chip.

In Figure 2-1, representing the actual PC board, it is possible to locate the chip that requires replacement. In this figure, note that at the right side of the chip locations are labeled positions A through L, moving bottom to top. Along the top, the chips are numbered left to right from 1 to 48. Finally, along the bottom of the chips, the bank locations are indicated. Each bank contains three chips in each of the rows A through L, and the banks are **not** numbered consecutively. Using these locator coordinates, apply the board coordinate determined on Table 2-1, and the physical location of the failing chip is defined.

As an example, if data bit  $2^{43}$  is reported as failing with an address of 312764132<sub>8</sub>, locate the failing DRAM chip.

Cray Research Proprietary Preliminary Information

continued pg 2-6

Table 2-1. DRAM Locator Chart

|         |         |         |         |         |         | в       | aniks H              | A26      | = 1       |          |          |          |          |              |          |          | DR       | AM       |            |        | •      |          |         |        |                | Banks L A26 = 0 |         |         |         |          |          |          |          |          |         |   |

|---------|---------|---------|---------|---------|---------|---------|----------------------|----------|-----------|----------|----------|----------|----------|--------------|----------|----------|----------|----------|------------|--------|--------|----------|---------|--------|----------------|-----------------|---------|---------|---------|----------|----------|----------|----------|----------|---------|---|

| 17      | 16      | 15      | 14      | 13      | 12      | 11      | 10                   | 7        | 6         | 5        | 4        | 3        | 2        | 1            | 0        |          | 1M x 4   |          |            |        | 1      | 2        | 3       | 4      | 5              | 6               | 7       | 10      | 11      | 12       | 13       | 14       | 15       | 18       | 17      |   |

| L       | L       | L       | ٤       | L       | L       | L       | L                    | L        | L         | L        | L        | L        | L        | L            | L        | 0        | 9        | 23       | 28         | к      | к      | к        | к       | к      | к              | к               | ĸ       | к       | к       | к        | к        | к        | к        | к        | к       |   |

| 46      | 40      | 34      | 28      | 43      | 37      | 31      | 25                   | 22       | 18        | 10       | 4        | 19       | 13       | 7            | 1        |          | Ľ        | ~~~      |            | 1      | 7      | 13       | 19      | 4      | 10             | 16              | 22      | 25      | 31      | 37       | 43       | 28       | 34       | 40       | 46      |   |

| L       | L       | L       | L       | L       | L       | L       | L                    | L        | L         | L        | L        | L        | L        | L            | L        | 1        | 10       | 21       | 30         | ĸ      | ĸ      | к        | ĸ       | К      | K              | к               | к       | к       | к       | ĸ        | к        | к        | к        | к        | к       |   |

| 47<br>L | 41      | 35      | 29      | 44      | 38      | 32      | 26                   | 23       | 17        | 11       | 5<br>L   | 20<br>L  | 14<br>L  | 8            | 2        |          |          | ļ        |            | 2      | 8<br>K | 14<br>K  | 20<br>K | 5<br>K | <u>11</u><br>К | 17<br>K         | 23      | 26<br>K | 32      | 38       | 44<br>K  | 29<br>K  | 35       | 41       | 47      |   |

| L<br>48 | L<br>42 | L<br>36 | L<br>30 | L<br>45 | L<br>39 | L<br>33 | L<br>27              | L<br>24  | L<br>18   | L<br>12  | 6        | 21       | 15       | L<br>  9     | L<br>3   | 2        | 11       | 22       | 31         | к<br>3 | 9      | 15       | 21      | 6      | 12             | 18              | К<br>24 | 27      | К<br>33 | К<br>39  | 45       | 30       | К<br>36  | К<br>42  | К<br>48 |   |

| J       | <br>J   | 2       |         | 1       | 7       | J       |                      | <u> </u> | <u>,,</u> | <u> </u> | Ĵ        | <u> </u> | J        | J            | J        |          |          |          |            |        |        | <u> </u> | 1       |        |                | 1               |         |         | -       | -        |          |          | 1        |          |         | 1 |

| 46      | 40      | 34      | 28      | 43      | 37      | 31      | 25                   | 22       | 16        | 7        | 4        | 19       | 13       | 7            | 1        | 3        | 8        | 20       | 29         | 1      | 7      | 13       | 19      | 4      | 10             | 16              | 22      | 25      | 31      | 37       | 43       | 28       | 34       | 40       | 46      |   |

| J       | J       | J       | J       | J       | J       | J       | J                    | J        | J         | J        | J        | J        | J        | J            | J        | 4        | 13       | 19       | 24         | 1      | 1      | 1        | 1       | I      | 1              | 1               | 1       | 1       | 1       | 1        | 1        |          | T        | 1        | 1       |   |

| 47      | 41      | 35      | 29      | 44      | 38      | 32      | 26                   | 23       | 17        | 8        | 5        | 20       | 14       | 8            | 2        |          | 15       | 19       | 24         | 2      | 8      | 14       | 20      | 5      | 11             | 17              | 23      | 26      | 32      | 38       | 44       | 29       | 35       | 41       | 47      |   |

| J       | J       | J       | J       | J       | J       | J       | J                    | J        | J         | J        | J        | J        | J        | J            | J        | 5        | 14       | 17       | 26         | 1      | 1      | 1        | 1       | I      | I              | I               | 1       | 1       | T       | 1        | 1        | 1        | 1        | 1        | 1       |   |

| 48      | 42      | 36      | 30      | 45      | 39      | 33      | 27                   | 24       | 18        | 9        | 6        | 21       | 15       | 9            | 3        | Ĺ        |          |          |            | 3      | 9      | 15       | 21      | 6      | 12             | 18              | 24      | 27      | 33      | 39       | 45       | 30       | 36       | 42       | 48      |   |

| H       | H       | H       | H       | H       | H       | н       | H<br>25              | н<br>22  | H         | н<br>10  | H<br>4   | н<br>19  | н<br>13  | H<br>7       | H<br>  1 | 6        | 15       | 18       | 27         | G      | G<br>7 | G<br>13  | G<br>19 | G      | G<br>10        | G<br>16         | G<br>22 | G<br>25 | G<br>31 | G<br>37  | G        | G.<br>28 | G<br>34  | G<br>40  | G       |   |

| 46<br>H | 40<br>H | 34<br>H | 28<br>H | 49<br>H | 37<br>H | 31<br>H | <del>20</del><br>  H | н        | 16<br>H   | Н        | H        | H        | <u>н</u> | <del>H</del> | H        |          |          |          |            |        | G      | G        | G       | 4<br>G | G              | G               | 22<br>G | 25<br>G | G       | 3/<br>G  | 43<br>G  | 20<br>G  | G        | G        | 46<br>G |   |

| 47      | 41      | 35      | 29      | 44      | 38      | 32      | 26                   | 23       | 17        | 11       | 5        | 20       | 14       | 8            | 2        | 7        | 12       | 16       | 25         | 2      | 8      | 14       | 20      | 5      | 11             | 17              | 23      | 26      | 32      | 38       | 44       | 29       | 35       | 41       | 47      |   |

| н       | H       | н       | н       | н       | н       | н       | н                    | н        | H         | н        | H        | н        | н        | H            | н        |          |          |          | 00         | G      | G      | G        | G       | G      | G              | G               | G       | G       | G       | G        | G        | G        | G        | G        | G       |   |

| 48      | 42      | 36      | 30      | 45      | 39      | 33      | 27                   | 24       | 18        | 12       | 8        | 21       | 15       | 9            | 3        | 32       | 41       | 55       | 60         | 3      | 9      | 15       | 21      | 6      | 12             | 18              | 24      | 27      | 33      | 39       | 45       | 30       | 36       | 42       | 48      |   |

| F       | F       | F       | F       | F       | F       | F       | F                    | F        | F         | F        | F        | F        | F        | F            | F        | 33       | 42       | 53       | 62         | E      | Ε      | E        | E       | Ε      | E              | E               | E       | E       | E       | E        | ε        | E        | E        | E        | Ε       |   |

| 46      | 40      | 34      | 28      | 43      | 37      | 31      | 25                   | 22       | 16        | 10       | 4        | 19       | 13       | 7            | 1        |          |          | ~        |            | 1      | 7      | 13       | 19      | 4      | 10             | 16              | 22      | 25      | 31      | 37       | 43       | 28       | 34       | 40       | 46      |   |

| F       | F       | F       | F       | F       | F       | F       | F                    | F        | F         | F        | F        | F        | F        | F            | F        | 34       | 43       | 54       | 54 63      | 63     | E      | E        | E       | E      | ε              | ε               | / E \   | E       | E       | E        | E        | E        | E        | E        | Ε       | E |

| 47      | 41      | 35      | 29      | 44      | 38      | 32      | 26                   | 23       | 17        | 11       | 5        | 20       | 14       | 8            | 2        |          |          |          |            | 2      | 8      | 14       | 20      | 5      | 11             | 17              | 23      | 26      | 32      | 38       | 44       | 29       | 35       | 41       | 47      |   |

| F       | F       | F       | F       | F       | F       | F       | F                    | F        | F         | F        | F        | F        | F        | F            | F        | 35       | 40       | 52       | 61         | E      | E      | E        | E       | E      | E              | Ē               | E       | E<br>27 | E       | E        | E        | E        | E        | E        | E       |   |

| 48      | 42<br>D | 36<br>D | 30<br>D | 45<br>D | 39<br>D | 33<br>D | 27<br>D              | 24<br>D  | 18<br>D   | 12<br>D  | 6<br>D   | 21<br>D  | 15<br>D  | 9<br>D       | D        |          |          |          |            | 3<br>C | 9<br>C | 15<br>C  | 21<br>C | 6<br>C | 12<br>C        | 18<br>C         | 24<br>C | 2/<br>C | 33<br>C | 39<br>C  | 45<br>C  | 30<br>C  | 36<br>C  | 42<br>C  | 48<br>C |   |

| D<br>46 | 40      | 34      | 28      | 43      | 37      | 31      | 25                   | 22       | -         | 10       | 4        | 19       | 13       | 7            | 1        | 36       | 45       | 51       | 56         |        | 7      | 13       | 19      | 4      | 10             | 16              | 22      | 25      | 31      | 37       | 43       | 28       | 34       | 40       | 48      |   |

| D       | D       | D       | D       | D       | D       | D       |                      |          | D         | D        | D        | D        | D        | D            | D        |          |          |          |            | c      | c      | c        | c       | c      | C              | C               | c       | C       | C       | C        | c        | c        | c        | c        | c       |   |

| 47      | 41      | 35      | 29      | 44      | 38      | 32      | 26                   | 23       | 17        | 11       | 5        | 20       | 14       | 8            | 2        | 37       | 46       | 49       | 58         | 2      | 8      | 14       | 20      | 5      | 11             | 17              | 23      | 26      | 32      | 38       | 44       | 29       | 35       | 41       | 47      |   |

| D       | D       | D       | D       | D       | D       | D       | D                    | D        | D         | D        | D        | D        | D        | D            | D        | 38       | 47       | 50       | 59         | C      | C      | C        | C       | C      | C              | С               | С       | С       | C       | С        | C        | C        | C        | С        | c       |   |

| 48      | 42      | 36      | 30      | 45      | 39      | 33      | 27                   | 24       | 18        | 12       | 6        | 21       | 15       | 9            | 3        | 30       | <u> </u> | <u> </u> | 39         | 3      | 9      | 15       | 21      | 6      | 12             | 18              | 24      | 27      | 33      | 39       | 45       | 30       | 36       | 42       | 48      |   |

| В       | в       | В       | В       | В       | В       | B       | В                    | B        | В         | B        | 8        | В        | В        | В            | В        | 39       | 44       | 48       | 57         | A      | •      | •        | •       | •      | A              | •               | ۸       | •       | ^       | •        | A        | •        | A        | •        | ^       |   |

| 46      | 40      | 34      | 28      | 43      | 37      | 31      | 25                   | 22       |           | 10       | 4        | 19       | 13       | 7            | 1        | L        | ļ        | <u> </u> | L <u>.</u> | 1      | 7      | 13       | 19      | 4      | 10             | 16              | 22      | 25      | 31      | 37       | 43       | 28       | 34       | 40       | 46      |   |

| В       | 8       | В       | В       | B       | B       | B       | B                    | B        | B         | B        | B        | B        | B        | B            | B        | 64       | 66       | 68       | 70         |        |        |          | A       |        | A              | <b>A</b>        | A       | A       | A       | <b>A</b> | <b>A</b> | <b>A</b> | <b>A</b> | <b>A</b> | A       |   |

| 47      | 41      | 35      | 29      | 44      | 38      | 32      |                      | 23       |           | 11       | 5        | 20       | 14       | 8            | 2        | <u> </u> | ļ        | <b> </b> | <b> </b>   | 2      | 8      | 14       | 20      | 5      | 11             | 17              | 23      | 26      | 32      | 38       | 44       | 29       | 35       | 41       | 47      |   |

| B<br>48 | B<br>42 | B<br>36 | B<br>30 | B<br>45 | B<br>39 | B<br>33 | B<br>27              | B<br>24  | B         | B<br>12  | B<br>  6 | 8<br>21  | B<br>15  | B<br>  9     | B<br>3   | 65       | 67       | 69       | 71         | 3      | A<br>9 | A<br>15  | A<br>21 | 6      | A<br>12        | A<br>18         | A<br>24 | A<br>27 | A<br>33 | A<br>39  | A<br>45  | 30       | A<br>36  | A<br>42  | A<br>48 |   |

CMM-xxx-PR2

Cray Research Proprietary Preliminary Information

Memory

CRAY Y-MP EL Troubleshooting and Maintenance Manual

ი ს 1. Decode the address. Refer to Figure 2-4.

The reported error is in section 2, lower bank 6.

- Locate the failing module. Refer to Figure 2-3; section 2 is in 2. slot 6.

- Using Table 2-1, locate data bit 2<sup>43</sup> in the center section and lower 3. bank 6 in the top row. Draw lines to the right from bit  $2^{43}$  and down from bank 6. These two lines should intersect at a point labeled E17.

- 4. Using Figure 2-1, locate point E17. To the right of the DRAM chips, locate row E. From the left end of row E, count to the seventeenth DRAM chip (shaded on the diagram). To check, follow column 17 down and verify that the failing chip is in bank 6.

Because the DRAM chip used in the CRAY Y-MP EL system memory is a 1M x 4 chip, it is expected that a single-bit error will rapidly escalate into a multiple-bit error. For this reason, it is important to repair single-bit errors as soon as possible.

Other specifications pertaining to the DRAM chip are:

- ZIP package .4 x 1.03 inch

- 5 clock period bank access time

- Standby power = 5 milliwatts at 5 volts

- Active power = 550 milliwatts at 5 volts

The rest of the memory PC board is made up of two types of MAC and MAD ASICs. The MAC ASIC chip supports four memory operations:

- Read, a normal DRAM read operation, lasts 5 clock periods.

- Write, a normal DRAM write operation, lasts 5 clock periods.

- Refresh, which uses row address strobe (RAS) to refresh data, lasts 5 clock periods.

- Read/Modify/Write (RMW) is used during an exchange, and uses normal DRAM read operations followed by a normal DRAM write operation to the same address. RMW lasts 10 clock periods.

The refresh control for the DRAM chips is located on the CPU and memory PC boards.

Other functions of the MAC ASIC include:

- Connects any of the four processors to any of the 16 banks through an address crossbar

- Controls both address and control signals

- Holds a refresh address counter

- Controls all of the MAD ASICs

The MAD ASICs perform the following functions:

- Each handles a specific portion of the 72-bit memory data word

- Each contains a data crossbar which connects any of the four processors to any of the 16 banks

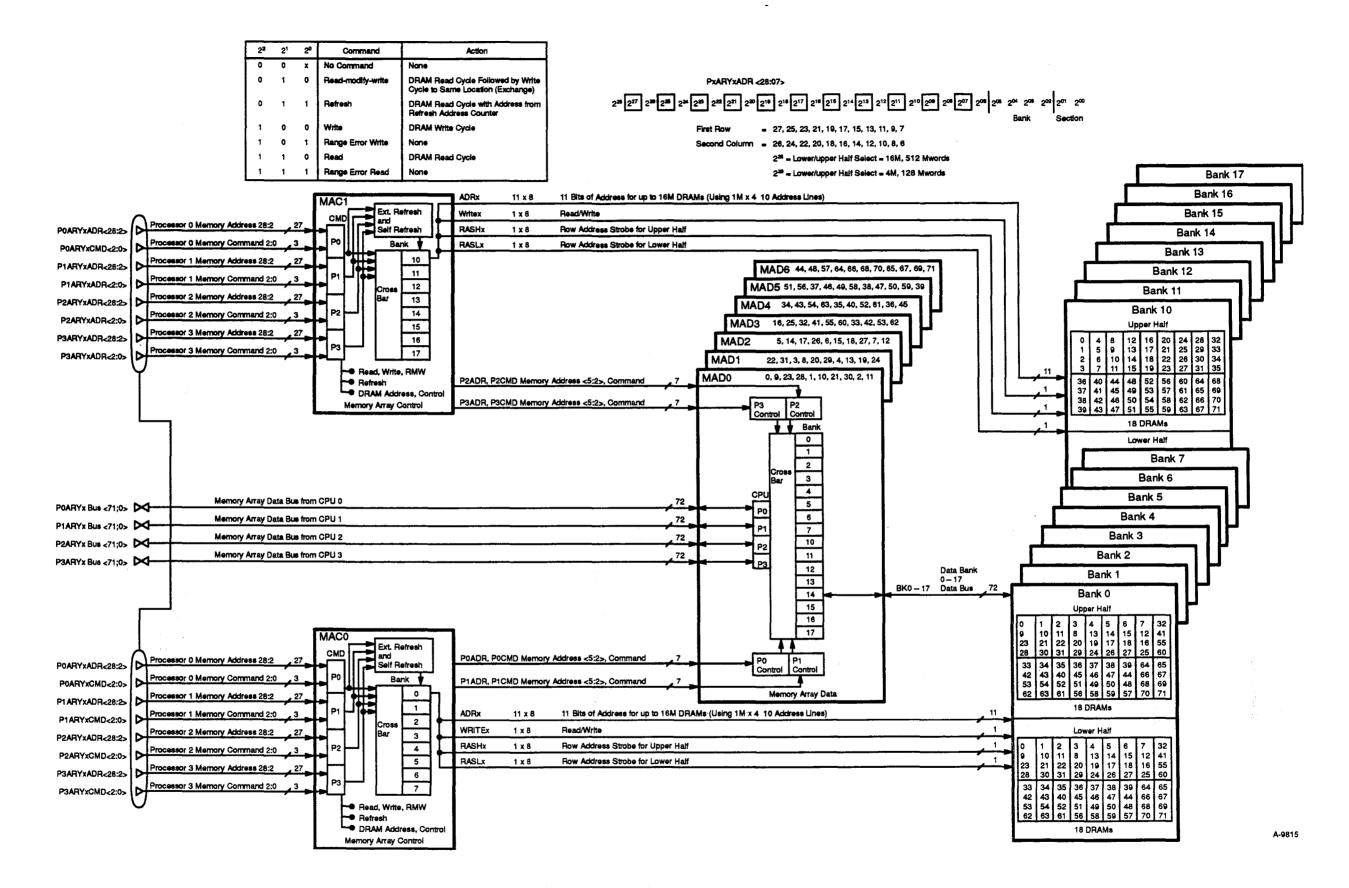

The interconnection between the MAD, MAC, and DRAM chips is represented in Figure 2-5. Note that MAC 0 controls operations for banks 0 through 7, and MAC 1 controls banks 10 through 17. The content of the entire data bus is presented to the seven MAD ASICs and each receives its assigned bits. The bits assigned to each MAD ASIC are in no specific order. If a group of 10 or 11 bits of data are reported as failing, it could in fact be a single MAD that is failing. Included in this section are Figure 2-6, the internal block diagram of a MAD ASIC, and Figure 2-7, the internal block diagram of the MAC ASIC, indicate how an ASIC is designed. When an ASIC fails, the failing chip is removed from the PC board, discarded, and replaced by a new ASIC. No internal repairs are possible.

Other important characteristics of CRAY Y-MP EL system memory modules are:

- Each memory module contains 16 Mwords of memory if half populated and 32 Mwords if fully populated

- Operates with a 30 ns clock period

- Air cooled

- Connected to the backplane by two types of connectors:

120 pins  $\times$  7 connectors = 840 pins 90 pins  $\times$  1 connector = 90 pins 930 pins

- Connected to the individual CPUs using one port per CPU; all ports are read/write ports

- There is no hardware error logger. Single and double bit errors are reported to the operating system by bits being set within the exchange package.

- 270 watts per module = 1080 watts per system

- Voltage = + volts 5

Figure 2-5. Memory Block Diagram

Figure 2-6. Memory Array Data Block Diagram

Figure 2-7. Memory Array Control Block Diagram

$\bigcirc$

C .

The CRAY Y-MP EL computer system central processing unit (CPU) is a single printed circuit (PC) board module that contains all the registers and functional units normally used in a computer mainframe. This miniturization is made possible by using very large-scale integration (VLSI) complimentary metal oxide semiconductive (CMOS) application-specific integrated circuits (ASICs). Twenty-three of these ASICs are mounted on a single  $16 \times 22 \times .093$  inch PC board.

The CMOS ASICs are provided in two sizes, both 1-micron, two-layer devices with 100,000 undefined gates:

- 2.08 x 2.08 inch chip with 299 pins

- 1.88 x 1.88 inch chip with 233 pins

The power consumed by these chips averages less than 5 watts per ASIC, operating at +  $\frac{6}{2}$  volts.

The PC board used to form the CPU module is manufactured of 16 separate layers:

- 1 top pad

- 1 bottom pad

- 4 ground (Vss) layers

- 4 power (Vdd) layers

- 6 signal layers

This module uses an average of 160 watts of power per CPU module. Therefore, the maximum of four CPU modules in a system consumes 640 watts. The CPU, like the entire CRAY Y-MP EL system, is an air cooled device.

The following nine types of ASIC chips reside on the CPU module:

- 1 arbiter (AR) ASIC controls memory access and arbitrates all memory conflicts. It also provides inter-CPU synchronization.

- 1 address and scalar (AS) ASIC contains all of the address registers and the address functional units (FUs), as well as the scalar (S) registers and scalar FUs.

- 2 channel control (CC) ASICs control or support the functions of two Y1 channels. Each of the Y1 channels is capable of 40-Mbyte/s transfers and each connects to a VME subsystem. It is also possible to use two Y1 channels in conjunction to provide one-high performance parallel interface (HHPPI) channel for 100-Mbyte/s transfers). One other function of the CC chip is console support.

- 8 data switch (DS) ASICs steer data between memory, the selected channel, and the required FUs.

- 4 execution unit (EU) ASICs contain all of the vector and floating-point FUs, with the exception of the floating-point reciprocal FU. This format provides full pipelining to the EU chips and allows each to work on a different problem independently of the others. The restrictions which pertain to the EU chips are:

- Only one FU in each EU chip can be operating at any one time

- Only the EU3 ASIC is capable of executing vector mask (VM) instructions (146 147, 175 instructions)

- 1 memory control (MC) ASIC provides address generation, which can support up to 512 Mwords of memory. The other function of the MC chip is to provide both operand and program range error detection.

- 4 memory data (MD) ASICs perform single-error correction, double-error detection (SECDED) functions, including check bit generation on the read and write memory data. The MD chips are also used to support all of the memory maintenance instructions.

- 1 processor control (PC) ASIC contains the CPU instruction buffers. The CRAY Y-MP EL system CPU uses eight instruction buffers, each of which is 32 words wide. Instruction issue control and I/O interrupt handling control also reside on the PC chip. Part of the issue control function is a resource scoreboard, also resident on the PC. Shared register access control is also performed on the PC ASIC; the CRAY Y-MP EL system supports seven shared register clusters.

- 1 reciprocal and control (RC) ASIC contains the floating-point reciprocal FU, the CONBUS interfaces, the scan and clock control, and the control registers.

These units interconnect in the way shown on the the CRAY Y-MP EL system block diagram, Figure 3-1. A more specific diagram showing some of the signal paths can be found in Figure 3-2, a block diagram of the CPU bus. This diagram also shows the internal contents of each of the ASICs located on the CPU module. Another diagram of interest is shown in Figure 3-3, which shows the actual location of the various ASICs.

. .

•

•

CMM-xxxx-PR2

Cray Research Proprietary Preliminary Information CRAY Y-MP EL Troubleshooting and Maintenance Manual

Figure 3-1. CRAY Y-MP EL Block Diagram

CF2

Figure 3-2. CPU Bus Block Diagram

A-9830

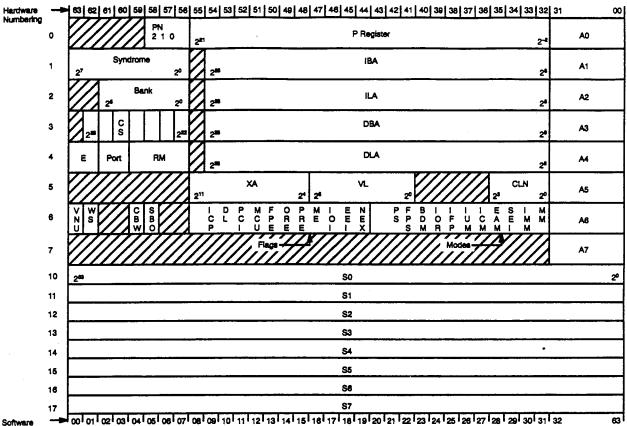

The representative diagram of the exchange package used in the CRAY Y-MP EL system, shown in Figure 3-4, is useful for troubleshooting. The exchange package may contain pertinent information about the state of the CPU at the point of failure. This information can be extracted by comparing the condition of the flag bits, mode bits, and the error word bits with the respective charts shown under the exchange package in Figure 3-4. In some cases, useful information can also be found in the A registers or the S registers, also shown in Figure 3-4. The usefulness of the A or S register information depends on the individual diagnostic used.

The CRAY Y-MP EL system supports one to four CPUs. Each of these CPUs can support up to four VME subsystems. The CPU module is completely self contained and plugs into the mainframe backplane using 11 connectors that provide 1230 signal pins.

When a CPU is indicated as the faulty unit in an incident, the only on-site repair performed is the replacement of the CPU module.

The CPU module connects to the mainframe memory via four 72-bit bidirectional ports. Each of these ports connects to a separate memory section. Each of the CPU modules in a CRAY Y-MP EL system contain a copy of all memory and shared register reservations, to reduce the possibility of conflicts. Each CPU has to check its local request registers, not the request registers of all of the CPUs.

Support for multiple CPUs in the mainframe includes such items as:

- Shared memory

- Shared registers

- Shared I/O channels

- Deadlock detection

- Shared deadstart paths

However, the CRAY Y-MP EL system does not currently support:

- Performance monitors

- High-speed (HISP) channels

- Very high-speed (VHISP) channels

Software Numbering

| Word 6 |          | Flag Bits                                | Set Flag    | Cause<br>Exchange | v           | E - Error Word 4 |                                                 |    |    |         |                            |            |                  |               |                 |   |          |                 |

|--------|----------|------------------------------------------|-------------|-------------------|-------------|------------------|-------------------------------------------------|----|----|---------|----------------------------|------------|------------------|---------------|-----------------|---|----------|-----------------|

| 56     | Reserved |                                          |             | 83                | VNU         | Vectors Not Used |                                                 | 33 | U  |         | Uncorrectable Memory Error |            |                  |               |                 |   |          |                 |

| 54     | ЮР       | Interrupt from Internal                  | мм          | мм"               | 62          | ws               | Waiting on Semaphores                           | lĿ | 32 | С       |                            | c          | t M              | иеттогу Егтог |                 |   |          |                 |

| 53     | DL       | CPU<br>Deadlock Interrupt                | MM' and IMM | MM" and IMM       | 59          | CBW              | Concurrent block Write<br>(CRAY Y-MP EL only)   |    |    | P- Port |                            |            |                  |               | RM<br>Read Mode |   |          | Port            |

| 52     | PCI      | Programmable Clock<br>Interrupt (staged) | мм          | мм                | 58          | SBO              | Scalar and block Overlap<br>(CRAY Y-MP EL only) |    | 36 |         | 6                          | 6 6<br>1 0 |                  |               | 55              |   | 55<br>76 | Usage           |

| 51     | мси      | MCU Interrupt                            | MM          | MM"               | 43          |                  | Reserved                                        |    |    | в       |                            | c          | D                |               |                 |   |          | Exchange        |

| 50     | FPE      | Floating-point Error                     | MM and IMM  | MM and IMM        | 42          | PS               | Program State                                   |    | 0  | 0 1     | +                          | 10         | 1.               | +             | 0 0             | - | 01       |                 |

|        |          | Interrupt                                |             |                   | 41          | FPS              | Floating-point Status                           |    | 0  | 0 1     |                            | 1 0        |                  | -             | 0 0             |   | 10       | AorS            |

| 49     | ORE      | Operand Range Error<br>Interrupt         | MM' and IMM | MM" and IMM       | 40          | BDM              | Bidirectional Memory                            | .  | •  |         |                            | • -        | D <sub>x</sub> , |               | 0 1             |   | 01       | 1/O Single      |

| 48     | PRE      | Program Range Error<br>Interrupt         | MM' and IMM | MM' and IMM       | 39          | IOR              | Interrupt Operand Range<br>Error                | •  | -  |         |                            | ••         | D<br>x,          | T             | 0 1             |   | 11       | 1/O Block       |

| 47     | ME       | Memory Error Interrupt                   | Always      | Always            | 38          | ifP              | Interrupt Floating-point<br>Error               | 1  | 0  | 0 1     |                            | 10         |                  | •             | 10              |   | 0 0      | BorT            |

| 48     | 101      | I/O Interrupt (staged)                   | MM"         | MM'               | 37          | IUM              | Interrupt Uncorrectable                         |    |    |         | 1                          |            | Þ                | ╈             | 1 0             |   | 11       | Fetch           |

| 45     | EEI      | Error Edit interrupt                     | MM' and IMM | Always            | <b> </b>  " |                  | Memory                                          |    | _  |         | ┥                          |            | <u>  x.</u>      | 4             |                 | _ |          |                 |

| 44     | NEX      | Normai Edit Interrupt                    | MM'         | Always            | 36          | ЮМ               | Interrupt Correctable                           | Ľ  | 0  | 0 1     | 4                          | 10         | <u> </u>         | -             | 11              |   | 0 0      | Vector Stride   |

|        | <u></u>  |                                          |             |                   | 35          | EAM              | Memory<br>Extended Address Mode<br>(32-bit)     | Ľ  | 0  | 0 1     |                            | 10         |                  | •             | 1 1             |   | 10       | V Gather/Scatte |

|        |          |                                          |             |                   | 34          | SEJ              | Selected External<br>Interrupt                  |    |    |         |                            |            |                  |               |                 |   |          |                 |

|        |          |                                          |             |                   | 33          | IMM              | Interrupt Monitor Mode                          |    |    |         |                            |            |                  |               |                 |   |          |                 |

|        |          |                                          |             | 32                | ММ          | Monitor Mode     |                                                 |    |    |         |                            |            |                  |               |                 |   | A-9829   |                 |

A-9829

$\bigcirc$

O

•

C).

# INPUT/OUTPUT SUBSYSTEM

The input/output subsection (IOS) of the CRAY Y-MP EL computer system is designed to act as a preprocessor and interface between the mainframe section [central processing unit (CPU) and memory] and the various customer-selected peripheral devices. The purpose of this section is to describe devices incorporated within the IOS as well as their functions.

### **Basic Architecture**

The IOS used in the CRAY Y-MP EL system is a VMEbus-based device. This VME is a modular design, and thus is easily adapted to customer requirements. The IOS is available in three different backplane configurations:

- 10-slot + 10-slot

- 10-slot + 6-slot + 4-slot

- 6-slot + 4-slot + 6-slot + 4-slot

Cray Research, Inc. (CRI) uses a VME backplane that supports the double-height 233 mm (6U) x 160 mm printed circuit (PC) board, which fits into a standard 19-inch rack. The IOS is powered by a 1000-watt power supply and is air cooled.

The CRAY Y-MP EL system can support up to four independent IOSs for each installed CPU. Thus, a fully enhanced system containing four CPUs can support 16 IOSs. Each of the IOSs communicates with its associated CPU via a 40-Mbyte/s channel, designated the Y1 bus.

IOS 0 is required and must reside in the primary cabinet. This primary IOS, designated the multiplex input/output processor (MIOP), consists of:

- Type 68030-processor based processor board

- Local memory

- Control store

The primary IOS also includes the following devices that are connected to the small computer system interface (SCSI):

- Winchester disk drive

- Cartridge tape drive (.25-inch)

- Communications port for the operators console

- Remote diagnostic facility

- Optional helical-scan tape system

Many peripheral products can be connected to an IOS. Some of these are:

- Networks using TCP/IP

- HYPERchannel

- Fiber-distributed data interface (FDDI)

- Ethernet

- Several varieties of disk drives

- Several varieties of tape drives

For a more detailed list of peripherals supported by the IOS, refer to Section 5 of this manual.

Each of these devices must be driven by a VMEbus-compatible device controller. Cray Research recommends and supports several of these controllers, but the customer may provide other controllers. The IOS backplane can contain up to 8 of these peripheral controllers (in the 10-slot configuration). However, each IOS must contain an I/O processor (IOP) board and a CPU channel communications interface board.

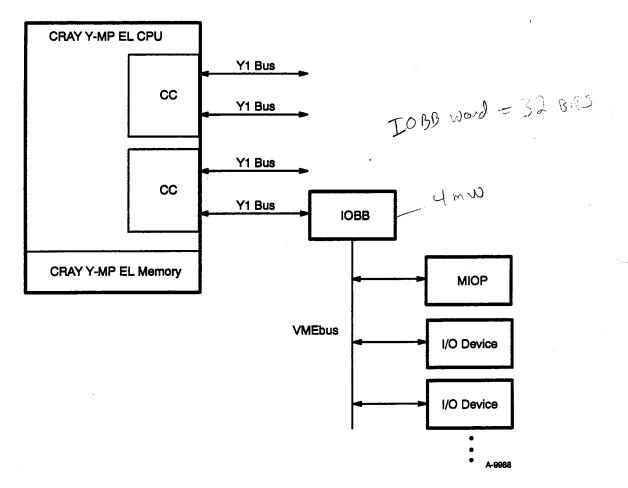

The IOP selected for the CRAY Y-MP EL system IOS is a type 68030-based board supplied by Heurikon Corporation. This IOP supports the SCSI, allows I/O computation, and controls IOS-to-CPU communications. Communication between the IOS and CPU takes place via a CRI board called the input/output buffer board (IOBB).

#### **IOBB**

The IOBB is used to provide buffer memory for the IOP and a communications interface between the IOS and the CPU. IOS-to-CPU communication takes place in the following manner: the IOP generates interrupts to initiate a CPU request, and the CPU generates interrupts to initiate a peripheral read or write operation or to terminate the CPU request. These interrupts are called I/O task control blocks (IOTCB), of which there are two types: I/O IOTCB and console IOTCB. Both of these types have the same format with minor variations (refer to Appendix B).

Once a channel interrupt has been received, the IOP initiates an IOTCB, sends an IOTCB pending interrupt to the CC application-specific integrated circuit (ASIC) on the CPU, and waits for the CPU to acknowledge the interrupt. When the interrupt is received by the CPU, it is handled by the CC ASIC, which acts as the IOTCB processor within the CC ASIC. Refer to Appendix B for illustrations and descriptions of the channel transfer sequences.

The IOBB also detects and reports errors. The Y1 bus enables parity transfers between the CPU and IOBB. The IOBB can thus detect and report parity errors, of which there are two types: errors during IOTCB fetch and errors during IOTCB execution. If a parity error occurs during the IOTCB fetch operation, the CC ASIC is not allowed to execute the IOTCB.

Errors that occur during IOTCB execution can also be of two types: command channel errors or data channel errors. In both cases, the execution of the IOTCB continues to completion, then the YC ASIC initiates a retry. If this retry is not successful, an error message (IOTCB execution error) is returned to the MIOP. At this point, the operating system determines the procedure to follow for further error resolution.

Figure 4-1 shows how the IOBB fits into the communication path employed by the CRAY Y-MP EL system. It must be remembered that the IOBB is a slave device to the IOP connected to it via the VMEbus. Refer to Figure 4-2 for a general block diagram of the IOBB.

Each of the Y1 busses has a channel pair number assigned to it. Because the Y1 bus is bidirectional, it must be considered a channel pair. These channel assignments are as follows:

- CPU 0

- CC0 channels 20/21

- CC0 channels 22/23

- 40 m/Byte

- CC1 channels 24/25

- CC1 channels 26/27

- CPU 1

- CC0 channels 30/31

- CC0 channels 32/33

- CC1 channels 34/35

- CC1 channels 36/37

- CPU 2

- CC0 channels 40/41

- CC0 channels 42/43

- CC1 channels 44/45

- CC1 channels 46/47

- CPU 3

- CC0 channels 50/51

- CC0 channels 52/53

- CC1 channels 54/55

- CC1 channels 56/57

4-4

# Communications

No discussion of an IOS would be complete without an introduction to the communications channel. The communications channel in the CRAY Y-MP EL system is called the Y1 bus. The Y1 bus is capable of 40-Mbyte/s transfer rates; these data transfers exist as data bursts of 4, 32, 64, or 128 thirty-two-bit words. The actual data signal is a differentiated value that provides a high level of noise immunity. Refer to Appendix B for a general diagram of the Y1 bus, as well as a table that lists the exact pin assignments.

Communication between the MIOP, the other IOSs, and the maintenance workstation (MWS) takes place via an RS-465 serial interface that can sustain transfers of 1.2 Mbits/s. This is a serial interface; therefore, any point that is defective eliminates the string. Essentially, if the MIOP is down, the entire system is down. Refer to Figure 4-3 for an illustration of this daisy chain. This figure also shows the communication path from the MIOP to the required system peripherals via the SCSI interface. These system peripherals are the .25-inch cartridge tape drive and the Winchester hard disk drive. The helical scan tape drive is optional, as is the system console. The system console used with the CRAY Y-MP EL system is a Wyse model 60 using an RS-232 interface to the MIOP.

1000 must be in the daisy chain and it must be the close in the chain

CMM-xxx-PR2

## **IOS-supported Peripheral Controllers**

The design of the IOS allows many different controllers to be installed. Consequently, many different peripheral devices can be connected to the CRAY Y-MP EL system. The types of controllers supported by Cray Research include:

- Enhanced serial drive interface (ESDI) disk controller with one to four 1.3-Gbyte drives

- IPI-2 disk controller with one or two 2.7-Gbyte drives

- Disk array subsystem (DAS) controller that can control 10 to 40 Gbytes of data

- Network controllers

- Ethernet

- FDDI

- HYPERchannel

- Pertec controller with a 125 ips 9-track tape drive

- SCSI controller for square-cartridge tape drive (18-track)

Refer to Figure 4-4 for a configuration diagram of these devices. To gain a more complete understanding of the individual controllers, refer to the Original Equipment Manufacturer (OEM) manuals supplied with the system. The specific controllers are:

- DC-3 ESDI disk controller

- DC-4 IPI-2 disk controller

- DAS-2 disk array subsystem

- 10 ESDI disk drives

- IFI1 FDDI

- HC1 HYPERchannel interface

- HI1 High performance parallel interface (HIPPI)

- SI1 VMEbus SCSI host bus

- TC-2 9-track tape drive interface (Pertec)

Refer to Appendix C for more specifications.

$\bigcirc$ C.

RD-1

MPB

RD-2

Deren

RC-3

Peripireral enclosure

# PERIPHERAL DEVICES

DD3 - ESOI; 1.36B (HITACHI)

PE3-10 ESDI ONCO

(removable Drive)

DOB

onlatt

Shuttle

The CRAY Y-MP EL computer system is designed with customer peripheral requirements in mind. The CRAY Y-MP EL system can accommodate a wide range of peripheral devices with a diverse amount of storage and communication capabilities. Because of this wide range of capabilities, in most cases it is best to refer to the original equipment manufacturer (OEM) manual for specific information on the equipment. A list of available peripheral devices and their characteristics follows.

- DD-3 Winchester disk drive

- High-speed access

- High-speed data transfer rate (2.753 Mbytes/s)

- Enhanced serial drive interface (ESDI) industry standard

- High mean time between failure (MTBF) (150,000 hours, MIL STD 2.17)

- 1.321 Gbytes of formatted storage

- No maintenance

•

system Disk

- DD-4 IPI-2 (intelligent peripheral interface) disk drive

- High-speed data transfer rate (9.34 Mbytes/s)

- High MTBF (150,000 hours, MIL STD 2.17)

- 2.7 Gbytes of formatted storage

TD-2 9-track tape drive (covered in detail in this section)

- TD-3 18-track tape drive (covered in detail in this section)

- EX-2 8mm cartridge tape drive hereal scan

- High density (1638 tracks/in.; 74 Mbits/sq. in.)

- Large capacity cartridge (5 Gbytes)

- Peak transfer rate of 4 Mbytes/s

- Sustained transfer rate of 500 Kbytes/s

- MTBF is 40,000 hours

- Intended as system backup device

SIST

- DAS-2 disk array sybsystem

- 1 disk array controller (DAC)

- 10 ESDI DD-3 drives forming one bank

- 8 data, 1 parity, and 1 spare drive

- 10.4 Gbytes of storage per bank

- Sustained transfer rate of 15 Mbytes/s

- Internal media defect management

- DAS-M disk array controller with multiplexer option installed

- DEB-2 disk array bank

- 8 DD-3 data drives

- 1 DD-3 parity drive

- 1 DD-3 spare drive

- 1 to 4 DEB-2s connect to 1 DAS-M

To obtain a more detailed description of these devices, refer to Appendix C for the design specifications.

All of the peripheral devices are mounted in the cabinets available. The input/output subsystem (IOS) that controls the peripheral is normally included in the same cabinet. Figure 5-1 shows a typical layout of the various components within the system. The exact placement of any component is determined by the system configuration.

The majority of the CRAY Y-MP EL system peripherals are considered field replaceable units (FRUs). This means that when one of the devices breaks down, it is completely replaced. There are no field repairable parts inside the peripherals, except in the 9-track tape drive (TD-2), the 18-track tape drive (TD-3), and the disk array subsystem (DAS-2) controller. These components are described in the following subsections.

DAC

Cray Research Proprietary Preliminary Information CMM-xxx-PR2

Figure 5-1. Example of Cabinet Layout for the CRAY Y-MP EL System

### **TD-2 Tape Drive**

The TD-2 tape drive (hereafter referred to as the TD-2) is a 9-track tape drive that handles open reel 0.5-in. tape. Any reel up to 10.5 in. fits on the unit. The TD-2 is manufactured by Storage Tek Manufacturing, Ltd. of London as Model 9914. It is designed to handle four types of data encoding:

- NRZI non-return to zero indicated (800 bpi)

- PE phase encoded (1600 bpi)

- GCR group coded recording (6250 bpi)

- DPE double phase encoded (3200 bpi)

The TD-2 is controlled by the small computer system interface-1 (SI-1) controller card in the VMEbus that connects to a Pertec cache interface within the TD-2. The Pertec interface is one of the FRUs included in the TD-2. Other FRUs in the TD-2 are as follows:

- Data control board (DCB)

- Digital data processor board (DDP)

- Analog data processor board (ADP)

- Servo control board (SCB)

- Power supply board (PSB) (contains two fuses)

- Hub sensor board (HSB)

- In-chute sensor board

Failures on any of these FRUs can be located by using the onboard diagnostics. These diagnostics are run by using the front panel switches on the TD-2. Other than a tape device that indicates failure, there are no provisions for maintaining the TD-2 via remote diagnostics. Faults must be isolated on site.

For complete information on how to run and interpret these diagnostics, refer to the Storage Tek user/diagnostic manual (# 95121796) supplied with the system. Because several combinations of front panels, switches, and diagnostic programs are available, Storage Tek service and diagnostic manuals must be used as references.

When the failure is diagnosed to the FRU level, the FRU must be replaced using the procedures provided in the Storage Tek servicing manual (# 95121797) provided with the system. It should be noted that there are no individual tape-path FRUs. Instead, the entire tape path subassembly is removed in case of failure. When you remove or insert the tape path subassembly, ensure that the Tacho roller is not misaligned on its pivot shaft. The Tacho roller and the heads are the only components that can be damaged, and can cause the TD-2 to malfunction.

As mentioned, the other components that can be damaged during normal removal and replacement are the read/write heads. These heads are thin film heads and are useless if they are scratched. As a precaution when you remove or install the tape path subassembly, cover the heads with an adhesive bandage. Place the cloth pad over the face of the heads and press the adhesive to the sides. Ensure that the adhesive does not contact the face of the heads. After you install the tape path subassembly, clean the heads to ensure proper operation.

The TD-2 Model 9914 is very sensitive to power line voltages. When you install the TD-2, be sure to check the AC power source before inserting the power cord. If the power source measures less than 115 Vac, be sure to set the input power switch to 100 Vac. In all other instances, set the input power switch to match, as closely as possible, the actual supply voltage.

### TD-3 Tape Drive

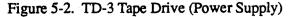

The TD-3 tape drive (TD-3) is also supplied by Storage Tek as the Model 4220 cartridge tape subsystem. The TD-3 is an 18-track tape drive that is IBM 3480 compatible.

The TD-3 comprises several subsystems. These subsystems include:

- Tape transport

- Servo electronics

- Disk drive electronics

- Read/write electronics

- Pneumatics

- Operator control panel

- DC power supply

The disk drive subsystem provides the TD-3 with both functional and diagnostic microcode. The floppy disk drive uses a 3.5-in., 720-Kbyte format, and is controlled by a single integrated circuit (IC) mounted on the system board (SB). Generated signals are sent to or from the drive through the bottom card (BT). The BT contains only foil runners (no active components); therefore, if there is a failure involving the floppy drive, the failing FRU is probably the drive itself or the SB.

As is true in any electro-mechanical device, three types of failure can occur in the TD-3: power-level electrical, mechanical, and signal-level electronic.

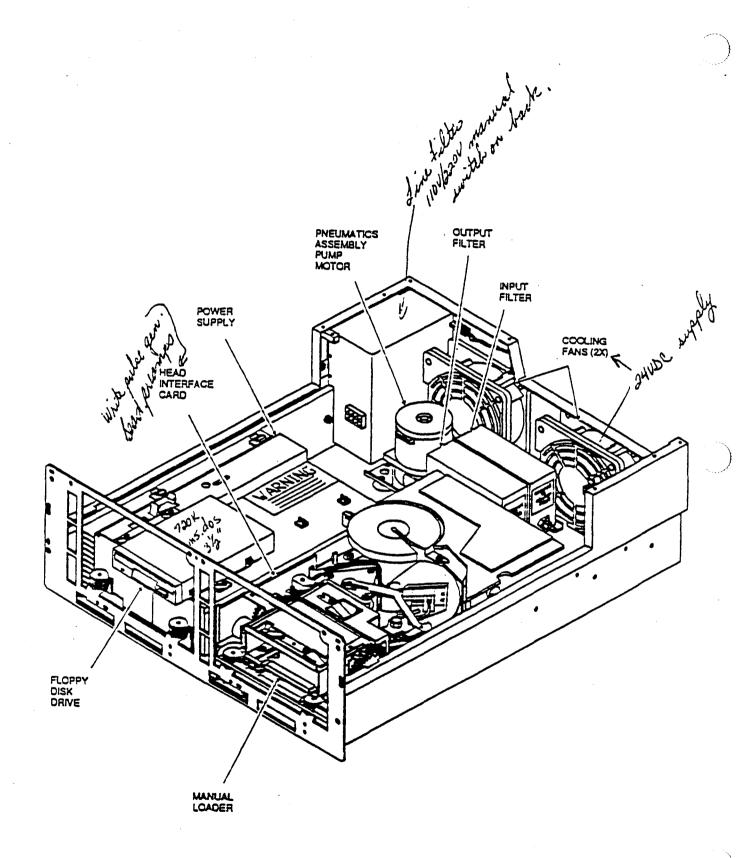

Power circuitry for the TD-3 is designed to accommodate either 100 to 120 Vac or 200 to 240 Vac, switch selectable from 47 to 63 Hz, single phase. From this input, the TD-3 supplies + 5 Vdc, +/- 12 Vdc, and + 24 Vdc to the various subassemblies. The only location in the TD-3 where AC power voltages exist is at the DC power supply board (DCPS). All voltages internal to the TD-3 are DC voltages. Refer to Figure 5-2 to locate the power supply.

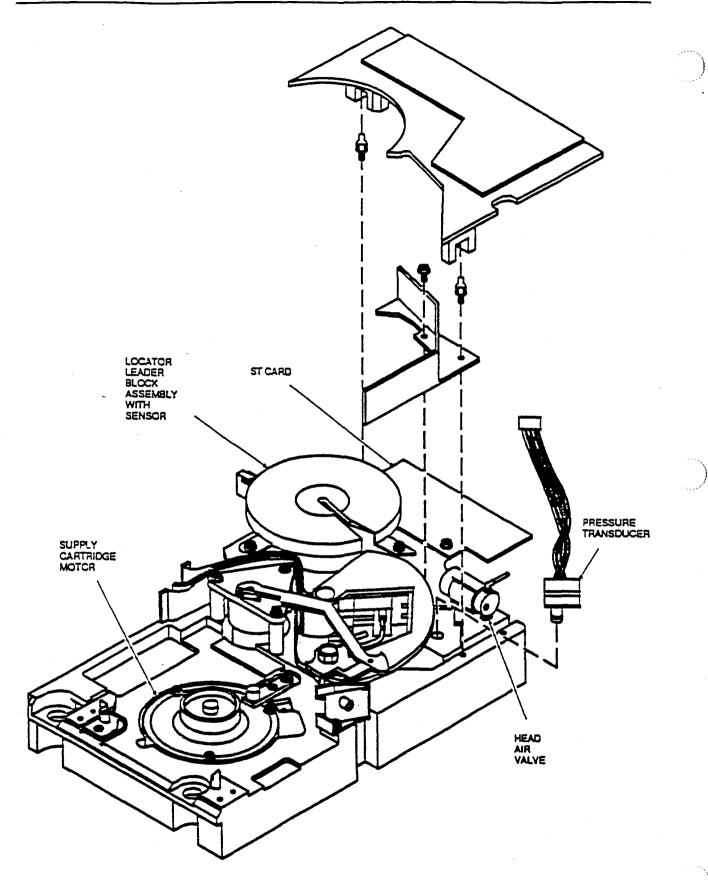

The mechanical processes of the TD-3 are contained primarily on the tape deck. These mechanical processes deal with loading, unloading, and moving the tape after the cartridge is inserted into the deck. Figure 5-3 and Figure 5-4 show the location of the mechanical FRUs. When a mechanical problem occurs, the problem could be caused by another nonmechanical subassembly. For instance, the servo circuitry could be providing values to the mechanical assemblies that emulate a mechanical problem.

Figure 5-3. TD-3 Tape Drive (FRUs)

Figure 5-4. TD-3 Tape Drive (FRUs)

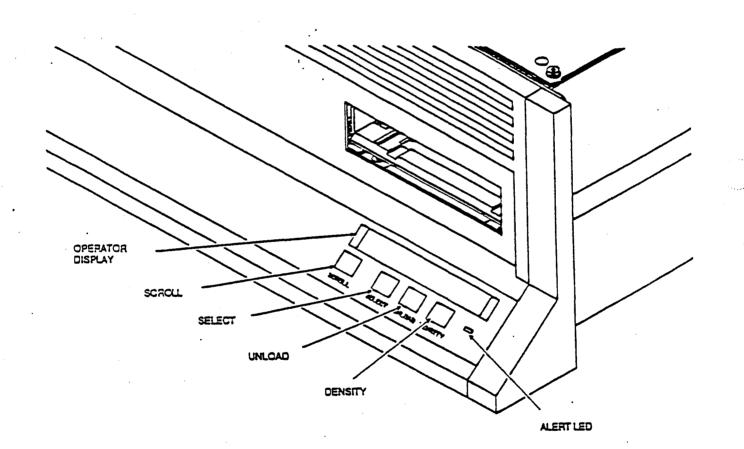

The TD-3 cannot be diagnosed from a remote location. A failing FRU within the TD-3 must be identified by using the front panel to load, run, and read the diagnostics and the error codes associated with them. Figure 5-5 shows the front panel of the TD-3. Note that there are four buttons on the panel, two of which are important to loading and running diagnostics: the scroll and the select buttons.

The scroll button advances the display through a menu, one step at a time. The menu is shown in Figure 5-6. When you reach the desired location in the menu, use the select button to select (lock in) the item. Then, push the select button a second time to run the selected item.

For a complete list and a more detailed explanation of the individual diagnostics available for the TD-3, refer to the Storage Tek manual for the Model 4220 that is supplied with the system. That manual contains an extensive explanation of the diagnostics, the error codes as returned to the operator display, and a complete FRU guide.

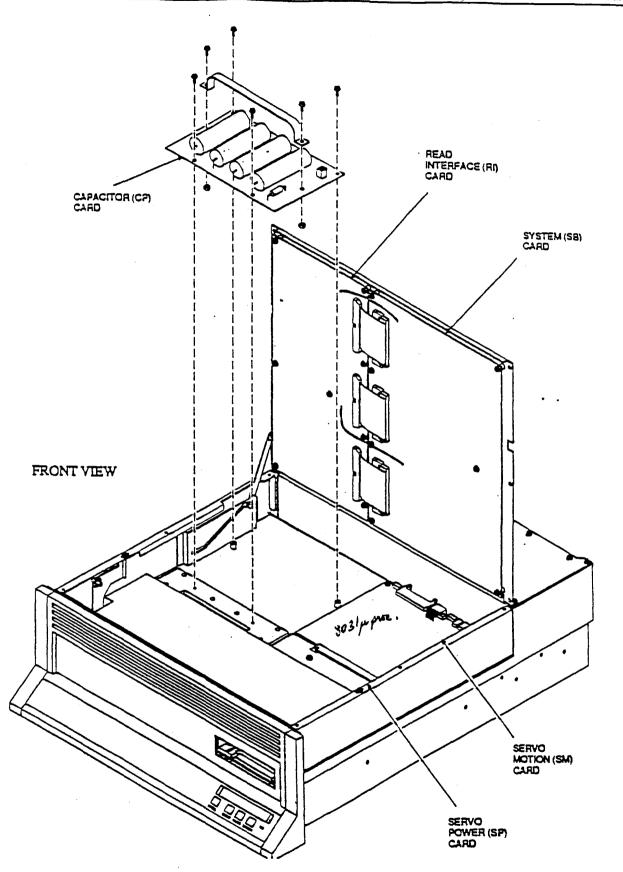

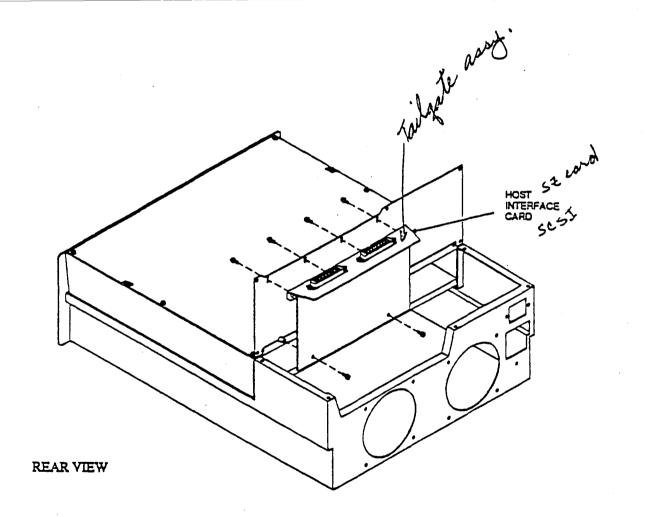

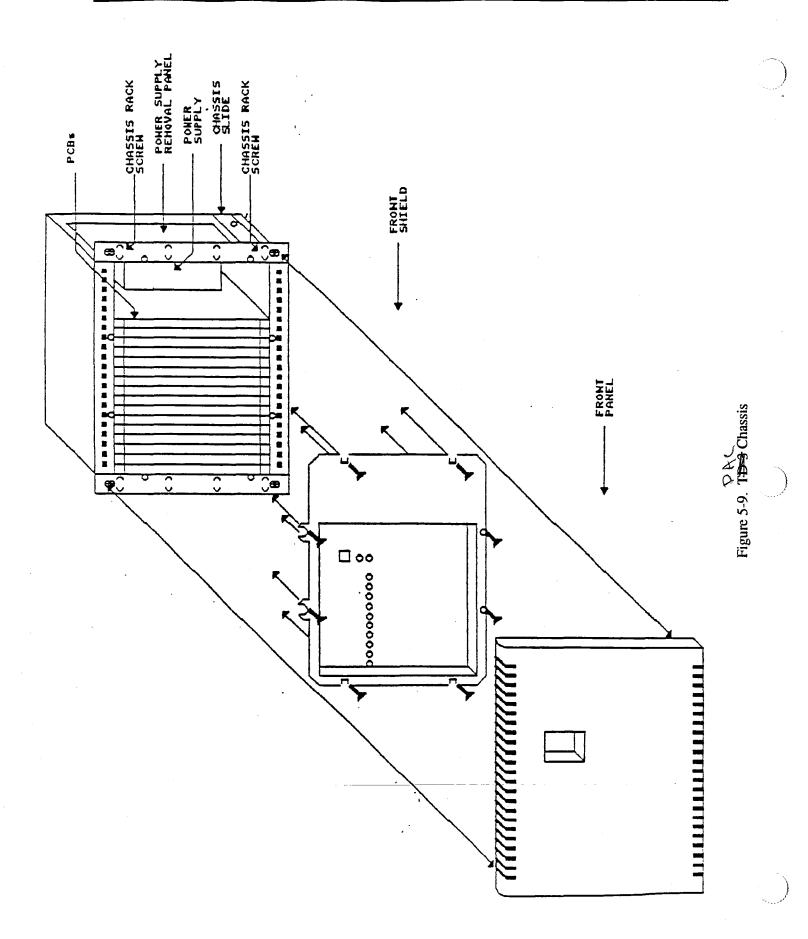

The following printed circuit (PC) boards comprise the signal-level electronics portion of the TD-3. Figure 5-7, Figure 5-8, and Figure 5-9 show the locations of these PC boards.

- Capacitor (CP) card

- Servo monitor (SM) card

- Servo power (SP) card

- Read interface(RI) card

- System (SB) card

Note that the PC boards reside on or under a tip-up lid on the top of the TD-3 (except the SCSI board) and cannot be accessed unless the TD-3 is extended from the rack. Follow the procedure provided in Section 10 of this manual to extend the TD-3.

The RI card controls generation of clock pulses for each track of data via three phase-locked loop (PLL) oscillators. The RI board also contains the write data encoders and peak detectors.

The SB card is the heart of the TD-3. It contains a 68010 microprocessor that processes host commands, provides I/O interface control, and controls the physical processes relating to tape operations. The SB card also includes a write formatter (WF) IC, a 2-Mbyte buffer, buffer FIFOs, an 8031 bus processor, deskew buffers, a floppy disk controller, and read data formatter devices. Be aware that all operations in the TD-3 are linked to the SB. When you troubleshoot the TD-3, remember that the SB may be faulty.

#### Figure 5-5. TD-3 Tape Drive Front Panel

**Offline Menus** [OF:DIAG: \*] [+SUBSYS STATUS] [\*Online Request] [\*Exit 1 [+SET OR DISPLAY] [\*\*CONFIGURATION] [> > Set Diags:None] [> > Diag EC LVL:0] [> > Set Host: SCSI] [> > Lang: English] [> > Set Part: Auto] [> > Set Sync Tm: 2] [> > Passkey: Enab] [> > Sync Nego:Enab] [> > Set BRN: 00] [> Exit 1 [\*Retension Tape] [\*Write Tape Mark] [\*\*Set Scsi ID: 0] [\*\*Set Lun: 0] [\*\*Set Clean: 16K] [\*Exit 1 [+DIAGNOSTICS ] [\*Diag: Test 1 ] [\*Diag: Test 2 ] [\*Diag: Test 3 ] [\*Diag: Test 4 ] [\*Diag:Load/Unld] [\*\*Diag: Loop 1] [Diag: Test Disp] [\*Loader Sensors] [\*Disply Pressure] [\*Disply Tension] [\*Exit 1 [+SAVE TRACE ] [\*Save Trc: All] [\*Exit ]

#### **Online Menus**

[ \*] [ON:IDLE: \*] [+SUBSYS STATUS] [\*Offline Request] [\*Exit ]

#### Figure 5-6. Basic 4280 Menus with a SCSI Interface

Figure 5-7. TD-3 Tape Drive Controller Module FRUs (Front View)

#### Figure 5-8. TD-3 Tape Drive Controller Module FRUs (Rear View)

Cray Research Proprietary Preliminary Information

#### **Disk Array Controller**

The third non-FRU device in the CRAY Y-MP EL system is the disk array controller (DAC) unit supplied by Maximum Strategy, Inc. The DAC is an intelligent disk controller capable of storing and retrieving data from one to four banks of eight standard ESDI disk drives in parallel. The DAC also controls an additional drive for each bank of eight used to store a parity bit for fault protection as well as an operational standby (hot spare) drive used to replace a faulty drive from the bank.

The drives supported by the DAC are 5.25-in. ESDI serial data drives, capable of transferring data at a rate of 16 Mbytes/s.

Each of the ten disk drives in the bank are connected to a disk interface and data buffer PC board in the DAC. The DAC also contains a parity PC board, separate from the parity drive disk interface PC board, and a CPU PC board. The CPU contains a high-speed interface (HSI) unit. The DAC is designed to interface with up to four banks of ESDI drives. If more than one bank of drives is to be controlled, an additional HSI PC board must be installed for each bank. A multiplexer board must also be installed to link the four banks to the one controller.

Figure 5-9 indicates which components must be removed to access the PC boards, and Figure 5-10 shows the location of each of the PC boards within the DAC.

The DAC has a small cut-out on the front panel (refer to Figure 5-9) in which the READY LED, a RESET button, and RS-232 serial communication (COM) port are visible. The READY LED is located on the CPU card in slot 12, and is a visual indicator of the state of the DAC. When the READY LED is glowing solid red, it indicates that the DAC is offline. During a normal power-on sequence or a reset sequence, the LED glows red as the disk drives spin up. The normal time for this sequence should not exceed 120 seconds. If the LED has not turned green after 120 seconds, it indicates a problem with the DAC or with one of the disk drives. Note in Figure 5-9 that each of the disk interface PC boards has an LED visible through the front shield. As the disk drive associated with the interface board spins up, this LED is red. When the disk drive is up to speed and when the internal diagnostics for the disk interface PC board have run, the LED turns green.

If the CPU READY LED is red, no communication is possible with the DAC. If any one of the data buffer/disk interface LEDs is red, either the disk drive failed to reach speed or the internal diagnostics for that interface board failed. In either case, the next step is to initiate disk drive diagnostics.

CRAY Y-MP EL Troubleshooting and Maintenance Manual

Cray Research Proprietary Preliminary Information

16-Slot Configuration

Figure 5-10. DAC Printed Circuit Board Locations

During normal operation, the RESET button should not be used. Instead, the reset function should be initiated by software through the IOS. However, during a power-up sequence you may use the RESET button once if the READY LED fails to turn green within 120 seconds.

The COM port located on the front of the DAC is a serial RS-232 connection that can be used for offline diagnostics or for online system configuration. These functions require test equipment not normally supplied, either on site or at the service center. If you need more information regarding the use of the COM port, refer to the Maximum Strategy documentation supplied with the system or contact Hardware Product Support.

## Diagnostics

The peripheral devices associated with the CRAY Y-MP EL system are FRUs. There is only one online diagnostic test, named olcfdt, that checks the functionality of the peripherals. This test is explained in the *Cray Research Entry Level (EL) Computer System UNICOS Online Diagnostic Maintenance Manual*, publication number SPM-1025. The only response of the olcfdt diagnostic to UNICOS is pass or fail. Likewise, there are no offline diagnostics, in place or planned, to deal specifically with the CRAY Y-MP EL system peripherals.

Disk drives for the CRAY Y-MP EL system are driven by intelligent controllers that perform media defect (flaw) management without operator/technician intervention.

•  $\sum_{i=1}^{n}$ •

$\cdot$

$\bigcirc$ Ũ

6

## DIAGNOSTICS

If the CRAY Y-MP EL computer system does not operate properly, a customer employee is the first person notified. This notification usually occurs via a fault code provided by the UNICOS operating system. The customer employee then follows a procedure, defined by the maintenance contract, to gather error information and notify the Cray Research Service Center.