# **Instruction Set Overview for IEEE CPUs**

(CRAY T90<sup>™</sup> Series)

HTM-317-0

Cray Research Proprietary

Cray Research, Inc.

## **Record of Revision**

#### REVISION DESCRIPTION

April, 1996. Original printing.

Any shipment to a country outside of the United States requires a letter of assurance from Cray Research, Inc.

This document is the property of Cray Research, Inc. The use of this document is subject to specific license rights extended by Cray Research, Inc. to the owner or lessee of a Cray Research, Inc. computer system or other licensed party according to the terms and conditions of the license and for no other purpose.

Cray Research, Inc. Unpublished Proprietary Information — All Rights Reserved.

Autotasking, CF77, CRAY, CRAY-1, Cray Ada, CraySoft, CRAY Y-MP, CRInform, CRI/*Turbo*Kiva, HSX, LibSci, MPP Apprentice, SSD, SUPERCLUSTER, SUPERSERVER, UniChem, UNICOS, and X-MP EA are federally registered trademarks and Because no workstation is an island, CCI, CCMT, CF90, CFT, CFT2, CFT77, ConCurrent Maintenance Tools, COS, CRAY-2, Cray Animation Theater, CRAY APP, CRAY C90, CRAY C90D, Cray C++ Compiling System, CrayDoc, CRAY EL, CRAY J90, Cray NQS, Cray/REELlibrarian, CRAY S-MP, CRAY SUPERSERVER 6400, CRAY T3D, CRAY T3E, CRAY T90, CrayTutor, CRAY X-MP, CRAY XMS, CS6400, CSIM, CVT, Delivering the power . . ., DGauss, Docview, EMDS, GigaRing, HEXAR, IOS, ND Series Network Disk Array, Network Queuing Environment, Network Queuing Tools, OLNET, RQS, SEGLDR, SMARTE, SUPERLINK, System Maintenance and Remote Testing Environment, Trusted UNICOS, UNICOS MAX, and UNICOS/mk are trademarks of Cray Research, Inc.

Requests for copies of Cray Research, Inc. publications should be directed to:

CRAY RESEARCH, INC. Customer Service Logistics 1100 Lowater Road P.O. Box 4000 Chippewa Falls, WI 54729–0078

Comments about this publication should be directed to:

CRAY RESEARCH, INC. Service Publications and Training 890 Industrial Blvd. P.O. Box 4000 Chippewa Falls, WI 54729–0078

## **INSTRUCTION SET OVERVIEW**

| Notational Conventions                     | 2  |

|--------------------------------------------|----|

| Instruction Formats                        | 2  |

| One-parcel Instruction Formats             | 3  |

| Three-parcel Instruction Formats           | 4  |

| Four-parcel Instruction Format             | 6  |

| Extended Instruction Set                   | 7  |

| Special Register Values                    | 7  |

| Undefined Instructions                     | 7  |

| Monitor-mode Instructions                  | 8  |

| IMI-mode Instructions                      | 9  |

| Instruction and Branch Timing              | 11 |

| Issue Timing                               | 11 |

| Branch Timing                              | 13 |

| Special CAL Syntax Forms                   | 14 |

| Instruction Summary                        | 14 |

| Figures                                    |    |

| Figure 1. Vector Element Layout            | 2  |

| Figure 2. General Instruction Format       | 3  |

| Figure 3. One-parcel Instruction Formats   | 4  |

| Figure 4. Three-parcel Instruction Formats | 5  |

| Figure 5. Four-Parcel Instruction Formats  | 6  |

| Tables                                     |    |

| Table 1. Special Register Values           | 7  |

| Table 2. Monitor-mode Instructions         | 8  |

| Table 3. IMI-mode Instructions             | 9  |

| Table 4. Special Indicators                | 15 |

| Table 5. Instruction Set                   | 15 |

This overview describes the instruction set for the IEEE CPU. The Triton mode (TRI) bit in the exchange package is not used in the IEEE CPU because the CPU is always in Triton mode. There is no C90 mode.

#### **Notational Conventions**

This document uses the following conventions:

- Machine instructions are octal; all other numbers are decimal unless otherwise indicated.

- Register bits are numbered from right to left.

- The letter n represents a specified value.

- Variable parameters are in *italic* type.

- The symbol \* designates an arithmetic product.

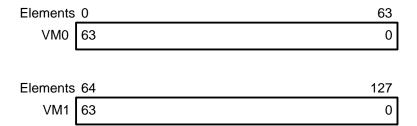

- The VM register contains the vector mask bits, which consist of two parts: VM0 and VM1. As shown in Figure 1, VM0 contains vector mask bits for elements 0 through 63; VM1 contains vector mask bits for elements 64 through 127.

Figure 1. Vector Element Layout

#### **Instruction Formats**

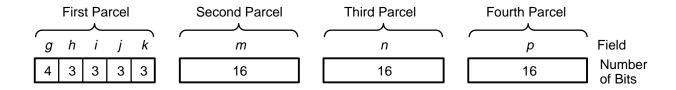

Instructions can be 1 parcel (16 bits), 3 parcels (48 bits), or 4 parcels (64 bits) long. Instructions contain 4 parcels per word. Within a word, parcels are numbered 0 through 3 from left to right.

A 3- or 4-parcel instruction can begin in any parcel of a word and can span a word boundary. For example, a 3-parcel instruction beginning in parcel 3 of a word ends in parcel 1 of the next word. No padding of word boundaries is required. Any parcel position can be addressed in branch instructions.

Figure 2 shows the general instruction format. The first parcel is divided into five fields. The second, third, and fourth parcels each contain a single field. Figure 4 and Figure 5 show how multiparcel instructions are actually stored in memory.

Figure 2. General Instruction Format

#### **One-parcel Instruction Formats**

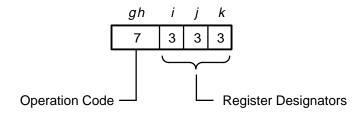

Most instructions are 1-parcel instructions; there are two types of 1-parcel instruction formats as shown in the following list. Figure 3 illustrates these two formats.

- 1-parcel instructions with discrete *j* and *k* fields

- 1-parcel instructions with combined j and k fields

In 1-parcel instructions with discrete j and k fields, the j and k fields usually designate operand registers. The i field designates a destination register. Some instructions do not use all three of these fields. Other instructions use the i or k field to provide additional bits for the operation code.

Figure 3. One-parcel Instruction Formats

In 1-parcel instructions with combined j and k fields, the jk field usually contains a constant or designates a source or destination register. The i field usually designates a destination or source register. Some instructions use the i field or bit 2 of the j field to provide additional bits for the operation code.

Some 1-parcel instructions of both formats are part of the extended instruction set. For example, they perform different operations when immediately preceded by the extended instruction set (EIS) instruction 005400.

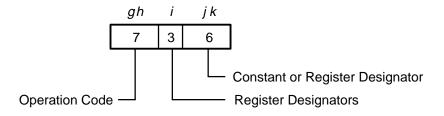

## **Three-parcel Instruction Formats**

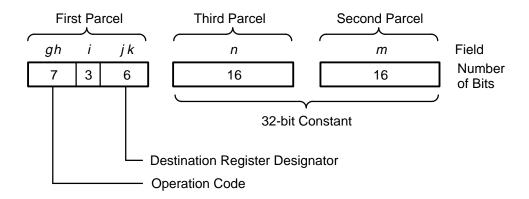

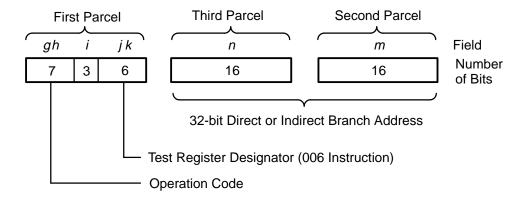

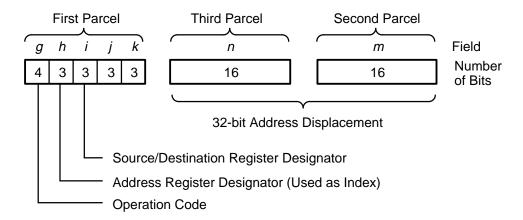

Some instructions are 3-parcel instructions. Figure 4 shows the 3-parcel format.

- 3-parcel instruction with field *nm* as a constant

- 3-parcel instruction with field *nm* as a branch address

- 3-parcel instruction with field *nm* as an address displacement

In all three formats, field nm is a 32-bit field with parcel n (the last parcel of the instruction) the most significant parcel.

Three-parcel instructions with the nm fields as constants transmit a constant value to an A or S register (instructions 020, 021, 040, and 041). The i field specifies the destination register. The j and k fields are not used, except that bits 1 and 2 of the j field specify different operations for instructions 020 and 040.

Figure 4. Three-parcel Instruction Formats

Three-parcel instructions with the nm fields as jump addresses are used for all types of jumps (instructions 006 through 017). Instructions 006 and 007 use i field bit 0 to distinguish between direct and indirect jumps.

Instruction 006 uses i field bit 2 to distinguish between unconditional and conditional jumps. For conditional jumps, instruction 006 uses the jk field as the test register designator. Instructions 010 through 017 do not use the i, j, and k fields.

Three-parcel instructions with field nm as address displacements are used for A-register and S-register memory references (instructions 10h through 13h) using normal addressing. The h field selects an A register to be used as an address index. The i field designates an A or S register as the source or destination of the data. For memory read references (instructions 10h and 12h) j field bit 1 disables/enables bypass of the data cache. Bit 2 of the j field must be 0 to indicate a 3-parcel (normal addressing) instruction. The k field is not used.

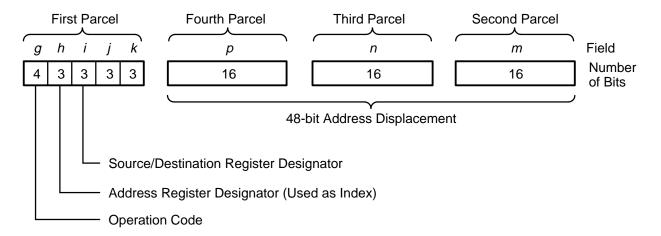

#### **Four-parcel Instruction Format**

Figure 5 shows the 4-parcel instruction format. Field *pnm* is a 48-bit field with parcel *p* (the last parcel of the instruction) as the most significant parcel.

Figure 5. Four-Parcel Instruction Formats

Four-parcel instructions are used for A- and S-register memory references (instructions 10h through 13h) that use extended addressing. The h field selects an A register to be used as an address index. The i field designates an A or S register as the source or destination of the data. For memory read references (instructions 10h and 12h), j field bit 1 disables/enables bypass of the data cache. Bit 2 of the j field must be 1 to indicate a 4-parcel (extended addressing) instruction. The k field is not used.

#### **Extended Instruction Set**

The operation of some 1-parcel instructions is modified when they immediately follow a special instruction parcel (005400). The set of modified instructions is called the extended instruction set (EIS).

Each EIS instruction must be immediately preceded by the instruction parcel 005400 or 0055xx or the instruction performs its normal operation. For example, if instruction 044ijk is *not* preceded by parcel 005400, it computes the logical sum of registers Sj and Sk and transmits the result to register Si. If instruction 044ijk is preceded by parcel 005400, it computes the logical sum of registers Aj and Ak and transmits the result to register Ai.

## **Special Register Values**

If register A0 or S0 is referenced in the h, j, or k field of certain instructions, the contents of the respective register are not used; instead, a special operand is generated.

The special operand is available regardless of existing A0 or S0 reservations (and in this case is not checked). This special operand does not alter the actual value of the A0 or S0 register. If register A0 or S0 is used in the i field as the operand, the actual value of the register is provided. Cray Assembly Language (CAL) issues a caution-level error message for A0 or S0 when 0 does not apply to the i field. Table 1 lists the special register values.

Table 1. Special Register Values

| Instruction Field | Operand Value |

|-------------------|---------------|

| Ah, h = 0         | 0             |

| Aj, j = 0         | 0             |

| Ak, k = 0         | 1             |

| Sj, j = 0         | 0             |

| Sk, k = 0         | bit 63 = 1    |

## **Undefined Instructions**

Executing an illegal instruction produces undefined results. Some instructions cause an error exit, others are no-operation (no-op) instructions, etc. However, no illegal instruction will halt or hang the CPU.

#### **Monitor-mode Instructions**

Monitor mode is active when the monitor mode (MM) bit in the exchange package modes field is set.

Monitor-mode instructions perform specialized functions that are useful to the operating system. These instructions execute normally only if the CPU is in monitor mode. If a monitor-mode instruction issues while the CPU is in user mode, the instruction is treated as a no-op instruction. However, all hold-issue conditions still apply.

In normal user mode, most monitor-mode instructions act as simple no-ops; program execution continues with the next sequential instruction. Instruction 073ij1 (j = 2 through 7) is the only exception. If this instruction is executed in normal user mode, it returns a value of 0 to register Si.

In interrupt-on-monitor-instruction (IMI) mode, most monitor-mode instructions execute as no-ops, but a monitor instruction interrupt (MII) occurs before the next instruction issues. Instruction 073ij1 (j = 2 through 7) is the only monitor-mode instruction that executes normally when the IMI mode bit is set. Table 2 lists the instructions that are privileged to monitor mode.

Table 2. Monitor-mode Instructions

| Machine Instruction             | CAL Syntax    | Machine Instruction             | CAL Syntax              |

|---------------------------------|---------------|---------------------------------|-------------------------|

| 0010 <i>jk</i> ( <i>jk</i> ≠ 0) | CA,Aj Ak      | 001406                          | ECI                     |

| 0011 <i>jk</i>                  | CL,Aj Ak      | 001407                          | DCI                     |

| 0012 <i>j</i> 0                 | CI,Aj         | 001500                          | _                       |

| 0012 <i>j</i> 1                 | MC,A <i>j</i> | 001501                          | _                       |

| 0012 <i>j</i> 2                 | DI,A <i>j</i> | 001600                          | ESI                     |

| 0012 <i>j</i> 3                 | EI,A <i>j</i> | 001640                          | BCD                     |

| 0013 <i>j</i> 0                 | XA Aj         | 0017 <i>jk</i>                  | BP <i>k</i> A <i>j</i>  |

| 0013 <i>j</i> 1                 | A <i>j</i> XA | 023 <i>ij</i> 6                 | A <i>i</i> EA, <i>j</i> |

| 001302                          | EMI           | 023 <i>ij</i> 7                 | Ai EA,Aj                |

| 001303                          | DMI           | 027 <i>ij</i> 2                 | EA <i>j</i> A <i>i</i>  |

| 0014 <i>j</i> 0                 | RT Sj         | 027 <i>ij</i> 3                 | EA,Aj Ai                |

| 0014 <i>j</i> 1                 | SIPI Aj       | 033 <i>i</i> 00                 | A <i>i</i> CI           |

| 001402                          | CIPI          | 033 <i>ij</i> 0 ( <i>j</i> ≠ 0) | Ai CA,Aj                |

| 0014 <i>j</i> 3                 | CLN Aj        | 033 <i>ij</i> 1 ( <i>j</i> ≠ 0) | Ai CE,Aj                |

| 0014 <i>j</i> 4                 | PCI Sj        | 073ij1 (j = 2 - 7)              | Si SRj                  |

| 001405                          | CCI           | 073 <i>i</i> 05                 | SR0 Si                  |

#### **IMI-mode Instructions**

IMI mode is active when the monitor mode (MM) bit in the exchange package modes field is clear and the IMI bit in the exchange package interrupt modes field is set.

IMI mode is a special operating mode designed to facilitate testing of an operating system in a nondedicated CPU. The operating system being tested is run under the control of a supervisory program that runs in monitor mode. The test operating system runs in IMI mode.

The test operating system can run most instructions at full speed. However, monitor-mode instructions and instructions that affect the system environment or the environment of the test operating system are trapped. (Most trapped instructions execute as no-ops, but some execute normally.) After execution of a trapped instruction, an MII occurs. The supervisory program can then simulate the operation of the trapped instruction.

For proper operation, the cluster number (CLN) must be set to 0 when the CPU is operating in IMI mode. Table 3 lists all instructions that are trapped in IMI mode.

Table 3. IMI-mode Instructions

| Machine Instruction                                                                                                                                         | CAL                                                                                                              | Syntax                                       | Operation When IMI Mode Active                                                                                                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 0010jk (jk ≠ 0)<br>0011jk<br>0012j0<br>0012j1<br>0012j2<br>0012j3<br>0013j0<br>0013j1<br>0014j0<br>0014j1<br>001402<br>0014j3<br>0014j4<br>001405<br>001406 | CA,Aj<br>CL,Aj<br>CI,Aj<br>MC,Aj<br>DI,Aj<br>EI,Aj<br>XA<br>Aj<br>RT<br>SIPI<br>CIPI<br>CLN<br>PCI<br>CCI<br>ECI | Ak<br>Ak<br>Aj<br>XA<br>Sj<br>Aj<br>Aj<br>Sj | These instructions are privileged to monitor mode. They execute as no-ops in IMI mode. An MII interrupt occurs after the instruction executes. |

| 001407<br>001500                                                                                                                                            | DCI<br>—                                                                                                         |                                              |                                                                                                                                                |

| 001501<br>001600<br>001640                                                                                                                                  | —<br>ESI<br>BCD                                                                                                  |                                              | These instructions are privileged to monitor mode. They execute as no-ops in IMI mode. An MII interrupt occurs after the instruction executes. |

| Machine Instruction                                                                                           | CAL                                                                            | Syntax                                | Operation When IMI Mode Active                                                                                                                                                                                                                                               |

|---------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0017 <i>jk</i><br>023 <i>ij</i> 6<br>023 <i>ij</i> 7<br>027 <i>ij</i> 2<br>027 <i>ij</i> 3<br>073 <i>i</i> 05 | BP <i>k</i><br>A <i>i</i><br>A <i>i</i><br>EA <i>j</i><br>EA,A <i>j</i><br>SR0 | Aj<br>EA,j<br>EA,Aj<br>Ai<br>Ai<br>Si |                                                                                                                                                                                                                                                                              |

| 00200 <i>k</i><br>073 <i>i</i> 01<br>073 <i>i</i> 25 (no-op when in<br>maintenance mode)                      | VL<br>S <i>i</i><br>SR2                                                        | A <i>k</i><br>SR0<br>S <i>i</i>       | These instructions execute normally in IMI mode. An MII interrupt occurs after the instruction executes.                                                                                                                                                                     |

| 002100<br>002200<br>002210<br>002300<br>002301<br>002400<br>002401<br>002500<br>002501<br>002600<br>002601    | EFI DFI CBL ERI EBP DRI DBP DBM ESC EBM DSC                                    |                                       | These instructions execute normally in normal user mode, but execute as no-ops in IMI mode. An MII interrupt occurs after the instruction executes.                                                                                                                          |

| 073 <i>i</i> 02<br>073 <i>ij</i> 3<br>073 <i>ij</i> 6                                                         | SM<br>ST <i>j</i><br>ST,A <i>j</i>                                             | Si<br>Si<br>Si                        | Because the cluster number must be set to 0 when IMI mode is active, these instructions execute as no-ops. An MII interrupt occurs after the instruction executes.                                                                                                           |

| 0064jknm (j2 = 0)<br>0064jknm (j2 = 1)                                                                        | JTS <i>jk</i><br>JTS,A <i>k</i>                                                | exp<br>exp                            | Because the cluster number must be set to 0 when IMI mode is active, these instructions execute as no-ops. An MII interrupt occurs after the instruction executes. Following the interrupt, the P register points to the second parcel ( <i>m</i> field) of the instruction. |

| 033 $i$ 00<br>033 $i$ $j$ 0 ( $j \neq 0$ )<br>033 $i$ $j$ 1 ( $j \neq 0$ )                                    | Ai<br>Ai<br>Ai                                                                 | CI<br>CA,A <i>j</i><br>CE,A <i>j</i>  | These instructions execute normally when IMI mode is active, but the data is blocked from entering register Ai. This effectively makes them no-ops. An MII interrupt occurs after the instruction executes.                                                                  |

| 073 <i>ij</i> 1 ( <i>j</i> = 2,3)                                                                             | Si                                                                             | SR <i>j</i>                           | This instruction is privileged to monitor mode. It executes normally in IMI mode except that the performance monitor pointer is prevented from advancing. An MII interrupt occurs after the instruction executes.                                                            |

| 073 ij1 $(j = 4 - 7)$                                                                                         | Si                                                                             | SR <i>j</i>                           | This instruction is privileged to monitor mode. It clears register Si to 0 in IMI mode. An MII interrupt occurs after the instruction executes.                                                                                                                              |

| Machine Instruction | CAL Syntax | Operation When IMI Mode Active                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 073 <i>i</i> 75     | SR7 Si     | This instruction operates as a no-op unless maintenance mode is active. With maintenance mode active, this instruction operates normally. An MII interrupt occurs after the instruction executes.  NOTE: Normal use of this instruction requires checking of register SR0 bit 0 before executing the instruction. Because the instruction that does the checking (073 <i>i</i> 01) is trapped in IMI mode, it is recommended that instruction 073 <i>i</i> 75 not be used in IMI mode. |

## **Instruction and Branch Timing**

The instruction buffer attempts to keep ahead of instruction issue; this reduces instruction waiting times. Because the instruction set is complex and is executing in a complex environment, issue timing might not seem deterministic (due to things such as variable wait times for memory conflicts). However, some general rules can be stated for events that occur within a CPU.

### **Issue Timing**

Although the instruction word that is the destination of a branch request is the first word requested from memory (followed by the remainder of the instruction block in circular order) instruction words can enter the stack in any order. (Eight words at a time are requested so that the 32-word block is requested over 4 clock periods.) Priority conflicts, however, can lengthen the request time.

The issue logic has five valid flags. The first flag corresponds to the branch address word. The next three flags correspond to the following 3 words (unless the branch address is 3 words or less from the end of a 32-word address block). The last flag indicates the validity of the remainder of the address block.

When the first valid flag sets, the issue unit retrieves the corresponding word from the buffer and starts issuing instructions. At the time the first parcel is issued, a request for the next word is made. The issue unit can request a new instruction word every 4 clock periods (CPs), corresponding to the maximum issue rate. The maximum issue rate is four 1-parcel instructions with no dependencies issued in 4 clock periods.

Issue continues until the next instruction word is required. If the next instruction word is available, issue continues; if the next word is not available, issue halts after the last complete instruction. (Instructions split

across word boundaries are never issued until all parcels are available to the issue unit.) This sequence continues for the first four instruction words/valid flags.

Because the fifth valid flag indicates the validity of the remaining 28 words of the instruction block, issue halts after 4 instruction words unless the entire instruction block is available. This is true even if the first instruction issued is in the middle of the instruction block, with one exception. If the next sequential instruction word of the block enters the buffer in the same clock period that issue would halt, that word is sent to the issue unit without waiting.

In order to reduce delays caused by memory access times, a prefetch of the next sequential 32-word instruction block is requested when the 25th word (8th word from the end) of the current instruction block is entered or when a branch is done into the last 8 words of the current block. If the next instruction block is already in the buffer, it does not have to be fetched from memory. If the current block is still being fetched when the request for the next block occurs, the next block is not fetched until the current fetch is completed; the hardware can perform only one instruction fetch at a time.

A delay occurs if the first word of the next sequential instruction block is needed while the current block is still being fetched. In this case, issue halts after the last word of the first block until the first word of the next block is fetched.

If an out-of-stack branch occurs while the next sequential block is waiting to be prefetched, the prefetch is aborted and the block containing the branch address is fetched instead. Issue of instructions at the branch address are delayed until the fetch of the current block is completed, a fetch of the block containing the branch address can begin, and the requested instruction word is available from the instruction buffer.

If an in-stack branch occurs (either to the current block or to another block in the buffer) while the next sequential block is waiting to be prefetched, the prefetch is aborted. Because the word at the branch address is already in the buffer, no fetch is needed and issue continues without delay.

## **Branch Timing**

In issuing, just like other instructions, a branch instruction is affected by instruction buffer timing and issue interlocks. In addition, timing is affected by branch success and by the destination address of the branch.

Even if the destination address is currently in the instruction stack, timing is further affected by, for example, the destination parcel address and by the size (number of parcels) of the destination instruction.

Two timing numbers are given for branches: issue time and branch time. The issue time corresponds to the number of parcels in the instruction; most branch instructions are 3 parcels long and therefore take 3 clock periods to issue. The branch time listed is the minimum additional time required to complete an in-stack branch.

Branch fall-through, for conditional branches, requires no additional time. If a branch that is taken completes in 10 clock periods (3 CPs to issue and 7 CPs branch time) the fall-through time for that instruction is 3 CPs.

To the times listed, add additional time according to the rules in the following list. This time is in addition to the time required for out-of-stack instruction issues discussed previously and applies only to branches that are taken.

- If the destination parcel is parcel 0, no additional time is added.

- If the destination parcel is parcel 1 and the destination instruction is a 4-parcel instruction, add 1 CP to the branch time. (If it is not a 4-parcel instruction, do not add any time.)

- If the destination is parcel 2 and that instruction is a single parcel, add 1 CP. If it is a multiparcel instruction, add 2 CPs.

- If the destination parcel is parcel 3, add 2 CPs.

This timing can create a special case. If a branch to a multiparcel instruction in parcel 2 can be converted from a branch to a single parcel instruction in parcel 1 (even an inserted no-op before the multiparcel instruction), a CP can be saved even if the multiparcel instruction is not moved. (What would have been a 2-CP wait is converted to 1 CP to issue the single-parcel instruction.) If a 3-parcel instruction can be moved from parcel 2 to parcel 1, two CPs are saved.

## **Special CAL Syntax Forms**

Certain machine instructions can be generated from two or more different CAL instructions. Any of the operations performed by special instructions can be performed by instructions in the basic CAL instruction set. For example, the following CAL instructions generate instruction 002000, which transmits a 1 to the vector length (VL) register:

- VL A0 (normal CAL syntax)

- VL 1 (special CAL syntax)

The first instruction is the basic form of the instruction, which takes advantage of the special case in which (Ak) = 1 if k = 0. The second instruction is a special syntax form that provides the programmer with a more convenient notation for the special case.

In several cases, a single CAL syntax can generate several different machine instructions. These cases provide for transmitting the value of an expression to an A register or S register, or for shifting A register or S register contents. For example, the CAL instruction A*i exp* generates instruction 020, 021, or 022, depending on the value of *exp*. The assembler uses *exp* to determine which instruction to generate.

## **Instruction Summary**

Table 4 lists the special indicators that apply to many of the instructions. When one or more of these indicators applies to a specific instruction, the indicator is shown as a superscript letter following the machine instruction.

Table 5 lists, in numerical order, all instructions in the CRAY T90 series instruction set. Included for each instruction is the machine instruction, the CAL syntax, and a brief description.

Table 4. Special Indicators

| Superscript | Description                                                                |

|-------------|----------------------------------------------------------------------------|

| N           | New instruction (not available on non-IEEE systems)                        |

| D           | Different instruction (op-code has different function on non-IEEE systems) |

| R           | New floating-point format (IEEE format instead of Cray format)             |

| M           | Monitor mode only                                                          |

| 0           | Maintenance mode only                                                      |

Table 5. Instruction Set

| Machine Instruction              | CAL Syntax    | Description                                                                                                                                                                       |

|----------------------------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 000000                           | ERR           | Error exit.                                                                                                                                                                       |

| 001000                           | PASS          | Pass (no operation).                                                                                                                                                              |

| 0010 <i>jk</i> M ( <i>jk</i> ≠0) | CA,Aj Ak      | Set channel (Aj) CA register (Ak) and activate channel.                                                                                                                           |

| 0011 <i>jk</i> <sup>M</sup>      | CL,Aj Ak      | Set channel (Aj) CL register (Ak).                                                                                                                                                |

| 0012 <i>j</i> 0 <sup>M</sup>     | CI,Aj         | Clear interrupt flag and error flag for channel (Aj).<br>Clear Device Master Clear (output channels only).<br>Enable channel interrupt.                                           |

| 0012 <i>j</i> 1 <sup>M</sup>     | MC,Aj         | Clear interrupt flag and error flags for channel (Aj).<br>Set Device Master Clear (output channels only). Clear<br>Ready Held (input channels only). Enable channel<br>interrupt. |

| 0012 <i>j</i> 2 <sup>M</sup>     | DI,A <i>j</i> | Disable channel Aj interrupt.                                                                                                                                                     |

| 0012 <i>j</i> 3 <sup>M</sup>     | EI,A <i>j</i> | Enable channel Aj interrupt.                                                                                                                                                      |

| 0013 <i>j</i> 0 <sup>M</sup>     | XA Aj         | Transmit (Aj) to exchange address.                                                                                                                                                |

| 0013 <i>j</i> 1 <sup>M</sup>     | Aj XA         | Transmit exchange address to Aj.                                                                                                                                                  |

| 001302 <sup>M</sup>              | EMI           | Enable monitor interrupt mode (set EIM to 1).                                                                                                                                     |

| 001303 <sup>M</sup>              | DMI           | Disable monitor interrupt mode (clear EIM to 0).                                                                                                                                  |

| 0014 <i>j</i> 0 <sup>M</sup>     | RT Sj         | Transmit (Sj) to real-time clock.                                                                                                                                                 |

| 0014 <i>j</i> 1 <sup>M</sup>     | SIPI Aj       | Send inter-CPU interrupt to CPU (Aj).                                                                                                                                             |

| 001402 <sup>M</sup>              | CIPI          | Clear inter-CPU interrupt.                                                                                                                                                        |

| 0014 <i>j</i> 3 <sup>M</sup>     | CLN Aj        | Transmit (Aj) to cluster number register.                                                                                                                                         |

| 0014 <i>j</i> 4 <sup>M</sup>     | PCI Sj        | Transmit (Sj) to programmable clock.                                                                                                                                              |

| 001405 <sup>M</sup>              | CCI           | Clear programmable clock interrupt (clear PCI to 0).                                                                                                                              |

| 001406 <sup>M</sup>              | ECI           | Enable programmable clock interrupt (set IPC to 1).                                                                                                                               |

| 001407 <sup>M</sup>              | DCI           | Disable programmable clock interrupt (clear IPC to 0).                                                                                                                            |

| Machine Instruction          | CAL Syntax | Description                                                |

|------------------------------|------------|------------------------------------------------------------|

| 001500 <sup>M</sup>          | _          | Clear all performance monitor counters.                    |

| 001501 <sup>M</sup>          | _          | Clear performance monitor pointer.                         |

| 001600 <sup>M</sup>          | ESI        | Enable system I/O interrupts (set SEI to 1).               |

| 0016 <i>j</i> 1 <sup>M</sup> | IVCP Aj    | Invalidate cache in CPU (Aj).                              |

| 0016 <i>ј</i> 2 <sup>М</sup> | IVCL Aj    | Invalidate cache in CPUs in cluster (Aj).                  |

| 001640 <sup>M</sup>          | BCD        | Broadcast cluster detach.                                  |

| 0017 <i>jk</i> <sup>M</sup>  | BP,k Aj    | Transmit (A)) to breakpoint address $k$ ( $k = 0$ or 1).   |

| 00200 <i>k</i>               | VL Ak      | Transmit (Ak) to vector length register.                   |

| 002101 <sup>N</sup>          | EFI INV    | Enable floating-point invalid interrupts.                  |

| 002102 <sup>N</sup>          | EFI DIV    | Enable floating-point divide by zero interrupts.           |

| 002103 <sup>N</sup>          | EFI OVF    | Enable floating-point overflow interrupts.                 |

| 002104 <sup>N</sup>          | EFI UNF    | Enable floating-point underflow interrupts.                |

| 002105 <sup>N</sup>          | EFI INX    | Enable floating-point inexact interrupts.                  |

| 002106 <sup>N</sup>          | EFI INP    | Enable floating-point exceptional input interrupts.        |

| 002201 <sup>N</sup>          | DFI INV    | Disable floating-point invalid interrupts.                 |

| 002202 <sup>N</sup>          | DFI DIV    | Disable floating-point divide by zero interrupts.          |

| 002203 <sup>N</sup>          | DFI OVF    | Disable floating-point overflow interrupts.                |

| 002204 <sup>N</sup>          | DFI UNF    | Disable floating-point underflow interrupts.               |

| 002205 <sup>N</sup>          | DFI INX    | Disable floating-point inexact interrupts.                 |

| 002206 <sup>N</sup>          | DFI INP    | Disable floating-point exceptional input interrupts.       |

| 002210                       | CBL        | Clear bit matrix loaded bit (clear BML to 0).              |

| 002300                       | ERI        | Enable interrupt on operand range error (set IOR to 1).    |

| 002301                       | EBP        | Enable interrupt on breakpoint (set IBP to 1).             |

| 002400                       | DRI        | Disable interrupt on operand range error (clear IOR to 0). |

|                              | DBP        | Disable interrupt on breakpoint (clear IBP to 0).          |

| 002500                       | DBM        | Disable bidirectional memory transfers (clear BDM to 0).   |

| 002501                       | ESC        | Enable scalar cache (set SCE to 1).                        |

| 002600                       | EBM        | Enable bidirectional memory transfers (set BDM to 1).      |

| 002601                       | DSC        | Disable and invalidate scalar cache (clear SCE to 0).      |

| 002700                       | CMR        | Complete memory references.                                |

| 002704                       | СРА        | Complete port reads and writes (ports A, B, and C).        |

| 002705                       | CPR        | Complete port reads (ports A and B).                       |

| 002706                       | CPW        | Complete port writes (port C).                             |

| 002707 <sup>N</sup>          | CFP        | Complete all floating-point operations.                    |

| Machine Instruction              | CAL Syr       | ntax                    | Description                                                                                    |

|----------------------------------|---------------|-------------------------|------------------------------------------------------------------------------------------------|

| 0030 <i>j</i> 0                  | VM0           | Sj                      | Transmit (Sj) to VM0.                                                                          |

| 003000                           | VM0           | 0 <sup>S</sup>          | Clear VM0.                                                                                     |

| 0030 <i>j</i> 1                  | VM1           | Sj                      | Transmit (Sj) to VM1.                                                                          |

| 003001                           | VM1           | 0 <sup>S</sup>          | Clear VM1.                                                                                     |

| 0030 <i>j</i> 2                  | VM0           | Aj                      | Transmit (Aj) to VM0.                                                                          |

| 0030 <i>j</i> 3                  | VM1           | Aj                      | Transmit (Aj) to VM1.                                                                          |

| 003004 <sup>N</sup>              | RNM           |                         | Set round-to-nearest mode.                                                                     |

| 003005 <sup>N</sup>              | RUM           |                         | Set round-up mode.                                                                             |

| 003006 <sup>N</sup>              | RZM           |                         | Set round-to-zero mode.                                                                        |

| 003007 <sup>N</sup>              | RDM           |                         | Set round-down mode.                                                                           |

| 0034jk (j2=0)                    | SM <i>jk</i>  | 1,TS                    | Test and set semaphore $jk$ ( $jk = 0 - 37_8$ ).                                               |

| 0034 <i>jk</i> ( <i>j</i> 2=1)   | SM,Ak         | 1,TS                    | Test and set semaphore (Ak).                                                                   |

| 0036jk (j2=0)                    | SM <i>jk</i>  | 0                       | Clear semaphore $jk$ ( $jk = 0 - 37_8$ ).                                                      |

| 0036 <i>jk</i> ( <i>j</i> 2=1)   | SM,Ak         | 0                       | Clear semaphore (Ak).                                                                          |

| 0037jk (j2=0)                    | SM <i>jk</i>  | 1                       | Set semaphore $jk$ ( $jk = 0 - 37_8$ ).                                                        |

| 0037 <i>jk</i> ( <i>j</i> 2=1)   | SM,Ak         | 1                       | Set semaphore (Ak).                                                                            |

| 00400 <i>k</i>                   | EX <i>k</i>   |                         | Exit k.                                                                                        |

| 0050 <i>jk</i>                   | J             | B <i>jk</i>             | Jump to B <i>jk</i> .                                                                          |

| 0051 <i>jk</i> O                 | JINV          | B <i>jk</i>             | Jump to B <i>jk</i> (invalidate instruction buffers).                                          |

| 006000 <i>nm</i>                 | J             | exp                     | Jump to exp.                                                                                   |

| 006100 <i>nm</i>                 | IJ            | exp                     | Jump to address in exp.                                                                        |

| 0064 <i>jknm</i> ( <i>j</i> 2=0) | JTS <i>jk</i> | exp                     | Jump to $exp$ if $SMjk = 1$ ; else set $SMjk$ .                                                |

| 0064 <i>jknm (j</i> 2=1)         | JTS,Ak        | exp                     | Jump to $exp$ if $SM(Ak) = 1$ ; else set $SM(Ak)$ .                                            |

| 007000 <i>nm</i>                 | R             | ехр                     | Return jump to exp; set B00 to (P)+3.                                                          |

| 007100 <i>nm</i>                 | IR            | exp                     | Return jump to address in exp; set B00 to (P)+3.                                               |

| 010000 <i>nm</i>                 | JAZ           | exp                     | Jump to $exp$ if $(A0) = 0$ .                                                                  |

| 011000 <i>nm</i>                 | JAN           | exp                     | Jump to $exp$ if $(A0) \neq 0$ .                                                               |

| 012000 <i>nm</i>                 | JAP           | exp                     | Jump to $exp$ if $(A0) \ge 0$ .                                                                |

| 013000 <i>nm</i>                 | JAM           | exp                     | Jump to <i>exp</i> if (A0) < 0.                                                                |

| 014000 <i>nm</i>                 | JSZ           | ехр                     | Jump to $exp$ if (S0) = 0.                                                                     |

| 015000 <i>nm</i>                 | JSN           | ехр                     | Jump to $exp$ if (S0) $\neq$ 0.                                                                |

| 016000 <i>nm</i>                 | JSP           | ехр                     | Jump to $exp$ if $(S0) \ge 0$ .                                                                |

| 017000 <i>nm</i>                 | JSM           | ехр                     | Jump to <i>exp</i> if (S0) < 0.                                                                |

| 020 <i>i</i> 00 <i>nm</i>        | Ai            | ехр                     | Transmit <i>nm</i> to A <i>i</i> bits $2^0 - 2^{31}$ ; A <i>i</i> bits $2^{32} - 2^{63} = 0$ . |

| 020 <i>i</i> 20 <i>nm</i>        | Ai            | A <i>i</i> : <i>exp</i> | Transmit $nm$ to A $i$ bits $2^0 - 2^{31}$ ; A $i$ bits $2^{32} - 2^{63}$ unchanged.           |

| Machine Instruction                         | CAL Sy                  | ntax                    | Description                                                                                                              |

|---------------------------------------------|-------------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------|

| 020 <i>i</i> 40 <i>nm</i>                   | Ai                      | exp:Ai                  | Transmit $nm$ to Ai bits $2^{32}$ — $2^{63}$ ; Ai bits $2^0$ — $2^{31}$ unchanged.                                       |

| 021 <i>i</i> 00 <i>nm</i>                   | Ai                      | ехр                     | Transmit not( $nm$ ) to Ai bits $2^0 - 2^{31}$ ; Ai bits $2^{32} - 2^{63} = 1$ .                                         |

| 022 <i>ijk</i>                              | Ai                      | exp                     | Transmit <i>jk</i> to A <i>i</i> bits $2^0 - 2^5$ ; A <i>i</i> bits $2^6 - 2^{63} = 0$ .                                 |

| 023 <i>ij</i> 0                             | Ai                      | Sj                      | Transmit (Sj) to Ai.                                                                                                     |

| 023 <i>i</i> 01                             | Ai                      | VL                      | Transmit (VL) to Ai.                                                                                                     |

| 023 <i>ij</i> 6 <sup>M</sup>                | Ai                      | EA,j                    | Transmit exit address j to Ai.                                                                                           |

| 023 <i>ij</i> 7 <sup>M</sup>                | Ai                      | EA,A <i>j</i>           | Transmit exit address (Aj) to Ai.                                                                                        |

| 024 <i>ijk</i>                              | Ai                      | B <i>jk</i>             | Transmit (Bjk) to Ai.                                                                                                    |

| 025 <i>ijk</i>                              | B <i>jk</i>             | Ai                      | Transmit (Ai) to Bjk.                                                                                                    |

| 026 <i>ij</i> 0                             | Ai                      | PS <i>j</i>             | Transmit population count of (Sj) to Ai.                                                                                 |

| 026 <i>ij</i> 1                             | Ai                      | QSj                     | Transmit population count parity of (Sj) to Ai.                                                                          |

| 026 <i>ij</i> 2                             | Ai                      | PA <i>j</i>             | Transmit population count of (Aj) to Ai.                                                                                 |

| 026 <i>ij</i> 3                             | Ai                      | QA <i>j</i>             | Transmit population count parity of (Aj) to Ai.                                                                          |

| 026 <i>ij</i> 4                             | Ai                      | SB,A <i>j</i> ,+1       | Transmit (SB(Aj)) to Ai; increment SB(Aj) by 1.                                                                          |

| 026 <i>ij</i> 5                             | Ai                      | SB <i>j</i> ,+1         | Transmit (SBj) to Ai; increment (SBj) by 1.                                                                              |

| 026 <i>ij</i> 6                             | Ai                      | SB,Aj                   | Transmit (SB(Aj)) to Ai.                                                                                                 |

| 026 <i>ij</i> 7                             | Ai                      | SBj                     | Transmit (SBj) to Ai.                                                                                                    |

| 027 <i>ij</i> 0                             | Ai                      | ZSj                     | Transmit leading zero count of (Sj) to Ai.                                                                               |

| 027 <i>ij</i> 1                             | Ai                      | ZAj                     | Transmit leading zero count of (Aj) to Ai.                                                                               |

| 027 <i>ij</i> 2 <sup>M</sup>                | EA <i>j</i>             | Ai                      | Transmit (Ai) to exit address j.                                                                                         |

| 027 <i>ij</i> 3 <sup>M</sup>                | EA,Aj                   | Ai                      | Transmit (Ai) to exit address (Aj).                                                                                      |

| 027 <i>ij</i> 6                             | SB,Aj                   | Ai                      | Transmit (Ai) to SB(Aj).                                                                                                 |

| 027 <i>ij</i> 7                             | SB <i>j</i>             | Ai                      | Transmit (Ai) to SBj.                                                                                                    |

| 030 <i>ijk</i>                              | Ai                      | A <i>j</i> +A <i>k</i>  | Transmit integer sum of (Aj) and (Ak) to Ai.                                                                             |

| 031 <i>ijk</i>                              | Ai                      | A <i>j</i> –A <i>k</i>  | Transmit integer difference (Aj) and (Ak) to Ai.                                                                         |

| 032 <i>ijk</i>                              | Ai                      | A <i>j</i> *A <i>k</i>  | Address multiply.                                                                                                        |

| 033 <i>i</i> 00 <sup>M</sup>                | Ai                      | CI                      | Transmit channel number of highest-priority interrupt request to A <i>i</i> .                                            |

| 033 <i>ij</i> 0 <sup>M</sup> ( <i>j</i> ≠0) | Ai                      | CA,Aj                   | Transmit current address of channel (Aj) to register Ai.                                                                 |

| 033 <i>ij</i> 1 <sup>M</sup> ( <i>j</i> ≠0) | Ai                      | CE,Aj                   | Transmit status/error word of channel (Aj) to register Ai.                                                               |

| 034 <i>ijk</i>                              | B <i>jk</i> ,A <i>i</i> | ,A0                     | Transmit (A <i>i</i> ) words from common memory starting at address (A0) to B registers starting at register <i>jk</i> . |

| 035 <i>ijk</i>                              | ,A0                     | B <i>jk</i> ,A <i>i</i> | Transmit (A <i>i</i> ) words from B registers starting at register <i>jk</i> to memory starting at address (A0).         |

| Machine Instruction |                           | CAL Sy                  | ntax                                                                                                                          | Description                                                                                                       |  |

|---------------------|---------------------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|--|

|                     | 036 <i>ijk</i>            | T <i>jk</i> ,A <i>i</i> | ,A0                                                                                                                           | Transmit (A <i>i</i> ) words from memory starting at address (A0) to T registers starting at register <i>jk</i> . |  |

|                     | 037 <i>ijk</i>            | ,A0                     | T <i>jk</i> ,A <i>i</i>                                                                                                       | Transmit (Ai) words from T registers starting at register jk to memory starting at address (A0).                  |  |

|                     | 040 <i>i</i> 00 <i>nm</i> | Si                      | exp                                                                                                                           | Transmit <i>nm</i> to S <i>i</i> bits $2^0 - 2^{31}$ ; S <i>i</i> bits $2^{32} - 2^{63} = 0$ .                    |  |

|                     | 040 <i>i</i> 20 <i>nm</i> | Si                      | S <i>i</i> :exp                                                                                                               | Transmit $nm$ to $Si$ bits $2^0 - 2^{31}$ ; $Si$ bits $2^{32} - 2^{63}$ unchanged.                                |  |

|                     | 040 <i>i</i> 40 <i>nm</i> | Si                      | exp:Si                                                                                                                        | Transmit $nm$ to $Si$ bits $2^{32} - 2^{63}$ ; $Si$ bits $2^0 - 2^{31}$ unchanged.                                |  |

|                     | 041 <i>i</i> 00 <i>nm</i> | Si                      | exp                                                                                                                           | Transmit not( $nm$ ) to Si bits $2^0 - 2^{31}$ ; Si bits $2^{32} - 2^{63} = 1$ .                                  |  |

|                     | 042 <i>ijk</i>            | Si                      | <exp< td=""><td>Form 1s mask in S<i>i</i> exp bits from right; <i>jk</i> field gets 100<sub>8</sub> — exp.</td></exp<>        | Form 1s mask in S <i>i</i> exp bits from right; <i>jk</i> field gets 100 <sub>8</sub> — exp.                      |  |

| 005400              | 042 <i>ijk</i>            | Ai                      | <exp< td=""><td>Form 1s mask in A<i>i</i> exp bits from right; <i>jk</i> field gets 100<sub>8</sub> — <i>exp</i>.</td></exp<> | Form 1s mask in A <i>i</i> exp bits from right; <i>jk</i> field gets 100 <sub>8</sub> — <i>exp</i> .              |  |

|                     | 043 <i>ijk</i>            | Si                      | >exp                                                                                                                          | Form 1s mask in Si exp bits from left; jk field gets exp.                                                         |  |

| 005400              | 043 <i>ijk</i>            | Ai                      | >exp                                                                                                                          | Form 1s mask in Ai exp bits from left; jk field gets exp.                                                         |  |

|                     | 044 <i>ijk</i>            | Si                      | Sj&Sk                                                                                                                         | Transmit logical product of (Sj) and (Sk) to Si.                                                                  |  |

| 005400              | 044 <i>ijk</i>            | Ai                      | Aj&Ak                                                                                                                         | Transmit logical product of (Aj) and (Ak) to Ai.                                                                  |  |

|                     | 045 <i>ijk</i>            | Si                      | #Sk&Sj                                                                                                                        | Transmit logical product of $(S_i)$ and one's complement of $(S_i)$ to $S_i$ .                                    |  |

| 005400              | 045 <i>ijk</i>            | Ai                      | #A <i>k</i> &A <i>j</i>                                                                                                       | Transmit logical product of (Aj) and one's complement of (Ak) to Ai.                                              |  |

|                     | 046 <i>ijk</i>            | Si                      | Sj\Sk                                                                                                                         | Transmit logical difference of (Sj) and (Sk) to Si.                                                               |  |

| 005400              | 046 <i>ijk</i>            | Ai                      | Aj\Ak                                                                                                                         | Transmit logical difference of (Aj) and (Ak) to Ai.                                                               |  |

|                     | 047 <i>ijk</i>            | Si                      | #Sj\Sk                                                                                                                        | Transmit logical equivalence of (Sj) and (Sk) to Si.                                                              |  |

| 005400              | 047 <i>ijk</i>            | Ai                      | #Aj\Ak                                                                                                                        | Transmit logical equivalence of (Aj) and (Ak) to Ai.                                                              |  |

|                     | 050 <i>ijk</i>            | Si                      | Sj!Si&Sk                                                                                                                      | Merge (Si) and (Sj) to Si using (Sk) as mask.                                                                     |  |

| 005400              | 050 <i>ijk</i>            | Ai                      | Aj!Ai&Ak                                                                                                                      | Merge Ai and Aj to Ai using (Ak) as mask.                                                                         |  |

|                     | 051 <i>ijk</i>            | Si                      | Sj!Sk                                                                                                                         | Transmit logical sum of (Sj) and (Sk) to Si.                                                                      |  |

| 005400              | 051 <i>ijk</i>            | Ai                      | A <i>j</i> !A <i>k</i>                                                                                                        | Transmit logical sum of (Aj) and (Ak) to Ai.                                                                      |  |

|                     | 052 <i>ijk</i>            | S0                      | S <i>i<exp< i=""></exp<></i>                                                                                                  | Shift (Si) left $exp = jk$ places to S0.                                                                          |  |

| 005400              | 052 <i>ijk</i>            | A0                      | A <i>i<exp< i=""></exp<></i>                                                                                                  | Shift (Ai) left $exp = jk$ places to A0.                                                                          |  |

|                     | 053 <i>ijk</i>            | S0                      | S <i>i&gt;exp</i>                                                                                                             | Shift (Si) right $exp = 100_8 - jk$ places to S0.                                                                 |  |

| 005400              | 053 <i>ijk</i>            | A0                      | A <i>i&gt;exp</i>                                                                                                             | Shift (Ai) right $exp = 100_8 - jk$ places to A0.                                                                 |  |

|                     | 054 <i>ijk</i>            | Si                      | Si <exp< td=""><td>Shift (Si) left <math>exp = jk</math> places to Si.</td></exp<>                                            | Shift (Si) left $exp = jk$ places to Si.                                                                          |  |

| 005400              | 054 <i>ijk</i>            | Ai                      | A <i>i<exp< i=""></exp<></i>                                                                                                  | Shift (Ai) left $exp = jk$ places to Ai.                                                                          |  |

|                     | 055 <i>ijk</i>            | Si                      | S <i>i&gt;exp</i>                                                                                                             | Shift (Si) right $exp = 100_8 - jk$ places to Si.                                                                 |  |

| 005400              | 055 <i>ijk</i>            | Ai                      | A <i>i&gt;exp</i>                                                                                                             | Shift (Ai) right $exp = 100_8 - jk$ places to Ai.                                                                 |  |

| Machine Instruction |                               | CAL Syntax  |                                                                             | Description                                                                         |

|---------------------|-------------------------------|-------------|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

|                     | 056 <i>ijk</i>                | Si          | Si,Sj <ak< th=""><th>Shift (Si) and (Sj) left (Ak) places to Si.</th></ak<> | Shift (Si) and (Sj) left (Ak) places to Si.                                         |

| 005400              | 056 <i>ijk</i>                | Ai          | Ai,Aj <ak< td=""><td>Shift (Ai) and (Aj) left (Ak) places to Ai.</td></ak<> | Shift (Ai) and (Aj) left (Ak) places to Ai.                                         |

|                     | 057 <i>ijk</i>                | Si          | Sj,Si>Ak                                                                    | Shift (Sj) and (Si) right (Ak) places to Si.                                        |

| 005400              | 057 <i>ijk</i>                | Ai          | Aj,Ai>Ak                                                                    | Shift (Aj) and (Ai) right (Ak) places to Ai.                                        |

|                     | 060 <i>ijk</i>                | Si          | Sj+Sk                                                                       | Transmit integer sum of (S <sub>i</sub> ) and (S <sub>k</sub> ) to S <sub>i</sub> . |

|                     | 061 <i>ijk</i>                | Si          | S <i>j</i> –S <i>k</i>                                                      | Transmit integer difference of (Sj) and (Sk) to Si.                                 |

|                     | 062 <i>ijk</i> R              | Si          | S <i>j</i> +FS <i>k</i>                                                     | Floating-point Sj plus Sk to Si.                                                    |

|                     | 063 <i>ijk</i> R              | Si          | S <i>j</i> –FS <i>k</i>                                                     | Floating-point Sj minus Sk to Si.                                                   |

|                     | 064 <i>ijk</i> R              | Si          | S <i>j</i> *FS <i>k</i>                                                     | Floating-point Sj times Sk to Si.                                                   |

|                     | 065 <i>ijk</i> D              | Si          | Sk/FSj                                                                      | Floating-point $Sk$ divided by $Sj$ to $Si$ .                                       |

|                     | 066 <i>ijk</i> D              | Si          | S <i>j</i> *LS <i>k</i>                                                     | Integer Sj times Sk to Si, returning lower.                                         |

| 005400              | 066 <i>ijk</i> N              | Si          | S <i>j</i> *US <i>k</i>                                                     | Integer Sj times Sk to Si, returning upper.                                         |

|                     | 070 <i>ij</i> 0 <sup>D</sup>  | Si          | SQRT,Sj                                                                     | Floating-point square root of Sj to Si.                                             |

|                     | 070 <i>ij</i> 1               | Vi          | CI,Sj&VM                                                                    | Transmit compressed index of (Sj) controlled by (VM) to Vi.                         |

|                     | 070 <i>ij</i> 2 <sup>N</sup>  | Si          | INT,Sj                                                                      | Floating-point Sj to integer Si                                                     |

|                     | 070 <i>ij</i> 3 <sup>N</sup>  | Si          | RINT,Sj                                                                     | Floating-point Sj to rounded integer Si                                             |

|                     | 070 <i>ij</i> 4 <sup>N</sup>  | Si          | FLT,S <i>j</i>                                                              | Integer Sj to floating-point Si                                                     |

|                     | 070 <i>ij</i> 6               | Si          | S <i>j</i> *BT                                                              | Transmit bit-matrix product of $(S_i)$ and $(B^T)$ to $S_i$ .                       |

|                     | 071 <i>i</i> 0 <i>k</i>       | Si          | Ak                                                                          | Transmit (Ak) with no sign extension to Si.                                         |

|                     | 072 <i>i</i> 00               | Si          | RT                                                                          | Transmit real-time clock to Si.                                                     |

|                     | 072 <i>i</i> 02               | Si          | SM                                                                          | Transmit semaphores to Si.                                                          |

|                     | 072 <i>ij</i> 3               | Si          | ST <i>j</i>                                                                 | Transmit (STj) register to Si.                                                      |

|                     | 072 <i>ij</i> 6               | Si          | ST,Aj                                                                       | Transmit ST(Aj) to Si.                                                              |

|                     | 073 <i>i</i> 00               | Si          | VM0                                                                         | Transmit (VM0) to Si.                                                               |

|                     | 073 <i>i</i> 10               | Si          | VM1                                                                         | Transmit (VM1) to Si.                                                               |

|                     | 073 <i>i</i> 20               | Ai          | VM0                                                                         | Transmit (VM0) to Ai.                                                               |

|                     | 073 <i>i</i> 30               | Ai          | VM1                                                                         | Transmit (VM1) to Ai.                                                               |

|                     | 073 <i>ij</i> 1™              | Si          | SR <i>j</i>                                                                 | Transmit (SRj) to Si (monitor mode only for $j = 2 - 7$ ).                          |

|                     | 073 <i>i</i> 02               | SM          | Si                                                                          | Transmit (Si) to semaphores.                                                        |

|                     | 073 <i>ij</i> 3               | ST <i>j</i> | Si                                                                          | Transmit (Si) to STj.                                                               |

|                     | 073 <i>i</i> 05               | SR0         | Si                                                                          | Transmit (S <i>i</i> ) bits 2 <sup>48</sup> — 2 <sup>52</sup> to SR0.               |

| 005400              | 073 <i>i</i> 05 <sup>N</sup>  | SETRM       | Si                                                                          | Set rounding mode from Si.                                                          |

|                     | 073 <i>i</i> 25 <sup>0</sup>  | SR2         | Si                                                                          | Advance performance monitor pointer.                                                |

|                     | 073 <i>i</i> 75 <sup>MO</sup> | SR7         | Si                                                                          | Transmit (Si) to maintenance channel.                                               |

|                     | 073 <i>ij</i> 6               | ST,Aj       | Si                                                                          | Transmit (Si) to ST(Aj).                                                            |

|                     | 074 <i>ijk</i>                | Si          | T <i>jk</i>                                                                 | Transmit (Tjk) to Si.                                                               |

| Machine | Instruction                | CAL Syr                | ntax                                                                                               | Description                                                                                                    |

|---------|----------------------------|------------------------|----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

|         | 075 <i>ijk</i>             | T <i>jk</i>            | Si                                                                                                 | Transmit (Si) to Tjk.                                                                                          |

|         | 076 <i>ijk</i>             | Si                     | V <i>j</i> ,A <i>k</i>                                                                             | Transmit (Vj element (Ak)) to Si.                                                                              |

|         | 077 <i>ijk</i>             | V <i>i</i> ,A <i>k</i> | Sj                                                                                                 | Transmit (Sj) to Vi element (Ak).                                                                              |

|         | 10 <i>hi</i> 00 <i>nm</i>  | Ai                     | exp,Ah                                                                                             | Load Ai from $((Ah) + exp)$ .                                                                                  |

|         | 10 <i>hi</i> 20 <i>nm</i>  | Ai                     | exp,Ah,BC                                                                                          | Load Ai from $((Ah) + exp)$ bypassing data cache and invalidating cache line.                                  |

|         | 10 <i>hi</i> 40 <i>pnm</i> | Ai                     | exp,Ah                                                                                             | Load Ai from $((Ah) + exp)$ .                                                                                  |

|         | 10 <i>hi</i> 60 <i>pnm</i> | Ai                     | exp,Ah,BC                                                                                          | Load Ai from $((Ah) + exp)$ bypassing data cache and invalidating cache line.                                  |

|         | 11 <i>hi</i> 00 <i>nm</i>  | exp,Ah                 | Ai                                                                                                 | Store (Ai) to $((Ah) + exp)$ .                                                                                 |

|         | 11 <i>hi</i> 40 <i>pnm</i> | exp,Ah                 | Ai                                                                                                 | Store (Ai) to $((Ah) + exp)$ .                                                                                 |