# **INPUT/OUTPUT MODULE (IO01)**

| Overview                            | 3  |

|-------------------------------------|----|

| Channel Assignments                 | 6  |

| IO Module Description               | 8  |

| IO Module Orientation in the System | 8  |

| Logical Layout of an IO Module      | 9  |

| Physical Layout of an IO Module     | 11 |

| Options on the IO Module            | 14 |

| DA Option                           | 14 |

| DB Option                           | 14 |

| DC Option                           | 15 |

| DD Option                           | 15 |

| DE Option                           | 15 |

| DR Option                           | 16 |

| DM Option                           | 19 |

| Options on the CPU Module           | 19 |

| HA Option                           | 19 |

| HB and HC Options                   | 19 |

| Connectors on the IO Module         | 20 |

| IO Module to CPU Module             | 20 |

| IO Module to Bulkhead               | 20 |

| Maintenance Connector               | 20 |

| Channel Functions                   | 21 |

| LOSPX Channel                       | 21 |

| Maintenance Channel                 | 21 |

| Error Logger Channel                | 22 |

| Support Channel                     | 22 |

| MCU                                 | 22 |

| LOSP Channel                        | 24 |

| LOSP Protocol                       | 27 |

| LOSP Channel Instructions           | 28 |

| I/O Commands                        | 29 |

|    | 50-Mbyte/s MISP Protocol                          | 31 |

|----|---------------------------------------------------|----|

|    | Ready Signal                                      | 31 |

|    | Data Lines 2 <sup>0</sup> through 2 <sup>15</sup> | 31 |

|    | Parity Bits                                       | 31 |

|    | Resume Signal                                     | 31 |

|    | Disconnect Signal                                 | 32 |

|    | Disconnecting Resume Signal                       | 32 |

|    | HISP Channel                                      | 32 |

|    | HISP Input Sequence                               | 33 |

|    | HISP Output Sequence                              | 38 |

|    | HISP Errors                                       | 42 |

|    | VHISP Channel                                     | 43 |

|    | VHISP Instructions                                | 43 |

|    | VHISP Addressing                                  | 44 |

|    | VHISP Input Sequence                              | 44 |

|    | VHISP Input Data Path                             | 45 |

|    | VHISP Output Sequence                             | 47 |

|    | VHISP Errors                                      | 49 |

|    | I/O Data Path through the CP Module               | 50 |

|    | I/O Write Path through the CP Module              | 50 |

|    | I/O Read Path through the CP Module               | 50 |

|    | I/O Logic on Shared Module                        | 53 |

|    | Acronyms                                          | 54 |

|    | Shared Module Ports                               | 54 |

|    | Shared Module Options                             | 56 |

|    | SA Option                                         | 56 |

|    | SB Option                                         | 56 |

|    | SC Option                                         | 56 |

|    | SD Option                                         | 56 |

|    | Shared Command Codes                              | 57 |

|    | I/O Command Flow through Shared Module            | 58 |

|    | I/O Sequence                                      | 61 |

|    | 1/O Sequence                                      | 01 |

| ig | jures                                             |    |

|    | Figure 1. IO Module Position within System        | 9  |

|    | Figure 2. IO Module Logical Layout                | 10 |

|    |                                                   |    |

| Figures (cont | inued)                                                           | ·  |  |  |

|---------------|------------------------------------------------------------------|----|--|--|

| Figure 3.     | IO Module Construction                                           | 11 |  |  |

| Figure 4.     | IO Module Board 1                                                | 12 |  |  |

| Figure 5.     | IO Module Board 2 1                                              |    |  |  |

| Figure 6.     | MCU Channel Format                                               | 23 |  |  |

| Figure 7.     | LOSP 0 and 1 Input Control and Data                              | 25 |  |  |

| Figure 8.     | LOSP 0 and 1 Output Control and Data                             | 26 |  |  |

| Figure 9.     | HISP Input Sequence                                              | 35 |  |  |

| Figure 10.    | HISP 0 Input Data                                                | 36 |  |  |

| Figure 11.    | HISP 0 Input Control and Address                                 | 37 |  |  |

| Figure 12.    | HISP Output Sequence                                             | 39 |  |  |

| Figure 13.    | HISP 0 Output Control and Address                                | 40 |  |  |

| Figure 14.    | HISP 0 Output Data                                               | 41 |  |  |

| Figure 15.    | VHISP Input Control Signals                                      | 45 |  |  |

| Figure 16.    | VHISP 0 Input Control and Data                                   | 46 |  |  |

| Figure 17.    | VHISP Output Control Signals                                     | 47 |  |  |

| Figure 18.    | VHISP 0 Output Control and Data                                  | 48 |  |  |

| Figure 19.    | CPU Options – Write (IO to Memory)                               | 51 |  |  |

| Figure 20.    | CPU Options – Read (Memory to IO)                                | 52 |  |  |

| Figure 21.    | Channel Request Information Flow                                 | 53 |  |  |

| Figure 22.    | Shared Module Port/Group Designation                             | 55 |  |  |

| Figure 23.    | CPU-to-Shared Module Initial Data Flow                           | 58 |  |  |

| Figure 24.    | SA Option Conflict Resolution                                    | 59 |  |  |

| Figure 25.    | Data Format for Shared Module-to-CPU Transfers .                 | 60 |  |  |

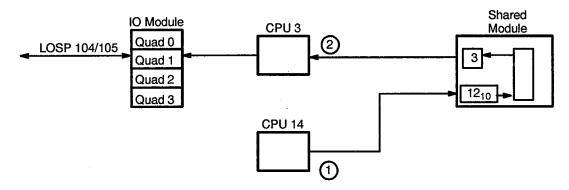

| Figure 26.    | CPU 14 Requests Channel 105 from the Shared Module               | 61 |  |  |

| Figure 27.    | Shared Module Sends Request to the IO Module                     | 62 |  |  |

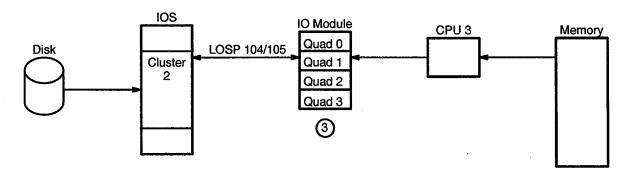

| Figure 28.    | Channel 104 Sending Disk Request Packet to the IOS through CPU 3 | 62 |  |  |

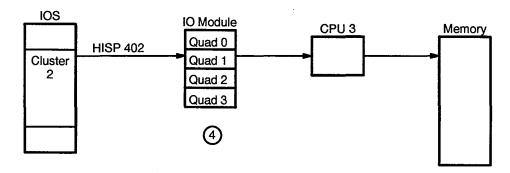

| Figure 29.    | HISP Transfer from IOS to Mainframe                              | 63 |  |  |

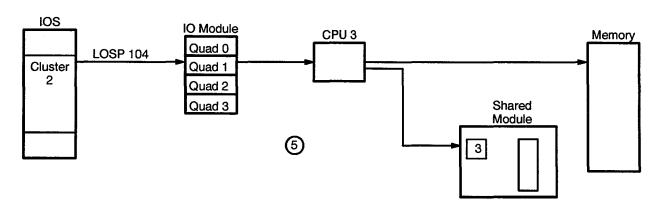

| Figure 30.    | LOSP Transfer from the IOS to Mainframe Memory                   | 63 |  |  |

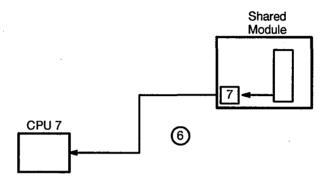

| Figure 31.    | CPU 7 is Interrupted                                             | 64 |  |  |

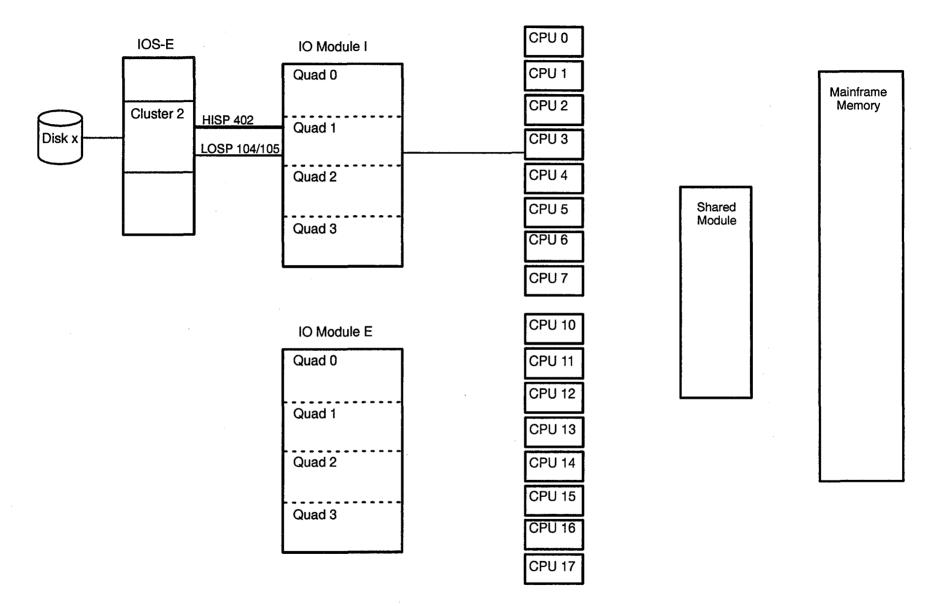

| Figure 32.    | Example System Configuration                                     | 66 |  |  |

| Tables        |                                                                  |    |  |  |

Table 1.

Table 2.

I/O Channel Assignments (CRAY T932 System) ...

I/O Channel Assignments (CRAY T916 System) ...

7

7

# Tables (continued)

| Table 3.  | I/O Channel Assignments (CRAY T94 System)     | 8  |

|-----------|-----------------------------------------------|----|

| Table 4.  | HISP and VHISP Data Buffer Option Assignments | 16 |

| Table 5.  | LOSP Channel Data Buffer Option Assignments   | 18 |

| Table 6.  | LOSP Channel Instructions                     | 29 |

| Table 7.  | DC Option I/O Command Packets                 | 30 |

| Table 8.  | HISP Address and Block Length Options         | 33 |

| Table 9.  | HISP Errors                                   | 42 |

| Table 10. | VHISP Instructions                            | 43 |

| Table 11. | VHISP Channel Errors                          | 49 |

| Table 12. | Shared Command Codes                          | 57 |

## **Overview**

The IO module provides an interface between the CPU and channels and the peripheral devices for the CRAY T90 series system. Each IO module supports the following channels:

- 8 low-speed (LOSP) channels

- 8 high-speed (HISP) channels

- 4 very high-speed (VHISP) channels

- 4 LOSPX channels

The term *LOSPX* refers to either the error logger channel, the maintenance channel, the support channel, or the maintenance control unit interrupt (MCU) channel. The quadrant position on the IO module determines the type of a given LOSPX channel. LOSPX channel assignments are as follows: quadrant 0 is the maintenance channel; quadrant 1 is the support channel; quadrant 2 is the error logger channel; and quadrant 3 is the MCU channel.

A fully configured CRAY T90 series system (a CRAY T932 system with four IO modules) can support the following channels:

- 32 LOSP

- 32 HISP

- 16 VHISP

- 16 LOSPX

A CRAY T916 system can support the following channels:

- 16 LOSP

- 16 HISP

- 8 VHISP

- 8 LOSPX

A CRAY T94 system can support the following channels:

- 8 LOSP

- 8 HISP

- 4 VHISP

- 4 LOSPX

Logical channel numbers are as follows:

LOSP: 100 through 177

HISP: 400 through 437

VHISP: 20 through 37

LOSPX support channel: 60 through 67

An IO module connects directly to a CPU module with electronic zero insertion force (EZIF) orthogonal interconnect module (OIM) connectors. OIMs connect modules that are on an orthogonal plane. Within a stack of 8 CPU modules (in a CRAY T916 or CRAY T932 system), CPUs 2, 3, 4, and 5 connect to the IO module. In a CRAY T94 system, CPUs 0, 1, 2, and 3 connect to the IO module.

External cabling begins at the IO module via I/O connectors. Cables within the CRAY T90 series system route through the chassis and connect to the bulkhead where external cable connections reside.

Any CPU can access any I/O channel. A direct connection does not always exist between the CPU making a request and the IO module receiving it; therefore, I/O commands are always sent to the local shared module first. If the local shared module cannot access the IO module, it sends the command to the remote shared module. The remote shared module sends the command to an I/O channel through the CPU module that lies between the shared module and the IO module.

# **Channel Assignments**

Table 1 lists the channel assignments for the CRAY T932 system. The column labeled "Quadrant" refers to the four quadrants on the IO module. The column labeled "IO Module" refers to the physical position of the module within the system. Note that HISP channel numbers are for reference only because the CPU cannot issue a HISP instruction.

Table 2 provides similar information for the CRAY T916 system, and Table 3 provides information for CRAY T94 systems.

Table 1. I/O Channel Assignments (CRAY T932 System)

| IO<br>Module | CPU<br>Physical<br>Number | IO<br>Module<br>Quadrant | VHISP<br>Number | LOSP<br>Number  | HISP<br>Number | Support<br>Channel<br>Number |

|--------------|---------------------------|--------------------------|-----------------|-----------------|----------------|------------------------------|

| Α            | 22                        | 0                        | 30              | 140/141,142/143 | 420, 421       |                              |

|              | 23                        | 1                        | ·· 31           | 144/145,146/147 | 422, 423       | 64/65                        |

|              | 24                        | 2                        | 32              | 150/151,152/153 | 424, 425       |                              |

|              | 25                        | 3                        | 33              | 154/155,156/157 | 426, 427       |                              |

| E†           | 12                        | 3                        | 24              | 120/121,122/123 | 410, 411       |                              |

|              | 13                        | 2                        | 25              | 124/125,126/127 | 412, 413       |                              |

|              | 14                        | 1                        | 26              | 130/131,132/133 | 414, 415       | 62/63                        |

|              | 15                        | 0                        | 27              | 134/135,136/137 | 416, 417       |                              |

|              | 2                         | 0                        | 20              | 100/101,102/103 | 400, 401       |                              |

|              | 3                         | 1                        | 21              | 104/105,106/107 | 402, 403       | 60/61                        |

|              | 4                         | 2                        | 22              | 110/111,112/113 | 404, 405       |                              |

|              | 5                         | 3                        | 23              | 114/115,116/117 | 406, 407       |                              |

| М†           | 32                        | 3                        | 34              | 160/161,162/163 | 430, 431       |                              |

|              | 33                        | 2                        | 35              | 164/165,166/167 | 432, 433       |                              |

|              | 34                        | 1                        | 36              | 170/171,172/173 | 434, 435       | 66/67                        |

|              | 35                        | 0                        | 37              | 174/175,176/177 | 436, 437       | <u> </u>                     |

<sup>†</sup> This IO module is positioned upside down.

Table 2. I/O Channel Assignments (CRAY T916 System)

| IO<br>Module | CPU<br>Physical<br>Number | IO<br>Module<br>Quadrant | VHISP<br>Number | LOSP<br>Number  | HISP<br>Number | Support<br>Channel<br>Number |

|--------------|---------------------------|--------------------------|-----------------|-----------------|----------------|------------------------------|

| 1            | 2                         | 0                        | 20              | 100/101,102/103 | 400, 401       |                              |

|              | 3                         | 1                        | 21              | 104/105,106/107 | 402, 403       | 60/61                        |

|              | 4                         | 2                        | 22              | 110/111,112/113 | 404, 405       |                              |

|              | 5                         | 3                        | 23              | 114/115,116/117 | 406, 407       |                              |

| E†           | 12                        | 3                        | 24              | 120/121,122/123 | 410, 411       |                              |

|              | 13                        | 2                        | 25              | 124/125,126/127 | 412, 413       |                              |

|              | 14                        | 1                        | 26              | 130/131,132/133 | 414, 415       | 62/63                        |

|              | 15                        | 0                        | 27              | 134/135,136/137 | 416, 417       |                              |

<sup>†</sup> This IO module is positioned upside down.

Table 3. I/O Channel Assignments (CRAY T94 System)

| IO<br>Module | CPU<br>Physical<br>Number | IO<br>Module<br>Quadrant | VHISP<br>Number | LOSP<br>Number  | HISP<br>Number | Support<br>Channel<br>Number |

|--------------|---------------------------|--------------------------|-----------------|-----------------|----------------|------------------------------|

| Α            | 0                         | 0                        | 20              | 100/101,102/103 | 400, 401       |                              |

|              | 1 .                       | 1                        | 21              | 104/105,106/107 | 402, 403       | 60/61                        |

|              | 2 ·                       | 2                        | 22              | 110/111,112/113 | 404, 405       |                              |

|              | 3                         | 3                        | 23              | 114/115,116/117 | 406, 407       |                              |

# **IO Module Description**

The following paragraphs describe the orientation of the IO module within the entire system as well as its logical and physical layout. The options and connectors on the IO module are also described.

# **IO Module Orientation in the System**

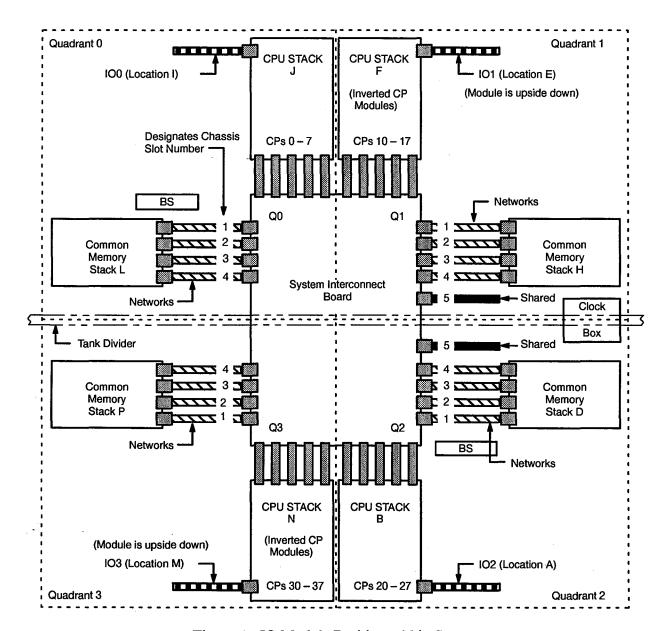

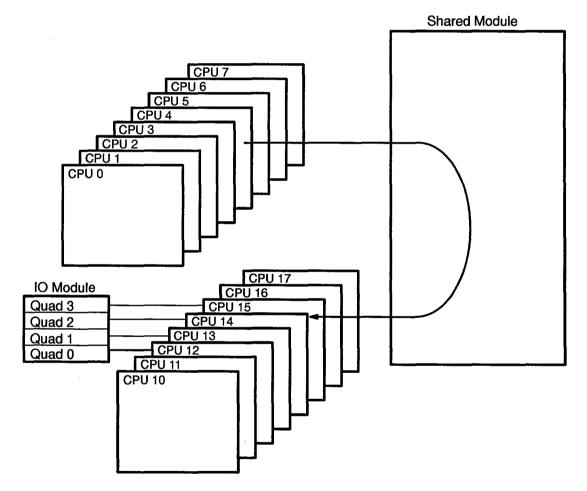

Figure 1 shows the position of the IO modules within the system, which is divided into four quadrants: 0, 1, 2, and 3. An IO module can reside in any or all quadrants. The IO modules are designated 0 (quadrant 0), 1 (quadrant 1), 2 (quadrant 2), and 3 (quadrant 3).

Figure 1 illustrates a CRAY T932 system. The CRAY T916 system, which has only quadrants 0 and 1 populated, can contain two IO modules, and the CRAY T94 system contains only one.

In CRAY T916 systems, the CP modules in stack location F are inverted; board 2 is facing up, and board 1 is facing down. For this reason, the IO module in quadrant 1 (location E) is positioned upside down.

In CRAY T932 systems, the IO module is positioned upside down in quadrant 1 (location E) and quadrant 3 (location M). This is necessary because the CP modules in stack locations F and N are inverted.

Figure 1. IO Module Position within System

# Logical Layout of an IO Module

The IO module is divided into four logical groups or quadrants. Each quadrant on the module can handle transfers for the following channels:

- 2 LOSP channels

- 2 HISP channels

- 1 VHISP channel

- 1 LOSPX channel

Each quadrant is logically connected to one of the four CPUs that physically connect to the IO module.

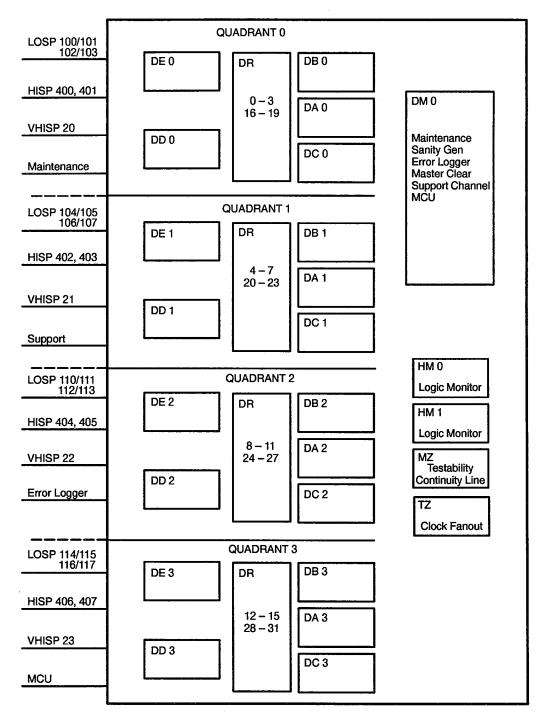

Figure 2 shows the options and channel assignments per quadrant for the IO modules in a CRAY T916 or CRAY T932 system. Software channel numbering is based on the position of the module within the system.

Figure 2. IO Module Logical Layout

# Physical Layout of an IO Module

The IO module is a single assembly that consists of one 8-layer printed circuit board (A board) laminated between two 22-layer printed circuit boards (boards 1 and 2), as shown in Figure 3. Logic chips are mounted on boards 1 and 2.

| Board 1 | 22 Layers |

|---------|-----------|

| A Board | 8 Layers  |

| Board 2 | 22 Layers |

Figure 3. IO Module Construction

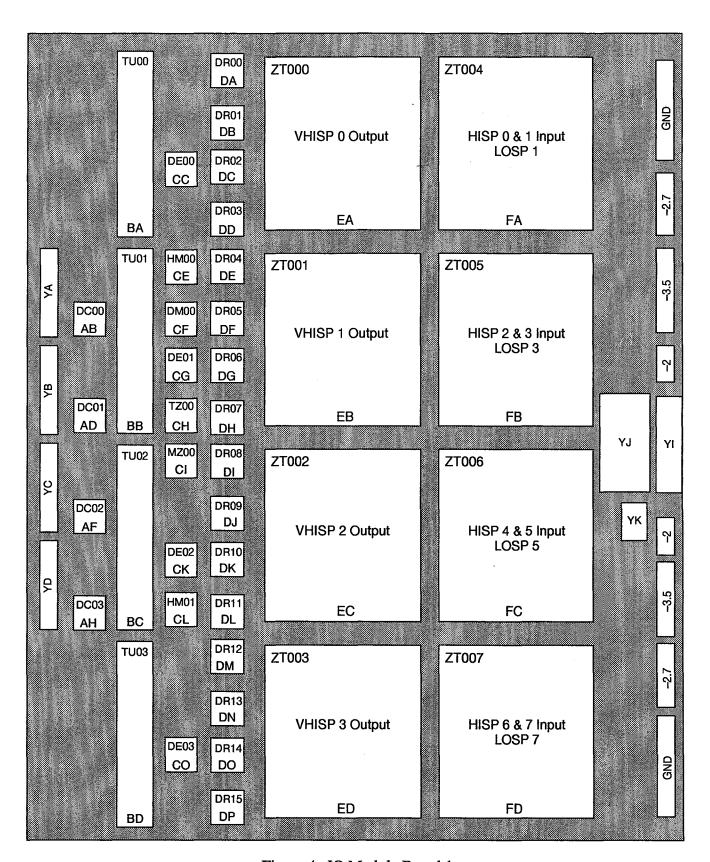

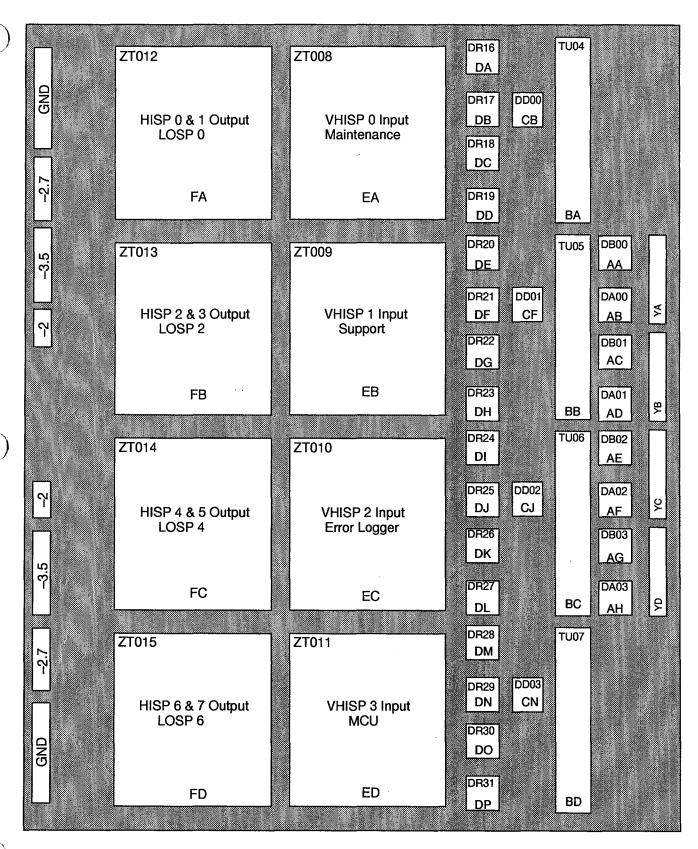

Each IO module has 16 channel connectors, which are described later in this document. Terminators for VHISP, HISP, and LOSP control signals are also located on the module. Figure 4 is a diagram of the physical layout of board 1; Figure 5 shows board 2.

Figure 4. IO Module Board 1

Figure 5. IO Module Board 2

## **Options on the IO Module**

Each of the four logical quadrants contains the following options:

- DA option (1 each quadrant)

- DB option (1 each quadrant)

- DC option (1 each quadrant)

- DD option (1 each quadrant)

- DE option (1 each quadrant)

- DR option (8 each quadrant)

- DM option (1 per IO module)

#### **DA Option**

This option is one of two data interface options used to interface the CPU and I/O channels. An IO module contains four DA options. These options are labeled DA00, DA01, DA02, and DA03, which corresponds to the four quadrants of the module: 0, 1, 2, and 3.

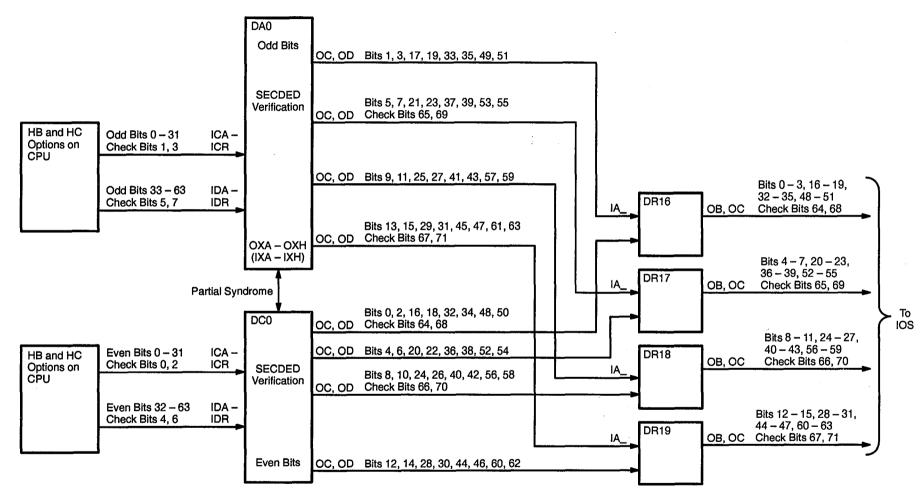

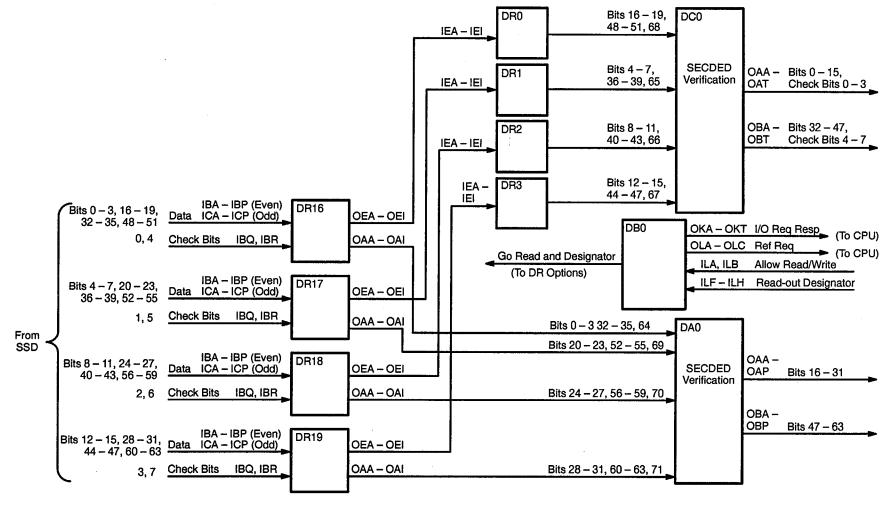

During a read operation (memory to I/O), the DA option receives 32 data bits and 4 check bits of each memory word. This option handles only the odd data bits and odd check bits (the DC option handles the even bits). Data is then passed to the DR options of that quadrant, based on the channel transfer.

During a write operation (I/O to memory), the DA option passes 32 data bits (bits 00 through 15 and 32 through 47) and all 8 check bits to the CPU. The DA option receives data from the DR options in the quadrant.

The DA option also verifies SECDED on the data it passes for either the read or write operation. On a LOSP write operation, the DA option generates check bits before the data passes to the CPU.

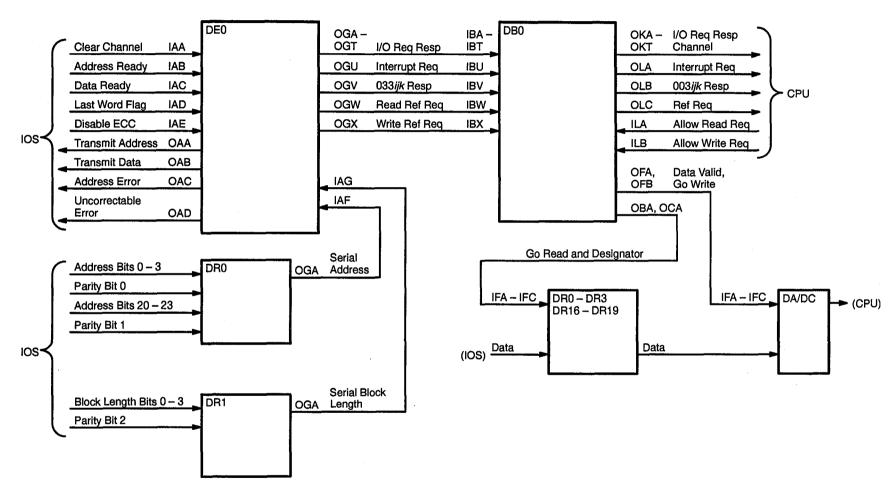

#### **DB Option**

Four DB options reside on the IO module. The DB option is the interface between the CPU and the channel controller options (DD/DE) for the IO module. As with the DA and DC options, each quadrant of the IO module uses one DB option.

The DB option passes reference request information to the CPU for either a read or a write operation. The reference request packet contains a read/write bit, memory group, SECDED control, reference designator, block length, and address.

The DB option receives reference request, interrupt request, and 033 response information from the DD and DE options for all channel types (LOSP, HISP, and VHISP). The DB communicates with the DA, DC, and DR options to send data to and receive data from the CPU.

# **DC Option**

Four DC options reside on the IO module. These options are labeled DC00, DC01, DC02, and DC03.

During a read operation (memory to IO), the DC option receives 32 data bits and 4 check bits of each memory word. This option handles only the even data and check bits.

During a write operation (IO to memory), the DC option passes 32 data bits (bits 16 through 31 and 48 through 63) to the CPU. The data is received from the DR options of the quadrant.

The DC option verifies SECDED on the data it passes for either the read or write operation, and it passes channel address information to the IO module on LOSP and VHISP transfers.

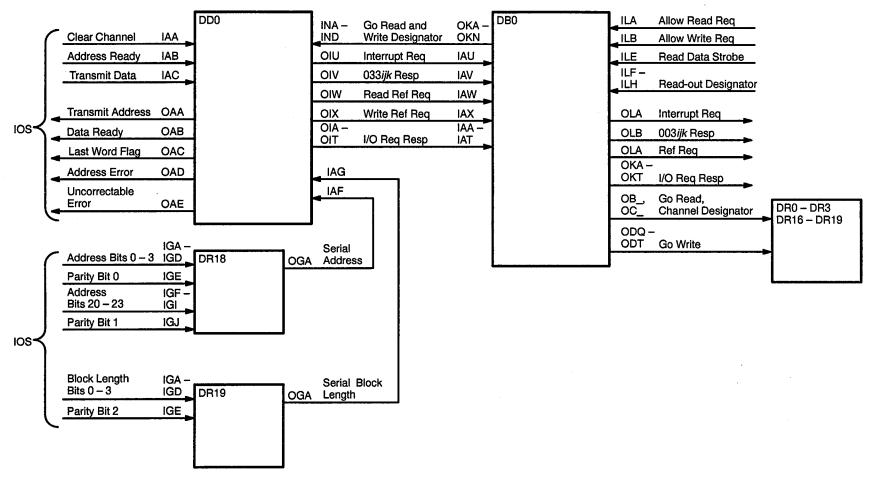

## **DD Option**

The DD option is the channel control option for the following channels: HISPO out, HISP1 out, LOSPO, and LOSPX. The DD option sends LOSP control signals to and receives HISP control signals from the external devices. Each IO module has four DD options, one in each quadrant.

The DD option contains the memory addressing registers for the channels indicated, including both current address registers and limit address registers. This option multiplexes its addresses and sends the resulting CPU address to the DB option.

The DD option sends LOSP, VHISP, and HISP control terms to and receives them from external devices.

## **DE Option**

The DE option is the channel control option for the HISP 0 in, HISP 1 in, LOSP 1, and VHISP channels. The DE option contains the memory addressing registers for the channels indicated, including both current address registers and limit address registers. This option multiplexes its addresses and sends the resulting CPU address to the DB option.

The DE option sends LOSP, VHISP, and HISP control terms to and receives them from external devices.

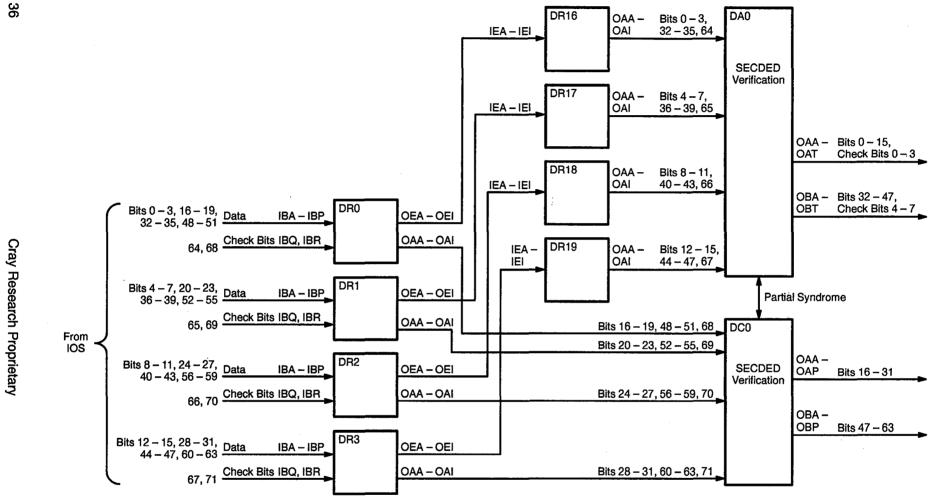

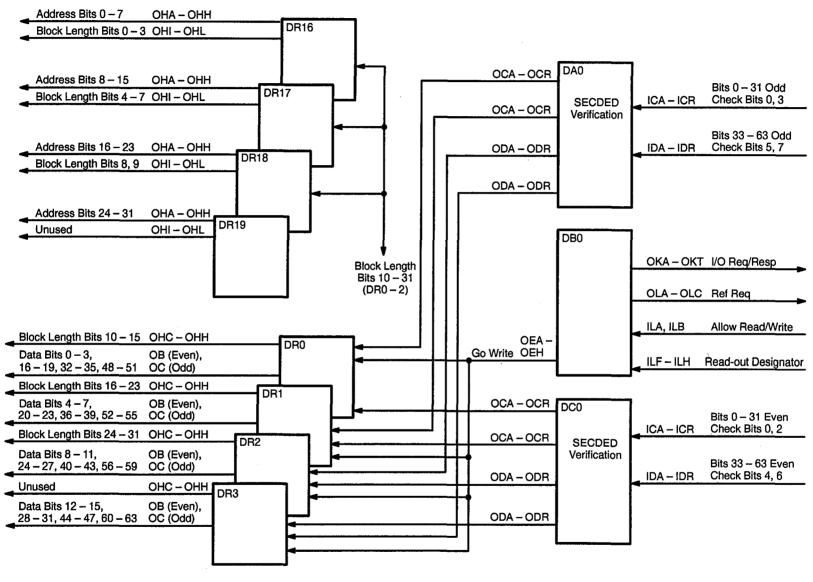

## **DR Option**

The DR option is the data buffer option between the channels and external devices. There are 32 DR options on the IO module. Each quadrant of the IO module contains 8 DR options. Refer again to Figure 2, the IO module logical layout block diagram, for the grouping of options per quadrant.

During a memory-to-I/O transfer, each DR option handles 18 bits (16 data bits and 2 check bits) received from the DA and DC options. During an I/O to memory transfer, each DR option sends 8 data bits and 1 check bit to the DA and DC options.

The DR option contains two data buffers for read data and two buffers for write data. Each buffer has four ranks. Each rank holds 16 words of data, 16 data bits and 2 check bits. These buffers can be circular; in other words, while one rank is being emptied, another rank can be filled.

The DR option receives memory addressing for the HISP channels. It also receives memory addressing and block length for the VHISP channels.

Table 4 describes the HISP and VHISP data buffer option assignments. Note that the bit assignments for the DR options on board 2 (DR16-31) are swapped with those on board 1. Table 5 describes the LOSP channel data buffer option assignments.

Table 4. HISP and VHISP Data Buffer Option Assignments

| Channel        | Option | Bits                                        |

|----------------|--------|---------------------------------------------|

| HISP 0 input   | DR000  | 0 – 3, 16 – 19, 32 – 35, 48 – 51, CB 0, 4   |

| HISP 1 input   | DR001  | 4 – 7, 20 – 23, 36 – 39, 52 – 55, CB 1, 5   |

|                | DR002  | 8 - 11, 24 - 27, 40 - 43, 56 - 59, CB 2, 6  |

| VHISP 0 output | DR003  | 12 – 15, 28 – 31, 44 – 47, 60 – 63, CB 3, 7 |

| HISP 0 output  | DR016  | 16 – 19, 0 – 3, 48 – 51, 32 – 35, CB 4, 0   |

| HISP 1 output  | DR017  | 20 - 23, 4 - 7, 52 - 55, 36 - 39, CB 5,1    |

|                | DR018  | 24 – 27, 8 – 11, 56 – 59, 40 – 43, CB 6, 2  |

| VHISP 0 input  | DR019  | 28 – 31,12 – 15, 60 – 63, 44 – 47, CB 7, 3  |

Table 4. HISP and VHISP Data Buffer Option Assignments (continued)

| Channel         | Option | Bits                                        |

|-----------------|--------|---------------------------------------------|

| HISP 2 input    | DR004  | 0 – 3, 16 – 19, 32 – 35, 48 – 51, CB 0, 4   |

| HISP 3 input    | DR005  | 4 – 7, 20 – 23, 36 – 39, 52 – 55, CB 1, 5   |

| The onput       | DR006  | 8 – 11, 24 – 27, 40 – 43, 56 – 59, CB 2, 6  |

| "VHISP 1 output | DR007  | 12 - 15, 28 - 31, 44 - 47, 60 - 63, CB 3, 7 |

| HISP 2 output   | DR020  | 16 – 19, 0 – 3, 48 – 51, 32 – 35, CB 4, 0   |

| HISP 3 output   | DR021  | 20 – 23, 4 – 7, 52 – 55, 36 – 39, CB 5,1    |

| ,               | DR022  | 24 - 27, 8 - 11, 56 - 59, 40 - 43, CB 6, 2  |

| VHISP 1 input   | DR023  | 28 - 31,12 - 15, 60 - 63, 44 - 47, CB 7, 3  |

| HISP 4 input    | DR008  | 0 – 3, 16 – 19, 32 – 35, 48 – 51, CB 0, 4   |

| HISP 5 input    | DR009  | 4 – 7, 20 – 23, 36 – 39, 52 – 55, CB 1, 5   |

| ·               | DR010  | 8 – 11, 24 – 27, 40 – 43, 56 – 59, CB 2, 6  |

| VHISP 2 output  | DR011  | 12 - 15, 28 - 31, 44 - 47, 60 - 63, CB 3, 7 |

| HISP 4 output   | DR024  | 16 – 19, 0 – 3, 48 – 51, 32 – 35, CB 4, 0   |

| HISP 5 output   | DR025  | 20 – 23, 4 – 7, 52 – 55, 36 – 39, CB 5,1    |

| ·               | DR026  | 24 - 27, 8 - 11, 56 - 59, 40 - 43, CB 6, 2  |

| VHISP 2 input   | DR027  | 28 - 31,12 - 15, 60 - 63, 44 - 47, CB 7, 3  |

| HISP 6 input    | DR012  | 0 – 3, 16 – 19, 32 – 35, 48 – 51, CB 0, 4   |

| HISP 7 input    | DR013  | 4-7, 20-23, 36-39, 52-55, CB 1, 5           |

| ·               | DR014  | 8-11, 24-27, 40-43, 56-59, CB 2, 6          |

| VHISP 3 output  | DR015  | 12 - 15, 28 - 31, 44 - 47, 60 - 63, CB 3, 7 |

| HISP 6 output   | DR028  | 16 – 19, 0 – 3, 48 – 51, 32 – 35, CB 4, 0   |

| HISP 7 output   | DR029  | 20 - 23, 4 - 7, 52 - 55, 36 - 39, CB 5,1    |

| ·               | DR030  | 24 – 27, 8 – 11, 56 – 59, 40 – 43, CB 6, 2  |

| VHISP 3 input   | DR031  | 28 - 31, 12 - 15, 60 - 63, 44 - 47, CB 7, 3 |

Table 5. LOSP Channel Data Buffer Option Assignments

| Channel | Option | Bits              |

|---------|--------|-------------------|

|         | DR016  | 0 – 3, parity 0   |

| LOSP 0  | DR017  | 4 – 7, parity 1   |

| 2001 0  | DR018  | 8 – 11, parity 2  |

|         | DR019  | 12 – 15, parity 3 |

|         | DR000  | 0 – 3, parity 0   |

| LOSP 1  | DR001  | 4 – 7, parity 1   |

| 2001    | DR002  | 8 – 11, parity 2  |

|         | DR003  | 12 - 15, parity 3 |

|         | DR020  | 0 – 3, parity 0   |

| LOSP 2  | DR021  | 4 – 7, parity 1   |

| 2001 2  | DR022  | 8 – 11, parity 2  |

|         | DR023  | 12 – 15, parity 3 |

|         | DR004  | 0 – 3, parity 0   |

| LOSP 3  | DR005  | 4 – 7, parity 1   |

| 2001 0  | DR006  | 8 – 11, parity 2  |

|         | DR007  | 12 - 15, parity 3 |

|         | DR024  | 0 - 3, parity 0   |

| LOSP 4  | DR025  | 4 - 7, parity 1   |

| 2001 4  | DR026  | 8 – 11, parity 2  |

|         | DR027  | 12 – 15, parity 3 |

|         | DR008  | 0 - 3, parity 0   |

| LOSP 5  | DR009  | 4 - 7, parity 1   |

| 200. 0  | DR010  | 8 – 11, parity 2  |

|         | DR011  | 12 - 15, parity 3 |

|         | DR028  | 0 - 3, parity 0   |

| LOSP 6  | DR029  | 4 - 7, parity 1   |

|         | DR030  | 8 11, parity 2    |

|         | DR031  | 12 – 15, parity 3 |

|         | DR012  | 0 - 3, parity 0   |

| LOSP 7  | DR013  | 4 – 7, parity 1   |

| 2001 1  | DR014  | 8 – 11, parity 2  |

|         | DR015  | 12 – 15, parity 3 |

#### **DM Option**

The DM option distributes the maintenance channel and routes the error logger channel and support channel to available CPUs. The DM option also contains the sanity code generator. Each IO module has one DM option.

# **Options on the CPU Module**

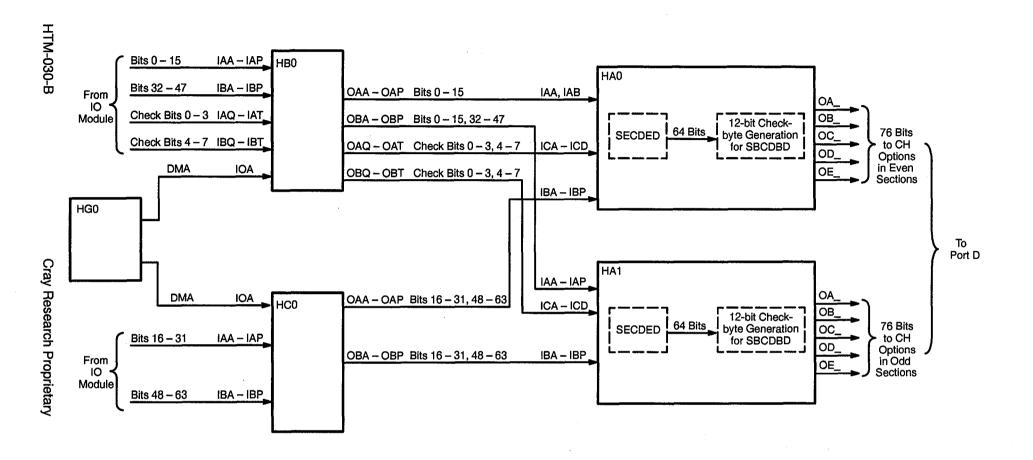

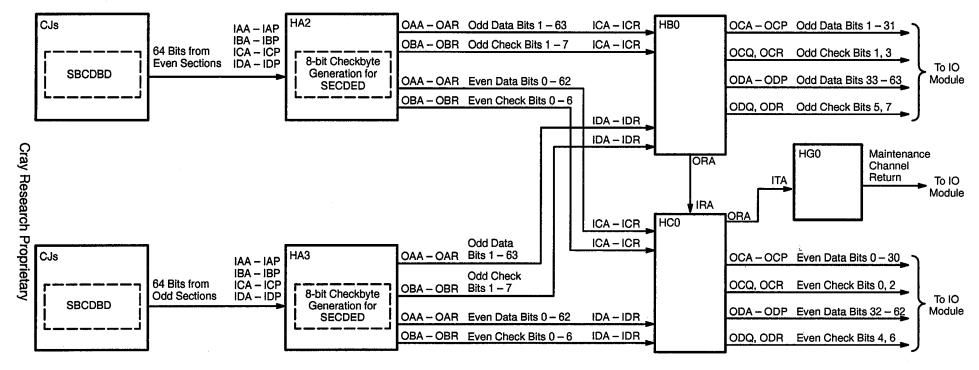

On the CPU module, the HA, HB, and HC option types perform I/O functions.

# **HA Option**

Four HA options (HA0 through HA3) reside on each CPU module. The HA options contain the input and output data buffers for read and write references. HA0 and HA1 serve as the write data buffers, and HA2 and HA3 contain the read data buffers. The HA options also perform error correction. During a write operation, the HA options receive a 72-bit word from the HB and HC options, and they perform SECDED. The 8 check bits are then stripped off, and a new 12-bit checkbyte is generated for SBCDBD. The HA options then pass the data to the CH options, which steer the data to the CI options (the section drivers).

During a read operation, the HA2 and HA3 options receive 64-bit data words from the CJ options and generate the checkbytes. The HA options send 72-bit words to the HB and HC options in two transfers.

#### **HB and HC Options**

Each CPU has one HB option and one HC option. The HB option controls the interface to the IO module module. During a memory write operation, the HB and HC options work in unison, each receiving 36 bits from the IO module.

During a read operation, the HB and HC options each receive data, in two 36-bit transfers, from two HA options. The HB option receives the odd bits; the HC option receives the even bits. The HB and HC options send the data to the IO module.

#### Connectors on the IO Module

The IO module uses three basic types of connections: the IO module-to-CPU module connection, the IO module-to-bulkhead connection, and the maintenance connection. The following paragraphs describe all three types of connections and their respective connectors.

#### **IO Module to CPU Module**

The IO module connects to the CPU modules through four OIM connectors. The IO module has four connection pads, which are labeled YA, YB, YC, and YD. Each connection pad connects to the YF pad of a CPU module. All CPU-I/O commands and I/O data pass through these connections.

#### **IO Module to Bulkhead**

The external channels physically connect to the IO module through an I/O connector harness. The I/O connector harness connects the IO module and the bulkhead. The connectors on the IO module side of the harness are sometimes referred to as *fuzz-button* connectors.

The IO module contains 16 I/O connectors: 8 on board 1 and 8 on board 2. There are five types of I/O connectors; each type has a unique part number. Types of connectors differ only in how they branch into the connections at the bulkhead. For example, one I/O connector may branch into ten 51-pin connectors, and another may branch into four 100-pin connectors. Refer again to Figure 4 and Figure 5 for more detailed information about the placement and characteristics of these connectors.

Each IO module is wired to one bulkhead. In a CRAY T932 system that has four IO modules, each module is wired to one of four bulkheads. External cabling starts from the bulkhead.

#### **Maintenance Connector**

The maintenance connector is located on the power regulator of the module. The maintenance connector is used to send and receive the following information to and from the module:

- Boundary scan signals TCLK, TM, TDI, TDO, and RCLCK

- OIM and SIM connector interlock signals

- Continuity line signals

- Thermal diode to output module temperature status

# **Channel Functions**

This section describes the functions of all the I/O channels in CRAY T90 series systems. It includes information on each type of LOSPX channel, as well as a description of the LOSP, HISP, and VHISP channels.

#### **LOSPX Channel**

The term LOSPX refers to a maintenance channel, support channel, an error logger channel, or MCU channel. Each IO module supports up to four LOSPX channels. The quadrant position on the IO module indicates the type of LOSPX channel. The support channel can operate in either LOSP or mid-speed (MISP) mode. The following paragraphs describe the four types of LOSPX channels.

#### **Maintenance Channel**

The maintenance channel provides a channel for performing the following CRAY T90 series system functions:

- Configuring the system

- Master clearing CPUs

- Master clearing memory

- Initializing the system

- Enabling and disabling sections of the system

- Monitoring system activity

- Selecting test points

- Initializing I/O resources

- Sending and controlling sanity codes

Each half of a CRAY T932 system can have a separate and independent maintenance channel if the system is logically and physically divided into two separate systems. Not all the maintenance ports on the IO modules in a CRAY T932 system are used. If one of the maintenance ports fails, the maintenance channel can be recabled to a different IO module; however, this recabling changes the system configuration.

The maintenance channel originates as a standard 6-Mbyte/s LOSP channel that is routed from the support system VME chassis, through the I/O bulkhead, and then to a maintenance port interface on one of the IO modules.

Refer to the document entitled *Maintenance Channel* for more information.

#### **Error Logger Channel**

The error logger channel in CRAY T90 series systems uses a standard 6-Mbyte/s LOSP channel. The LOSP portion of the error logger channel runs from an FEI-3 board in the system support VME chassis to one of the I/O bulkheads. From an I/O bulkhead, the LOSP error logger channel runs through a boundary scan module (normal operation) to an IO module. From the IO module, the serial error logger channel connects to the rest of the modules in the system. For more information, refer to the document entitled *Error Logger Channel*.

#### **Support Channel**

Each IO module contains eight LOSP channels, which are connected to IOS clusters. The support channel is the ninth LOSP that originates from the OWS. It provides a Transmission Control Protocol/Internet Protocol (TCP/IP) connection for system calls and can operate in either LOSP or MISP mode.

The support channel enters the IO module on the DD1 option. From there, the data is sent serially to the DM option. The DM option sends the serial data to one of four DA/DC options; each DA/DC option corresponds to one physically connected CPU.

#### MCU

The MCU interrupt has the capability to interrupt any or all CPUs at once. The CRAY T90 series system can target the interrupt to any combination of the four possible partitions. All CPUs are capable of receiving MCU interrupt.

The MCU channel enters the IO module via the bulkhead. It originates from the HCM quarter board within the IOS. The DD3 option contains a 16-bit register that is loaded by the maintenance channel at configuration time. From the DD3 option, the data is sent serially to the DM option. The DM option directs the data to one of four DE options. The DE option reassembles the data into 16-bit packets (interrupt request packet) and sends it to the shared module via the attached CPU.

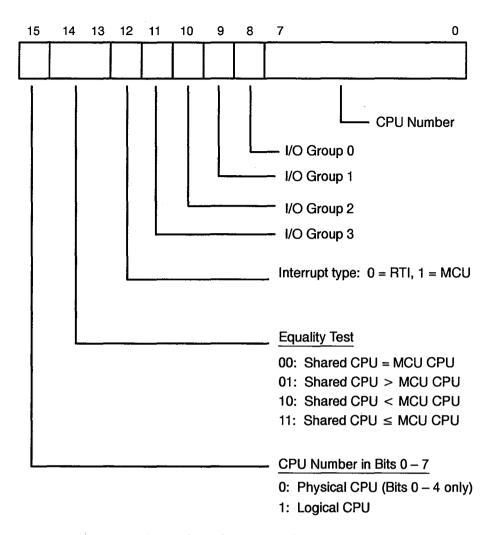

Figure 6 shows the bit assignments in the 16-bit register that is loaded from the maintenance channel. Bits 0 through 7 identify the CPU number, which can be either a physical or logical CPU number, as selected by bit 15. Bits 8 through 11 select the I/O group or groups that contain the CPUs to be interrupted. Bit 12 selects either a PINT or MCU interrupt. Currently, the PINT channel for real-time interrupts is not used.

Figure 6. MCU Channel Format

The equality test bits determine exactly which CPUs are interrupted. For example, bits 0 through 7 and bit 15 select physical CPU 5. If the equality test bits are 00, then physical CPU 5 gets the interrupt. If the equality test bits are 01, all CPUs numbered 6 and greater get the interrupt. If the equality test bits are 10, all CPUs numbered 4 and less get the interrupt. If the equality test bits are 11, all CPUs numbered 5 and less get the interrupt. This option provides the capability to interrupt all CPUs, which is done by setting the CPU number to the greatest number of CPUs in the system and setting the equality test bits to 11.

# **LOSP Channel**

The function of the LOSP channel is to connect the IOS to the system's CPU. The LOSP channel path is 20 bits wide (16 data bits and 4 parity bits). Odd parity is performed on the channel. All LOSP transfers are word transfers; 1 word consists of four 16-bit parcels. During a LOSP input sequence, a parity error causes all transfers to memory, following the word with the parity error, to be equal to zero. A LOSP-in parity error sets the Error flag but does not cause an interrupt. A LOSP channel interrupt is caused by a Disconnect signal from the connected device (CA = CL) or a fatal error.

The LOSP and support channels on CRAY T90 series systems can operate in either LOSP mode or MISP mode. MISP mode is selected with a software command and is described in greater detail later in this section.

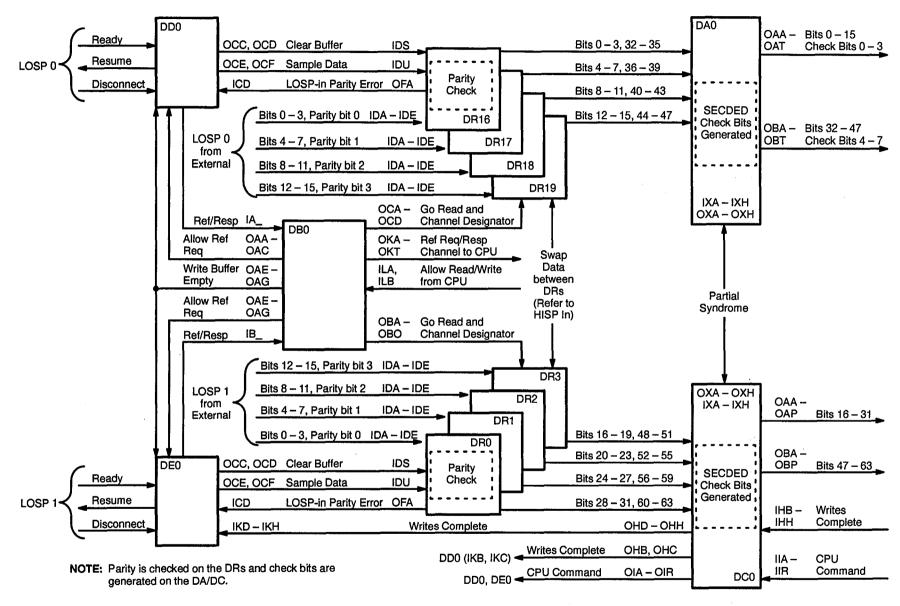

Figure 7 and Figure 8 illustrate the control and data paths and options associated with the LOSP channel input and output sequences.

Figure 7. LOSP 0 and 1 Input Control and Data

Figure 8. LOSP 0 and 1 Output Control and Data

# **LOSP Protocol**

The LOSP channel operates at 6 Mbytes/s and is similar to the LOSP channels in the CRAY Y-MP and CRAY C90 series computer systems. The data transfer is controlled by two signals: Ready and Resume. The Ready signal is sent with the data; the Resume signal is sent by the receiving device. Both the input and output channels use this protocol.

#### Ready Signal

The Ready signal is sent with each parcel of data. This signal indicates that the data on the data line is valid. The Ready signal is a 50-ns pulse.

# Data Lines 20 through 215

The data lines transmit 16-bit parcels of data between the transmitting and receiving devices. The channel samples data after the leading edge of the Ready signal is received. Data integrity is verified by 4 parity bits transmitted with the data.

#### Parity Bits

Parity bit signals 0 through 3 accompany each 16-bit parcel of data. Each of the four parity bit signals is assigned to one 4-bit group of data bits. The parity bits are set or cleared to give odd parity to the resulting 5-bit group (4 data, 1 parity).

#### Resume Signal

The receiving device sends the resume signal to the sending device to indicate that data has been received and that the receiving device is ready for another 16 bits of data. The Resume signal is a 50-ns pulse.

#### Disconnect Signal

The sending device sends the Disconnect signal to the receiving device to indicate the end of the transmission. The Disconnect signal deactivates the channel. When a channel is disconnected in the mainframe, an interrupt is generated (if the channel is enabled for interrupts).

#### **LOSP Channel Instructions**

Any CPU can request any LOSP channel to perform a read or write operation. The following list shows the sequence of the instructions issued.

- 0012j0 (Aj) is the channel number. The instruction issued clears any interrupts: clear error, clear done, and enable.

- 0011jk (Aj) is the channel number, and (Ak) is the channel limit address (CL).

- 0010jk (Aj) is the channel number, and (Ak) is the channel current address (CA). This instruction activates the channel.

Table 6 lists and explains all of the LOSP channel instructions for both read and write operations.

Table 6. LOSP Channel Instructions

| Machine<br>Instruction                   | CAL Syntax    | Input LOSP                                                                                                                                                                   | Output LOSP                                                                                                                                                                       |

|------------------------------------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0010 <i>jk</i>                           | CA,Aj Ak      | Set 35-bit CA<br>Start channel                                                                                                                                               | Set 35-bit CA<br>Start channel                                                                                                                                                    |

| 0011 <i>jk</i>                           | CL, Aj Ak     | Set 32-bit CL                                                                                                                                                                | Set 32-bit CL                                                                                                                                                                     |

| 0012 <i>j</i> 0                          | CI,Aj         | Clear interrupt<br>Clear error<br>Clear done<br>Enable interrupt                                                                                                             | Clear interrupt<br>Clear error<br>Clear done<br>Clear master clear<br>Enable interrupt                                                                                            |

| 0012 <i>j</i> 1                          | MC,A <i>j</i> | Clear interrupt<br>Clear error<br>Clear done<br>Clear ready held<br>Enable interrupt                                                                                         | Clear interrupt<br>Clear error<br>Clear done<br>Set master clear<br>Enable interrupt                                                                                              |

| 0012 <i>j</i> 2                          | DI,Aj         | Disable interrupt                                                                                                                                                            | Disable interrupt                                                                                                                                                                 |

| 0012 <i>j</i> 3                          | EI,Aj         | Enable interrupt                                                                                                                                                             | Enable interrupt                                                                                                                                                                  |

| 033 <i>i</i> 00                          | Ai Cl         | Transmit interrupting channel number to Ai                                                                                                                                   | Transmit interrupting channel number to Ai                                                                                                                                        |

| 033 <i>ij</i> 0                          | Ai CA,Aj      | Read CA                                                                                                                                                                      | Read CA                                                                                                                                                                           |

| 033 <i>ij</i> 1 A <i>i</i> CE,A <i>j</i> |               | Read status & errors Bits 0 – 28: 0 Bit 42: unexpected ready Bit 43: sequence error Bit 44: parity error Bit 45: DBE in mainframe Bit 46: Fatal error Bits 47 & 63: Not done | Read status & errors Bits 0 – 29: 0 Bit 42: extra Resume Bit 43: Disc. Resume detected Bit 44: Resume while active Bit 45: DBE on read Bit 46: Fatal error Bits 47 & 63: Not done |

#### I/O Commands

The DC option receives, from the CPU, four 16-bit packets that contain either the limit address register contents or the current address register contents along with the channel number, CPU number, and command bits 0 through 7. A Go I/O Command signal is sent with the first packet. These packets of data are routed through the DC option to both the DD option (for LOSP 0) or DE option (for LOSP 1). Table 7 describes the bit information for each of the four packets.

Because the DD and DE options handle both input and output for a LOSP channel, there are two channel limit registers and two channel current address registers per option.

The command codes interpreted by the DD or DE option are as follows:

• Command 11: enter CA

• Command 12: enter CL

• Command 14, 15, 16, and 17: clear interrupt

• Command 20: read current address

• Command 21: read error status

Table 7. DC Option I/O Command Packets

| Bit Position | 1st Packet | 2nd Packet | 3rd Packet           | 4th Packet           |

|--------------|------------|------------|----------------------|----------------------|

| Bit 00       | Ak data 00 | Ak data 16 | XX                   | Command bit 00       |

| Bit 01       | Ak data 01 | Ak data 17 | XX                   | Command bit 01       |

| Bit 02       | Ak data 02 | Ak data 18 | XX                   | Command bit 02       |

| Bit 03       | Ak data 03 | Ak data 19 | XX                   | Command bit 03       |

| Bit 04       | Ak data 04 | Ak data 20 | XX                   | Command bit 04       |

| Bit 05       | Ak data 05 | Ak data 21 | XX                   | Command bit<br>05    |

| Bit 06       | Ak data 06 | Ak data 22 | XX                   | Command bit 06       |

| Bit 07       | Ak data 07 | Ak data 23 | XX                   | Command bit 07       |

| Bit 08       | Ak data 08 | Ak data 24 | Channel number 00    | CPU number bit 00    |

| Bit 09       | Ak data 09 | Ak data 25 | Channel number 01    | CPU number<br>bit 01 |

| Bit 10       | Ak data 10 | Ak data 26 | Channel<br>number 02 | CPU number<br>bit 02 |

| Bit 11       | Ak data 11 | Ak data 27 | Channel<br>number 03 | CPU number<br>bit 03 |

| Bit 12       | Ak data 12 | Ak data 28 | Channel<br>number 04 | CPU number<br>bit 04 |

| Bit 13       | Ak data 13 | Ak data 29 | Channel<br>number 05 | CPU number<br>bit 05 |

| Bit 14       | Ak data 14 | Ak data 30 | Channel<br>number 06 | CPU number<br>bit 06 |

| Bit 15       | Ak data 15 | Ak data 31 | Channel<br>number 07 | CPU number<br>bit 07 |

# 50-Mbyte/s MISP Protocol

The LOSP channel and the support channel can run in MISP mode. A MISP channel operates at 50 Mbytes/s. MISP protocol, described below, is similar to the 6-Mbyte/s LOSP channel protocol.

#### **Ready Signal**

The Ready signal is a pulse 18.75 ns long. The Ready signal indicates to the channel that data transmission will follow on the data lines. Each ready pulse corresponds to a parcel of data.

# Data Lines 20 through 215

The data lines transmit 16-bit parcels of data between the transmitting and receiving devices. The channel typically samples data 37.5 ns after the leading edge of the appropriate Ready signal is received. Typically, data is sent 18.75 ns after the leading edge of the Ready signal pulse and remains valid for 37.5 ns.

#### **Parity Bits**

Parity bit signals 0 through 3 accompany each parcel of data. Each of the 4 parity bit signals is assigned to one 4-bit group of data bits. During a LOSP-out sequence, the parity is generated prior to sending the 16 bits of data to the external device.

#### **Resume Signal**

The Resume signal is a pulse 18.75 ns long. The receiver sends the Resume signal to the data transmitter, which indicates that parcel 0 of the transmitted word has been received and that the receiver is ready for the next full-word (64-bit) transfer. Each Resume signal corresponds to 4 parcels of data and 4 Ready signals. The final Resume signal of a transfer is an exception, however; it is issued in response to a Disconnect signal and can be sent only after the final word transfer is successfully stored.

#### **Disconnect Signal**

Like the Ready and Resume signals, the Disconnect signal is a pulse that is 18.75 ns long. The data transmitter sends a Disconnect signal to the receiver, which indicates that the transmission is complete. A Disconnect signal can be sent only after the last Resume signal for the last word of data is received by the transmitting device.

#### **Disconnecting Resume Signal**

The Disconnecting Resume signal reflects an error or interrupt condition in the receiving device. This signal disables channel communications between a receiver and a transmitter. It acts as a Master Clear signal to both the transmitter and receiver. The Disconnecting Resume signal uses the same wire as the Resume signal and is differentiated by the width of the signal. The Disconnecting Resume signal has a 56.25-ns pulse instead of the 18.75-ns pulse of a normal Resume signal.

## **HISP Channel**

Each IO module contains eight HISP channels. These channels are distributed across the four logical quadrants on an IO module. The HISP channels are referred to as HISP 0 and HISP 1 in quadrant 0, HISP 2 and HISP 3 in quadrant 1, HISP 4 and HISP 5 in quadrant 2, and HISP 6 and HISP 7 in quadrant 3.

A HISP channel operates at 200 Mbytes/s. A block of data in a HISP transfer consists of sixteen 72-bit words. Memory address and block length are transferred in five 12-bit packets from the master device to the mainframe. The block length register contains 16 bits; each bit represents a transfer of sixteen 72-bit words. The high-speed address register contains 32 bits. Table 8 lists the options that receive address and block length bits from the master device.

The mainframe operates as a slave device for a HISP transfer. There are no instructions that the mainframe issues that activate a HISP channel transfer; all channel transfers start from a master device such as the IOS-E.

Table 8. HISP Address and Block Length Options

| Channel       | Address Bits | Block Length Bits |

|---------------|--------------|-------------------|

| HISP 0 input  | DR000        | DR001             |

| HISP 0 output | DR018        | DR019             |

| HISP 1 input  | DR002        | DR003             |

| HISP 1 output | DR016        | DR017             |

| HISP 2 input  | DR004        | DR005             |

| HISP 2 output | DR022        | DR023             |

| HISP 3 input  | DR006        | DR007             |

| HISP 3 output | DR020        | DR021             |

| HISP 4 input  | DR008        | DR009             |

| HISP 4 output | DR026        | DR027             |

| HISP 5 input  | DR010        | DR011             |

| HISP 5 output | DR024        | DR025             |

| HISP 6 input  | DR012        | DR013             |

| HISP 6 output | DR030        | DR031             |

| HISP 7 input  | DR014        | DR015             |

| HISP 7 output | DR028        | DR029             |

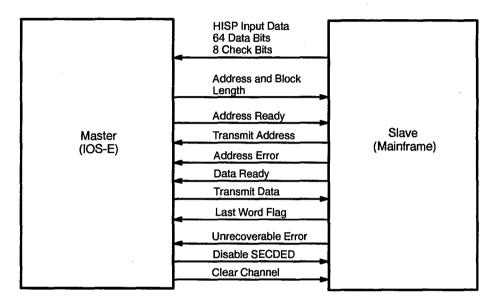

#### **HISP Input Sequence**

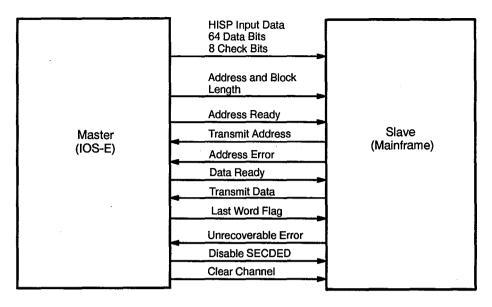

The IOS-E initiates a HISP transfer. The following exchange of control and data signals occurs between the IOS-E and the mainframe during a write operation. Figure 9 illustrates the exchange of control during the sequence.

- 1. Clear Channel: The Clear Channel signal clears the mainframe and enables it to receive data.

- 2. Transmit Address: The mainframe activates the Transmit Address signal when it can accept the address and block length. The mainframe deactivates the signal after it has received five Address Ready signals.

- 3. Address Ready: The Address Ready signal informs the mainframe that the IOS-E is sending the address and block length.

- 4. Address and Block Length: The IOS-E sends five packets that contain the address and block length. Each transfer accompanies an Address Ready signal. The five transfers consist of the following bits:

- First transfer: address bits 0 through 3 and 20 through 23; block length bits 0 through 3

- Second transfer: address bits 4 through 7 and 24 through 27; block length bits 4 through 7

- Third transfer: address bits 8 through 11 and 28 through 31; block length bits 8 through 11

- Fourth transfer: address bits 12 through 15 and 32 through 35; block length bits 12 through 15

- Fifth transfer: address bits 16 through 19 and 36 through 39; block length bits 16 through 19

- 5. Transmit Data: The mainframe sends a Transmit Data signal when it can accept 16 words of data from the IOS-E.

- 6. Data Ready: A Data Ready signal is sent to the mainframe with each 72-bit word of data from the IOS-E.

- 7. Steps 5 and 6 repeat until the last word of data is transferred.

- 8. Last Word flag: The Last Word Flag signal is sent from the IOS-E when the last word of data is sent. The Last Word Flag accompanies the Data Ready signal on the last word.

- 9. Done flag: The Done flag is set within the IOS-E to indicate that the block length is zero and no errors have occurred.

Figure 9. HISP Input Sequence

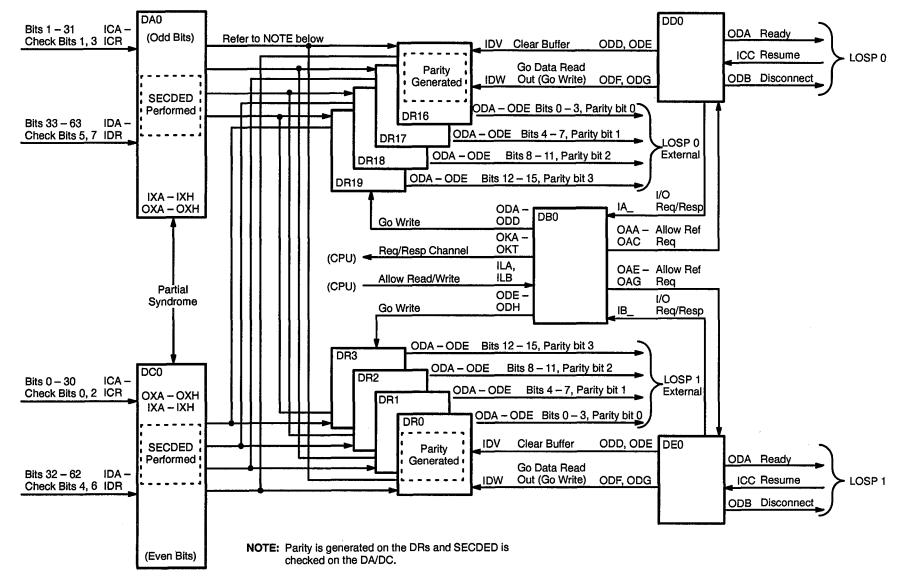

Figure 10 is a block diagram of the data flow through the options during an input sequence. Figure 11 illustrates the control signal, address, and block length flow through the options on the IO module during an input sequence.

Figure 10. HISP 0 Input Data

Figure 11. HISP 0 Input Control and Address

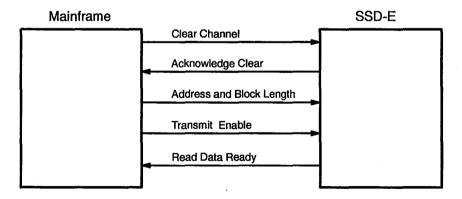

#### **HISP Output Sequence**

The IOS-E initiates a HISP transfer. The following exchange of control and data signals occurs between the IOS-E and the mainframe during a read operation. Figure 12 illustrates the exchange of control that takes place during an output sequence.

- 1. Clear Channel: The Clear Channel signal clears the mainframe and enables it to receive data.

- 2. Transmit Address: The mainframe activates the Transmit Address signal when it can accept the address and block length. The mainframe deactivates the signal after it has received five Address Ready signals.

- 3. Address Ready: The Address Ready signal informs the mainframe that the IOS-E is sending the address and block length.

- 4. Address and Block Length: The IOS-E sends five packets that contain the address and block length. Each transfer accompanies an Address Ready signal. The five transfers consist of the following bits:

- First transfer: address bits 0 through 3 and 20 through 23; block length bits 0 through 3

- Second transfer: address bits 4 through 7 and 24 through 27; block length bits 4 through 7

- Third transfer: address bits 8 through 11 and 28 through 31; block length bits 8 through 11

- Fourth transfer: address bits 12 through 15 and 32 through 35; block length bits 12 through 15

- Fifth transfer: address bits 16 through 19 and 36 through 39; block length bits 16 through 19

- 5. Transmit Data: The IOS-E sends a Transmit Data signal when it can accept 16 words of data from the mainframe.

- 6. Data Ready: A Data Ready signal is sent to the IOS-E with each 72-bit word of data from the mainframe.

- 7. Steps 5 and 6 repeat until the last word of data is transferred.

- 8. Last Word Flag: The Last Word Flag signal is sent to the IOS-E when the last word of data is sent. The Last Word Flag accompanies the Data Ready signal on the last word.

- 9. Done flag: The Done flag is set within the IOS-E to indicate that the block length is 0 and no errors have occurred.

Figure 12. HISP Output Sequence

Figure 13 illustrates the control signal, address, and block length flow through the options on the IO module during an output sequence. Figure 14 is a block diagram of the data flow through the options during an output sequence.

Figure 13. HISP 0 Output Control and Address

Figure 14. HISP 0 Output Data

## **HISP Errors**

Certain error conditions can occur during HISP channel activity. Some errors terminate the transfer; others do not. Table 9 lists and describes the HISP errors.

Table 9. HISP Errors

| Error                                                                    | Description                                                                                                                                                                                                                                |

|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Address channel parity error                                             | A parity error was detected on the DR option receiving memory address and/or block length. This error terminates the transfer.                                                                                                             |

| Extra Address Ready signal                                               | An Address Ready signal was detected after the fifth address/block length transfer. This error terminates the transfer.                                                                                                                    |

| Address Ready signal without<br>Transmit Address signal                  | An Address Ready signal was detected but the mainframe had not sent the Transmit Address signal. This error terminates the transfer.                                                                                                       |

| Missing Address Ready signal                                             | A Data Ready signal was detected between the 1st and 5th address/block length transfer. This error terminates the transfer.                                                                                                                |

| SECDED error detected on read data from CPU or write to CPU              | For a read operation, an error occurred on the DA/DC options while data was en route from the CPU to the DR options. For a write operation, an error occurred on the DA/DC options while data was en route to the CPU.                     |

| SECDED error on CPU write buffers                                        | Unrecoverable memory error signal.                                                                                                                                                                                                         |

| SBCDBD error on CPU Read                                                 | Unrecoverable memory error signal.                                                                                                                                                                                                         |

| Clear Channel signal and reference pending                               | If a Clear Channel signal arrives and there is a pending write reference to the CPU, an error condition occurs to ensure the channel does not try a new transfer until the reference is completed. This error terminates the transfer.     |

| Clear Channel signal and no<br>HISP writes complete signal               | If a Clear Channel signal arrives and there is a pending write reference to the CPU, an error condition occurs to ensure that the channel does not try a new transfer until the reference is complete. This error terminates the transfer. |

| Last Word Flag signal and Block<br>Length ≠ 00                           | The Last Word Flag signal was detected but the block length register did not equal 0. This error terminates the transfer.                                                                                                                  |

| No Last Word Flag signal and<br>Block Length = 00                        | The Block Length register equals 0 but no Last Word Flag signal is detected. This error terminates the transfer.                                                                                                                           |

| Last Word Flag signal and Block<br>Length = 00 and another Data<br>Ready | The Last Word Flag signal was received and the Block Length register equals 0 and another Data Ready signal is detected. This error terminates the transfer.                                                                               |

## **VHISP Channel**

Each IO module contains four VHISP channels. A fully configured CRAY T90 series system can include 16 VHISP channels. Each VHISP channel is identified by a specific channel number.

A VHISP transfer is under the direct control of the mainframe. The SSD-E is the slave device; the mainframe is the master device. Any CPU can request either a VHISP read from the SSD-E or write to the SSD-E using any VHISP channel.

#### **VHISP Instructions**

Table 10 lists the VHISP instructions.

Table 10. VHISP Instructions

| Machine Instruction | Cal Syntax               | Function                                                                                                                                                                                                                                                   |  |  |

|---------------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 0010 <i>jk</i>      | CA,Aj Ak                 | Set CA (first sends 32-bit SSD address, second sends 32-bit CPU address)                                                                                                                                                                                   |  |  |

| 0011 <i>jk</i>      | CL,A <i>j</i> A <i>k</i> | Set BL and start channel Bits 0 – 23: BL Bit 31: transfer direction Bit 24 and 25: reserved                                                                                                                                                                |  |  |

| 0012 <i>j</i> 0     | CI,Aj                    | Clear interrupt Clear channel sequence Clear error status Clear done Clear interrupt                                                                                                                                                                       |  |  |

| 0012 <i>j</i> 2     | DI,Aj                    | Disable interrupt                                                                                                                                                                                                                                          |  |  |

| 0012 <i>j</i> 3     | El,Aj                    | Enable interrupt                                                                                                                                                                                                                                           |  |  |

| 033i00              | Ai Cl                    | Transmit interrupting channel number to Ai                                                                                                                                                                                                                 |  |  |

| 033 <i>ij</i> 0     | Ai CA,Aj                 | Read CA                                                                                                                                                                                                                                                    |  |  |

| 033 <i>ij</i> 1     | Ai CE,Aj                 | Read status and errors Bits 0 – 23: remaining BL Bits 24 – 41: 0 Bit 42: transfer in progress Bit 43: BL error Bit 44: double-bit error in SSD Bit 45: double-bit error in mainframe Bit 46: fatal error Bit 47: not done Bits 48 – 62: 0 Bit 63: not done |  |  |

The 001000 instruction is a pass (no-operation) instruction. The 0010jk ( $jk \neq 0$ ) and 0011jk instructions initiate a channel transfer. For a VHISP channel, the 0010jk must be issued twice, followed by instruction 0011jk. The first 0010jk instruction sets the starting block address in the SSD-E. The second 0010jk instruction sets the channel address (CA) in the mainframe. The 0011jk instruction sets the block length (BL) and starts the transfer.

#### VHISP Addressing

When the VHISP channel is online, the mainframe supplies the SSD-E address and block length for read or write operations. The address and block length are sent from the DR options. The DR options listed in the table refer only to quadrant 0 of the IO module.

The mainframe sends 32 address bits that are loaded into the address register of the SSD-E. The mainframe also sends 32 block length bits to the SSD-E. The SSD-E defines a block of data to be 32 words, whereas the mainframe defines a block of data as 64 words.

### **VHISP Input Sequence**

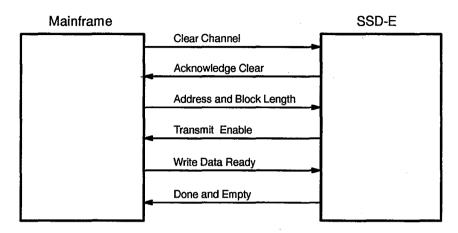

The following exchange of control and data takes place during a read to the mainframe. The mainframe (master) initiates the read operation.

- 1. Clear Channel: The mainframe sends the Clear Channel signal to the SSD-E to clear and initiate the VHISP channel.

- 2. Clear Acknowledge: Once the SSD-E has cleared the channel, it returns the Clear Acknowledge signal.

- 3. Address and Block Length: The mainframe sends address and block length bits to the SSD-E.

- 4. Transmit Enable: The mainframe sends this signal to the SSD-E to indicate that it has an empty buffer ready to be filled.

- 5. Read Data Ready: The SSD-E sends this signal once for every 16 144-bit words.

- 6. Data: Data leaves the SSD-E 144 bits at a time (72 bits for even word and 72 bits for odd word).

- 7. Steps 4, 5, and 6 continue until the last word of the last block is sent by the SSD-E.

Figure 15 illustrates the exchange of control that takes place during a VHISP input sequence.

Figure 15. VHISP Input Control Signals

# **VHISP Input Data Path**

The DR options receive input data from the SSD-E. Both an even and an odd word (72 bits each) are received. The DR options for quadrant 0 of the IO module are DR16 through DR19. The even word is received on IBA through IBR, and the odd word is received on ICA through ICR. Figure 16 shows the flow of data and control during a VHISP input sequence.

Figure 16. VHISP 0 Input Control and Data

#### **VHISP Output Sequence**

The following exchange of control and data takes place during a read from mainframe memory. The mainframe (master) initiates the read operation.

- 1. Clear Channel: The mainframe sends the Clear Channel signal to the SSD-E to clear and initiate the VHISP channel.

- 2. Acknowledge Clear: Once the SSD-E has cleared the channel, it returns the Clear Acknowledge signal.

- 3. Address and Block Length: The mainframe sends address and block length bits to the SSD-E.

- 4. Transmit Enable: The mainframe sends this signal to the SSD-E to indicate that it has an empty buffer ready to be filled.

- 5. Read Data Ready: The SSD-E sends this signal once for every 16 144-bit words.

- 6. Data: Data leaves the SSD-E 144 bits at a time (72 bits for even word and 72 bits for odd word).

- 7. Steps 4, 5, and 6 continue until the last word of the last block is sent by the SSD-E.

Figure 17 illustrates the exchange of control that takes place during a VHISP read function.

Figure 17. VHISP Output Control Signals

Figure 18 shows the flow of data and address/block length during a VHISP output sequence.

Figure 18. VHISP 0 Output Control and Data

## **VHISP Errors**

A number of conditions can occur during a VHISP reference that cause VHISP channel errors. Some errors terminate the channel transfer; others do not. Table 11 describes the VHISP channel errors.

Table 11. VHISP Channel Errors

| Error                                            | Description                                                                                                                                                          |  |  |

|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| No Last Word and block length = 0                | During transfer from mainframe to SSD, the SSD does not receive Last Word Flag signal, but the block length is 0. This error terminates the transfer.                |  |  |

| Done and Empty and block length ≠ 0              | During transfer from SSD to mainframe, the mainframe receives the Done and Empty signal, but block length is not zero. This error terminates the transfer.           |  |  |

| Done signal is set, Done and<br>Empty is not set | During a transfer from SSD to mainframe, the Done flag sets, but the mainframe does not receive the Done and Empty signal. This error terminates the transfer.       |  |  |

| Done and Empty is set, but no<br>Last Word flag  | During a transfer from mainframe to SSD, the Done and Empty flag sets, but the mainframe has not sent the Last Word Flag signal. This error terminates the transfer. |  |  |

| Fatal Error                                      | Caused by an OR condition of all above errors or an outstanding reference. This error terminates the transfer.                                                       |  |  |

| SECDED error on SSD during a read or write       | The SSD detected a data error. If it is a single bit, it is corrected. If a double- or multiple-bit error has occurred, the transfer is terminated.                  |  |  |

| SECDED error on mainframe during a read or write | The CPU detected a data error. If it is a single bit, it is corrected. If a double- or multiple-bit error has occurred, the transfer is terminated.                  |  |  |

| SBCDBD error during CPU read                     | The CPU detected a data error. If it is a single byte, it is corrected. If a double- or multiple-byte error has occurred, the transfer is terminated.                |  |  |

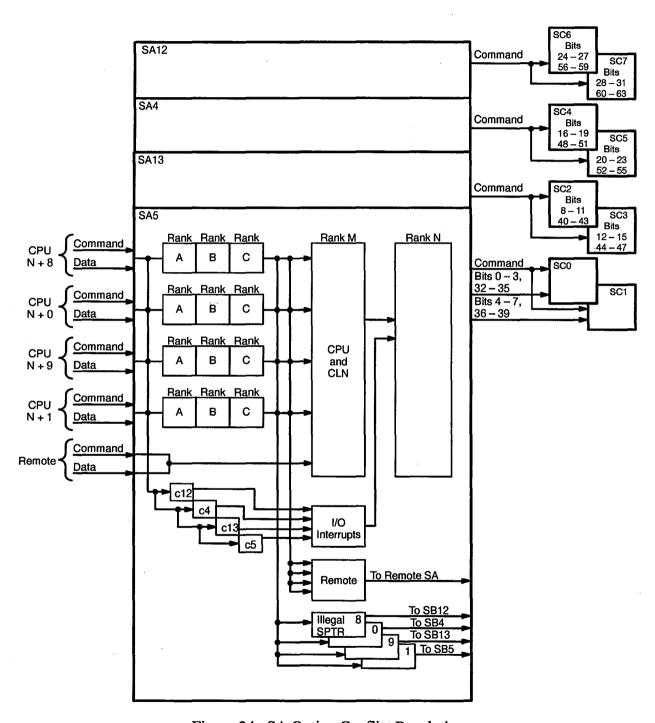

# I/O Data Path through the CP Module

Any I/O data that is read from or written to memory must pass through the CP module. This is necessary because the IO module does not have a direct physical connection to memory; it uses the CPU's port D path into memory. The following paragraphs decribe the write and read paths through the CP module. Refer to Figure 19 and Figure 20, which follow the text.

# I/O Write Path through the CP Module

During an I/O write sequence, the data leaves the IO module on a 72-bit path: 64 data bits, and 8 checkbits for SECDED. The data enters data buffers in the HB and HC options on the CP module. The HB and HC options send the data in two 36-bit transfers to the HA0 and HA1 options.

The HA options first perform SECDED on the data; then they generate a 12-bit checkbyte for single-byte correction/double-byte detection (SBCDBD). The HA0 option sends the 76-bit words to the CH options for even memory sections; the HA1 option sends the 76-bit words to the CH options for odd sections of memory.

The maintenance channel also has a path into the HB options, which is used during DMA transfers into memory. The maintenance channel path is a serial path into the HB and HC options. The HB and HC options assemble the serial data into 64-bit word format; each option handles half the data bits for the word. The HB option generates the SECDED checkbyte for the entire word.

# I/O Read Path through the CP Module

During an I/O read sequence, the CJ options in the CPU perform SBCDBD. Then the CJ options send the 64-bit data word to the HA2 and HA3 options, where an 8-bit checkbyte is generated for SECDED. The HA options send the data to the buffers on HB0 and HC0 options; HB0 receives the odd bits, and HC0 receives the even bits. The HB and HC options send the 72-bit words to the IO module.

During a maintenance channel read of memory, the data enters the HB and HC options as does any other I/O data. The HB option sends its odd data bits in a serial stream to the HC option. The HC injects its even bits into the serial stream and sends it to the HG option. From the HG option, the maintenance channel data follows the regular maintenance channel path back to the IO module.

Figure 19. CPU Options – Write (IO to Memory)

NOTE: The terms OAA, OAC, OAE, etc., go to the HB0 option. The terms OAB, OAD, OAF, etc., go to the HC0 option. The terms OBA, OBC, OBE, etc., go to the HB0 option. The terms OBB, OBD, OBF, etc., go to the HC0 option.

Figure 20. CPU Options – Read (Memory to IO)

HTM-030-B

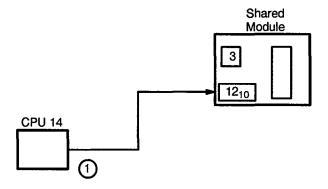

# I/O Logic on Shared Module

All I/O channel request information follows a path from the issuing CPU, to the local shared module, and finally to the IO module through the CPU that is connected to the IO module that services the requested channel, as shown in Figure 21. If the local shared module determines that the requested channel is on the other physical half of the chassis, it forwards the channel request to the remote shared module. The remote shared module then sends the information to the appropriate CPU module on that half of the chassis.

Figure 21. Channel Request Information Flow

# **Acronyms**

The engineering documentation uses several acronyms to identify signals and commands used in the shared module. The following list defines these acronyms. Not all of these are used for an I/O instruction.

- CCMD CPU shared command

- CMD shared command

- SPTR steering pointer

- RPTR register pointer

- SCPU source CPU

- DCPU destination CPU

- EDCPU effective destination CPU (from channel number)

- ECLN effective CLN (from CLN+partition)

- MM/UM monitor mode/user mode

- T&S test and set

- DLI deadlock interrupt

#### **Shared Module Ports**

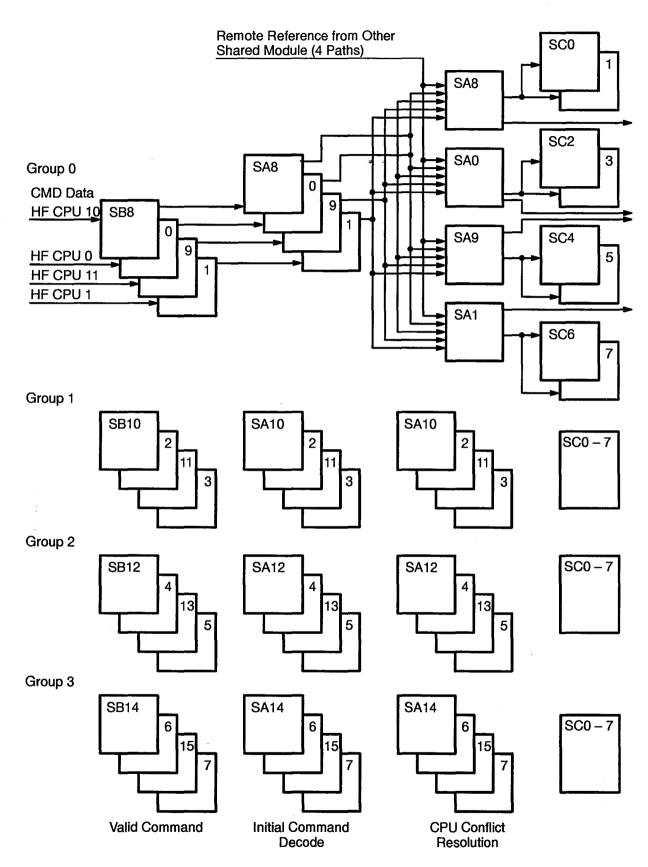

The shared module is divided into ports, and the ports are then grouped. There are 16 ports on each shared module, one for each of the 16 CPUs that connect to it. The ports are numbered in octal. Each port contains both an SA and an SB option. The ports are divided into four groups for the passing of information and data. Group 0 contains ports 10, 0, 11, and 1; Group 1 contains ports 12, 2, 13, and 3; Group 2 contains ports 14, 4, 15, and 5; and Group 3 contains ports 16, 6, 17, and 7.

Figure 22 shows the grouping of the ports within the shared module. Group 0 is expanded in the diagram to show the data and command flow from each port within the group to the other ports within that group.

Figure 22. Shared Module Port/Group Designation

# **Shared Module Options**

The following paragraphs describe the shared module options that are involved in I/O activity.

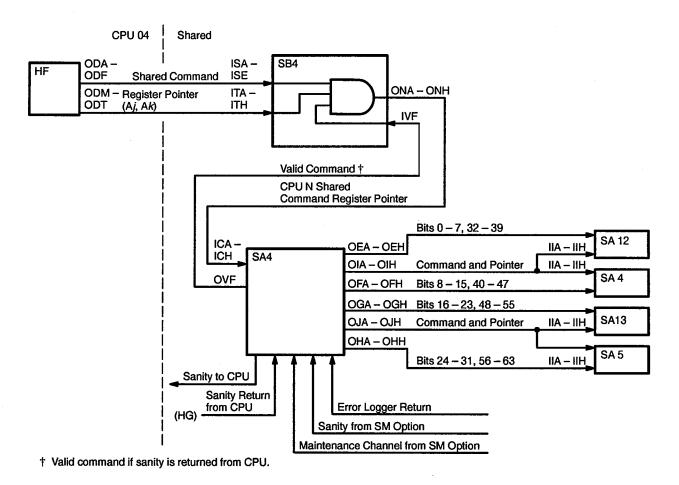

## **SA Option**

There are 16 SA options, numbered SA00 through SA15, on the shared module. The SA option is one of two options that make up the 16 ports located on the module. This option decodes the channel number requested during an I/O instruction and generates the effective destination CPU (EDCPU) code and the steering pointer (SPTR) code.

### **SB Option**

There are 16 SB options located on the shared module, which are numbered SB00 through SB15. The SB option is the second of two options that make up the 16 ports located on the module. The SB option passes data and command information to the CPU that will service the I/O channel request.

The SB option receives the initial command code for an I/O request and, once the code is validated, sends the information to the SA option.

#### **SC Option**

There are 8 SC options used within the shared module, SC0 through SC7. The SC option performs functions related to channel interrupts and the real-time clock (RTC). During an I/O request, the SC option routes data to the SD option.

Channel interrupt and the SIE scoreboard are held in SC00. SC00 synchronizes RTC broadcasts with the remote shared module.

### **SD Option**

There are 16 SD options on the shared module, numbered SD00 through SD16. The SD option routes data and command information to the CPU port that services the I/O request. Data and command information is routed to the correct port via the steering pointer code generated on the SA option.

## **Shared Command Codes**