# **CPU MODULE (CP02)**

| CP02 MODULE       |                                              | 1  |

|-------------------|----------------------------------------------|----|

|                   | CP02 General Description                     | 1  |

|                   | Module Assembly Components                   | 2  |

| ADDRESS AND SCA   | LAR REGISTERS                                | 7  |

|                   | Address Registers                            | 7  |

|                   | Entry Codes                                  | 9  |

|                   | A Register Memory References                 | 11 |

|                   | Special Register Values                      | 11 |

|                   | Scalar Registers                             | 13 |

|                   | Instruction Issue                            | 13 |

|                   | S Register Memory References                 | 13 |

|                   | Special Register Values                      | 14 |

|                   | Lower/Upper Scalar Register Load             | 14 |

| B AND T REGISTERS | <u>s</u>                                     | 15 |

| ADDRESS/SCALAR    | ADD                                          | 19 |

| SCALAR LOGICAL    |                                              | 21 |

|                   | Address and Scalar Mask                      | 23 |

|                   | Transmit <i>nm</i> to Si, Si Upper, Si Lower |    |

| ADDRESS/SCALAR    | POP/PARITY AND LEADING ZERO                  | 27 |

| ADDRESS REGISTER | SHIFT                                    | 31     |

|------------------|------------------------------------------|--------|

|                  | Address Register Single Shift            | 33     |

|                  | Address Register Double Shift            | 33     |

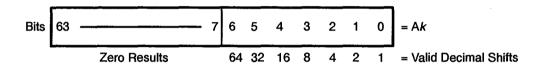

|                  | Address Register Shift Count Description | 34     |

|                  | Address Register Left Single Shift       | 35     |

|                  | Address Register Right Single Shift      | 36     |

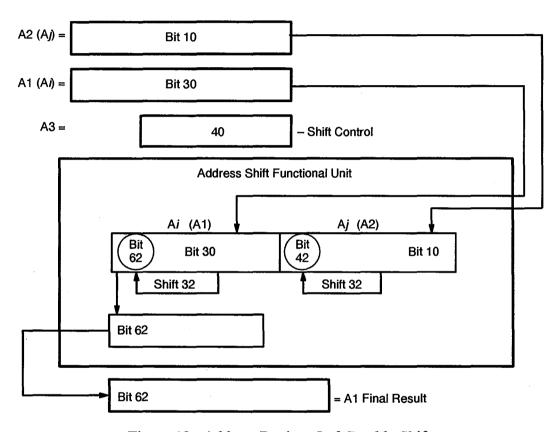

|                  | Address Register Left Double Shift       | 37     |

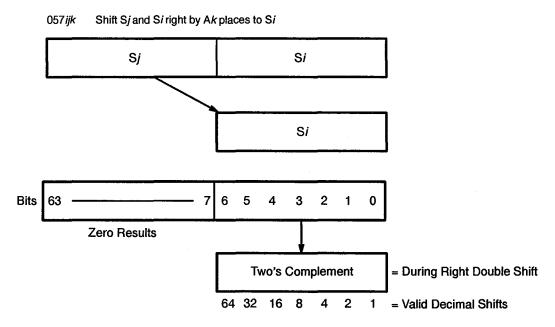

|                  | Address Register Right Double Shift      | 38     |

|                  | Left Single-shift Instruction            | 39     |

|                  | Right Single-shift Instruction           | 40     |

|                  | Left Double-shift Instruction            | 41     |

|                  | Right Double-shift Instruction           | 42     |

| SCALAR SHIFT     |                                          | 43     |

|                  | Scalar Single Shift                      | <br>45 |

|                  | Scalar Double Shift                      | 45     |

|                  | Scalar Shift Count Description           | 46     |

|                  | Scalar Left Single Shift                 | 47     |

|                  | Scalar Right Single Shift                | 48     |

|                  | Scalar Left Double Shift                 | 49     |

|                  | Scalar Right Double Shift                | 50     |

|                  | Left Single-shift Instruction            | 51     |

|                  | Right Single-shift Instruction           | 52     |

|                  | Left Double-shift Instruction            | 53     |

|                  | Right Double-shift Instruction           | 54     |

| ADDRESS MULTIPLY |                                          | 55     |

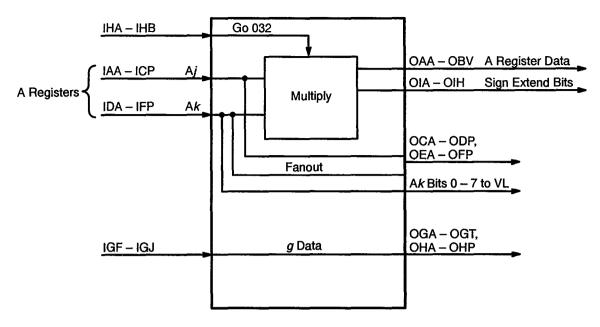

|                  | Multiply Algorithm                       | 56     |

|                  | Standard Binary Multiplication           | 57     |

|                  | Booth Recode Multiplication              | 57     |

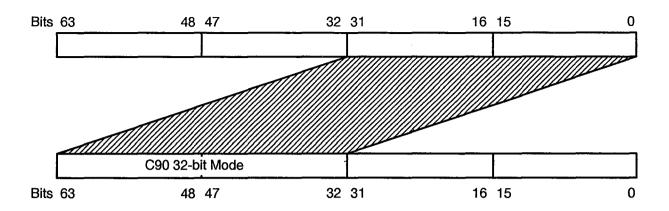

| INTEGER MULTIPLY |                                          | 59     |

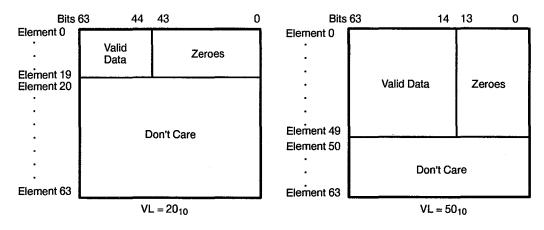

| VECTOR REGISTER | IS                                        | 63  |

|-----------------|-------------------------------------------|-----|

|                 | VA Option                                 | 65  |

|                 | Vector Length Register                    | 65  |

|                 | Chaining                                  | 66  |

|                 | VF Option                                 | 66  |

|                 | VM Option                                 | 67  |

|                 | VR Option                                 | 67  |

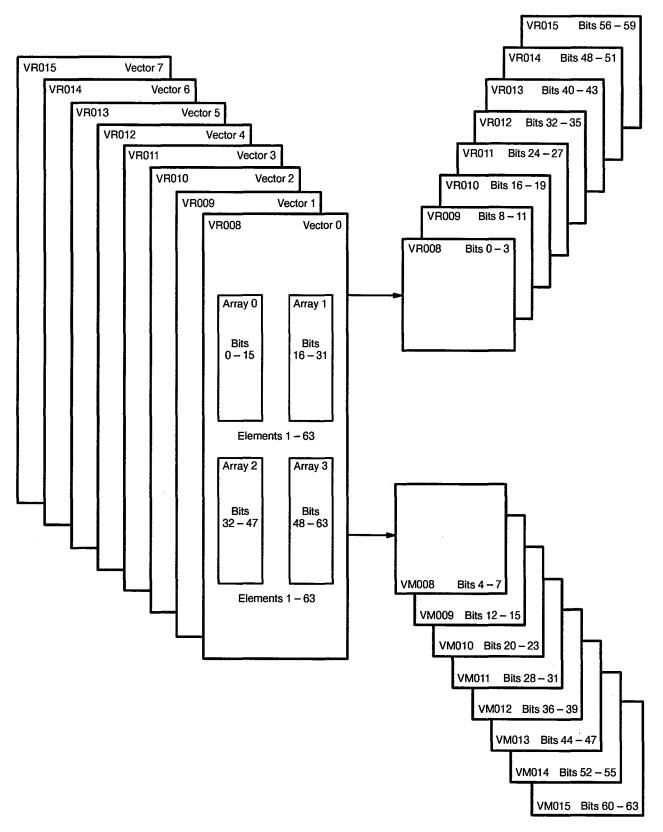

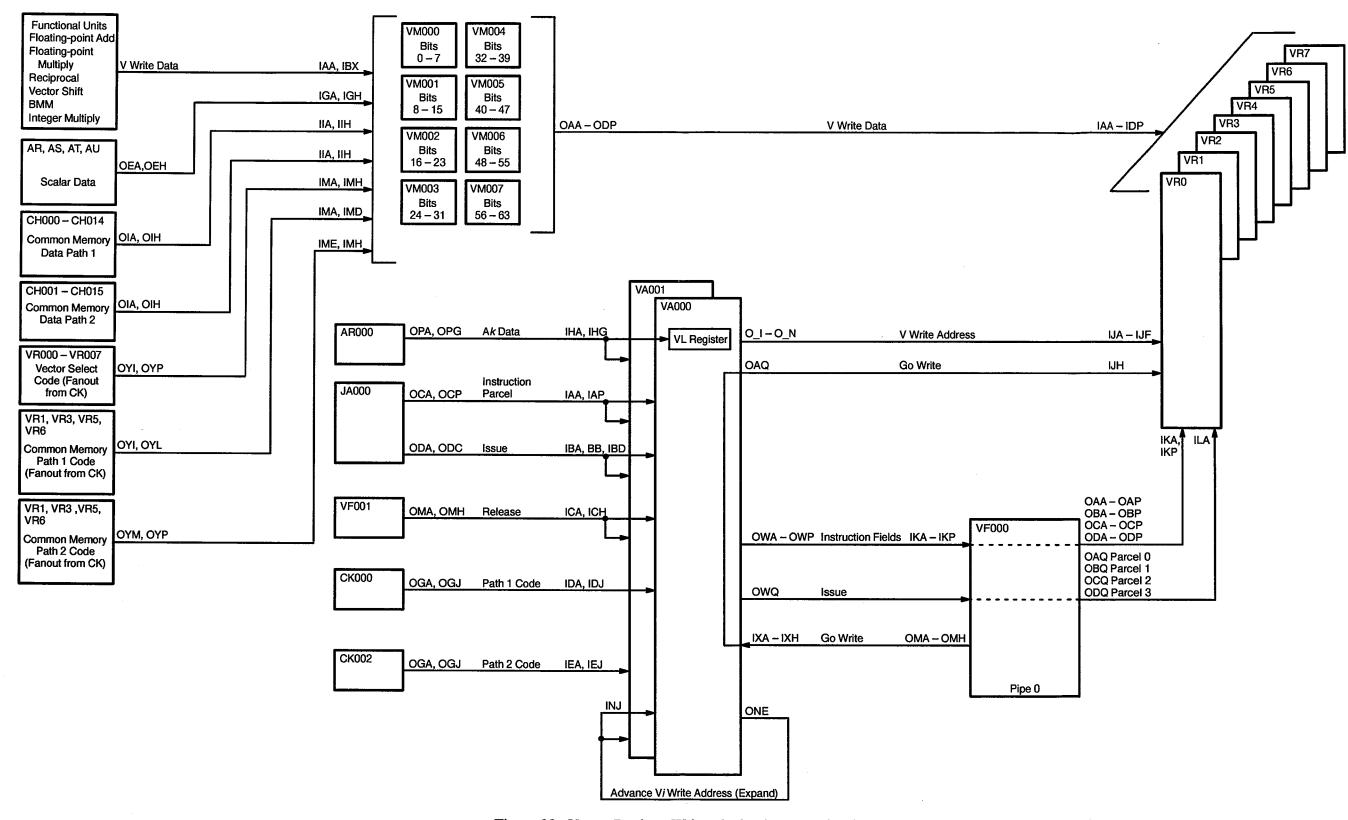

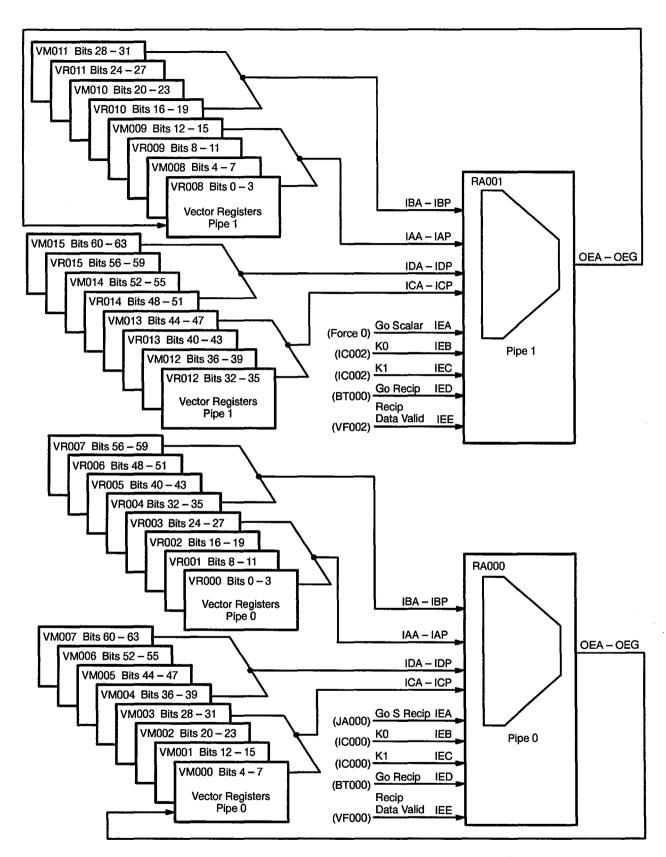

|                 | Write Data Steering                       | 68  |

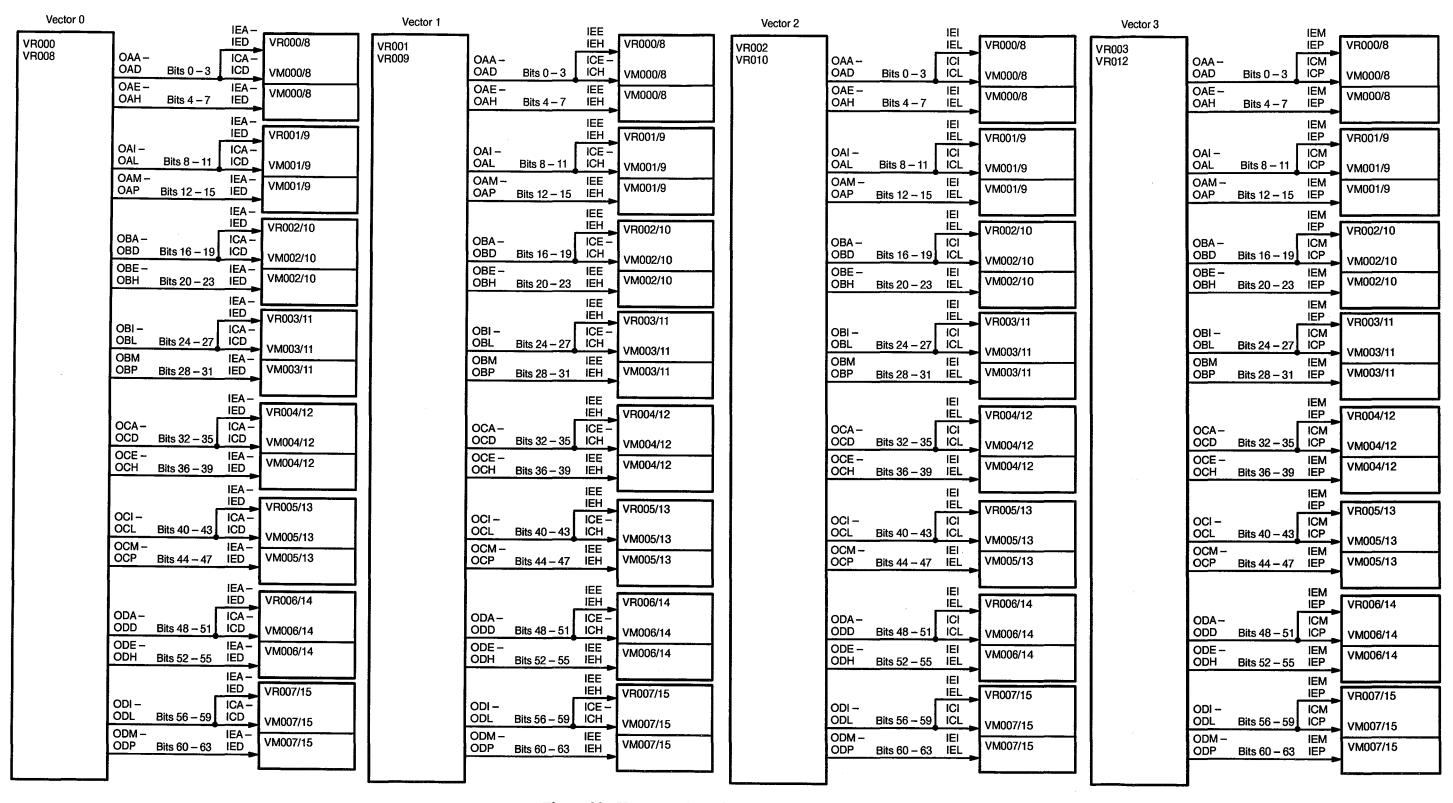

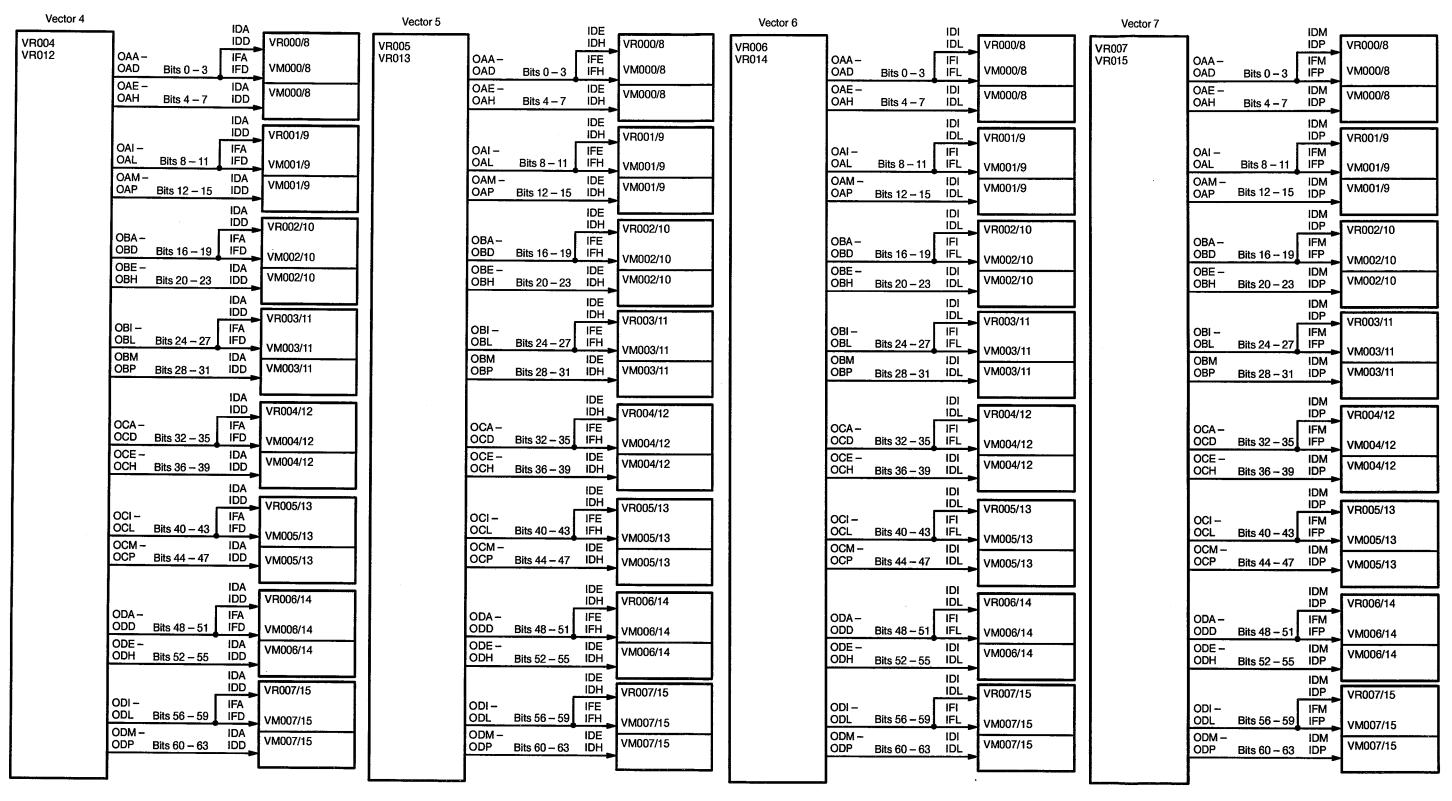

|                 | Read Data Steering                        | 70  |

| VECTOR LOGICAL  |                                           | 93  |

|                 | Vector Logical Instructions               | 95  |

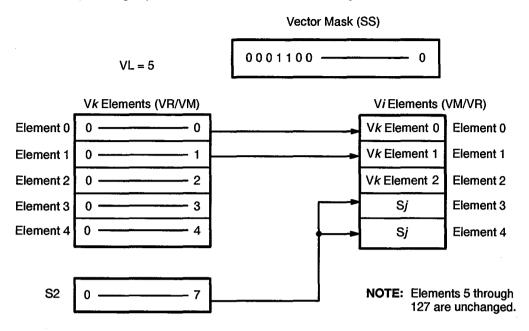

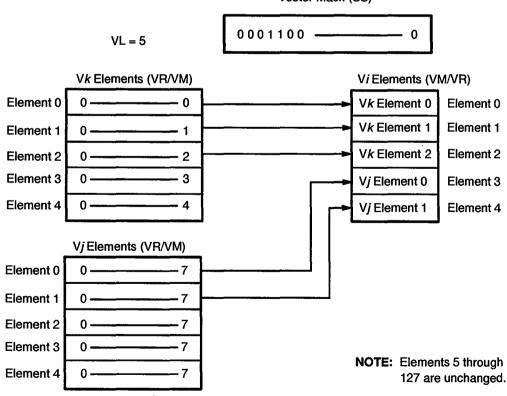

|                 | Vector Merge                              | 95  |

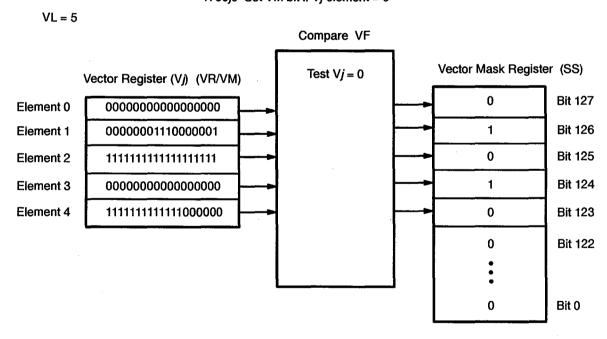

|                 | Vector Mask                               | 98  |

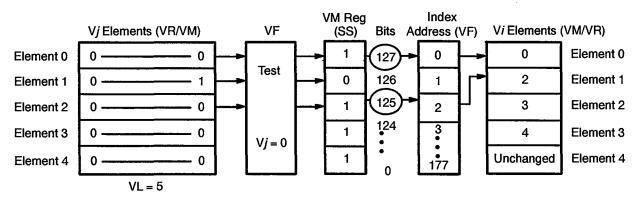

|                 | Compressed Iota                           | 100 |

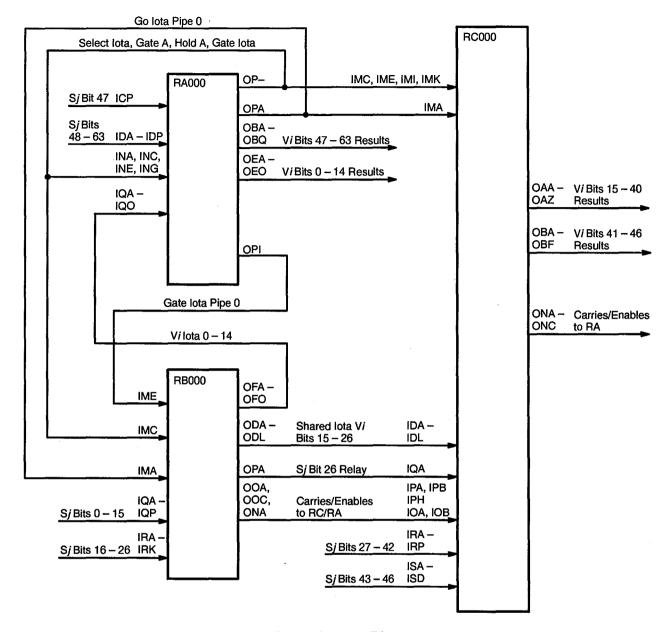

|                 | RA Option                                 | 101 |

|                 | RB Option                                 | 102 |

|                 | RC Option                                 | 102 |

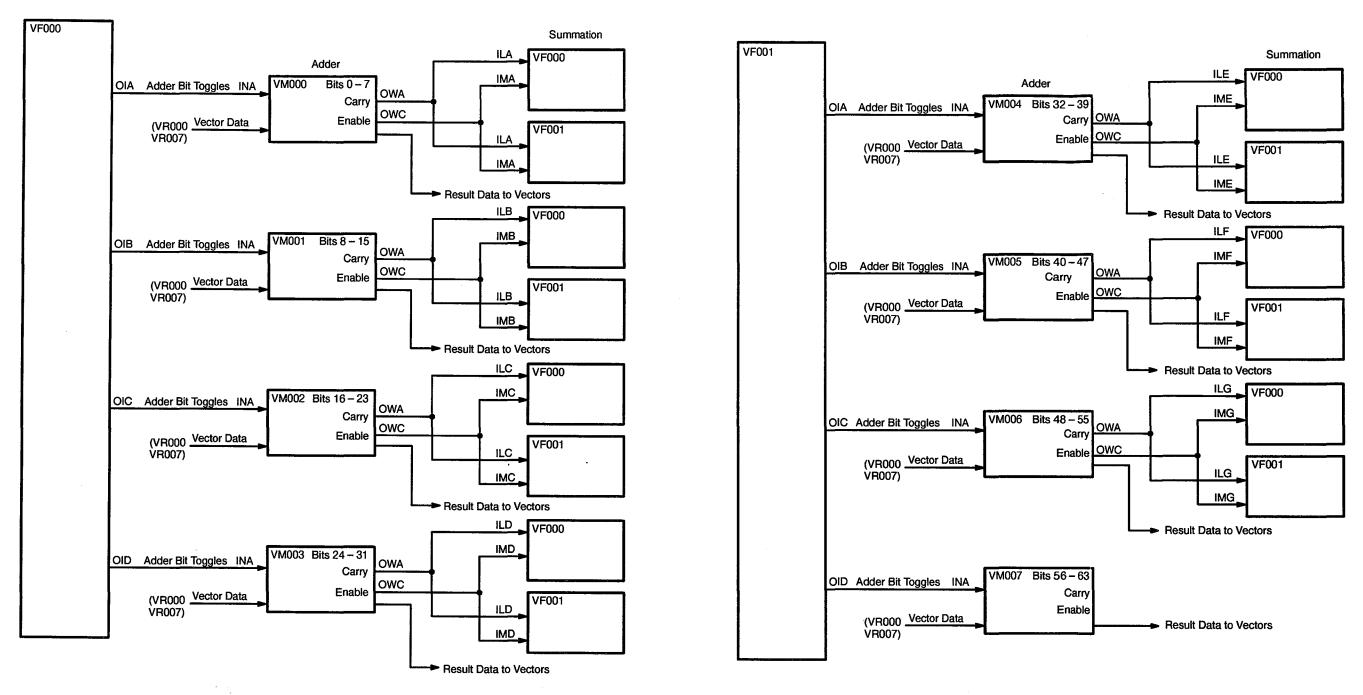

| VECTOR ADD      |                                           | 103 |

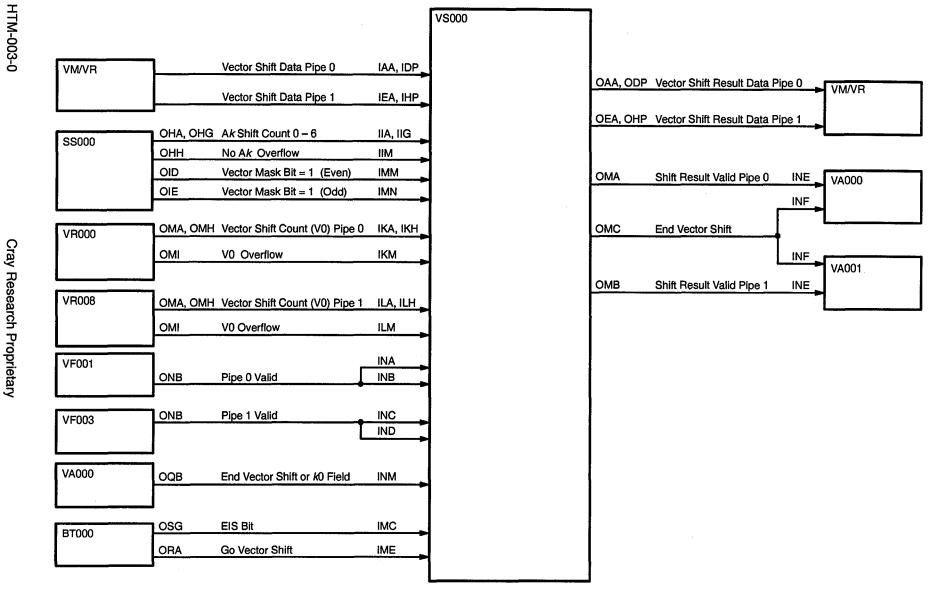

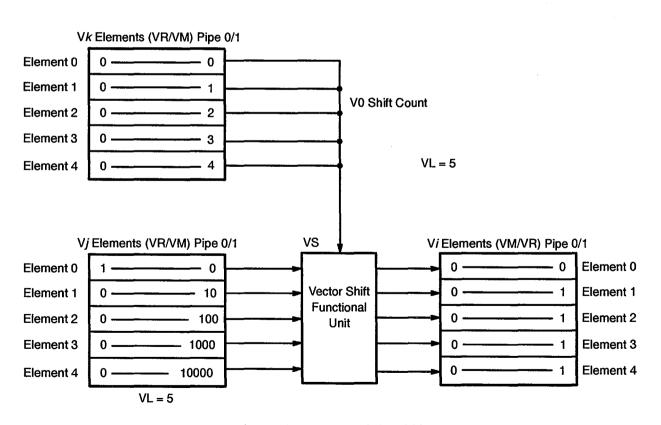

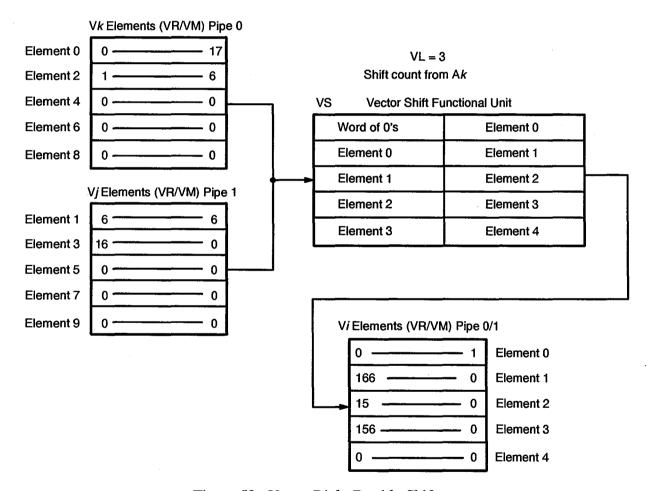

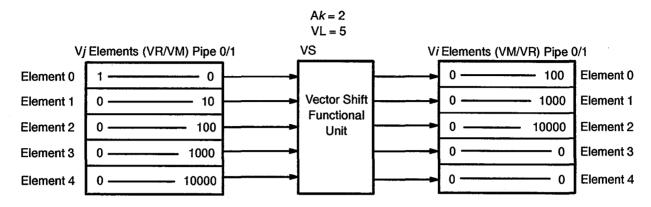

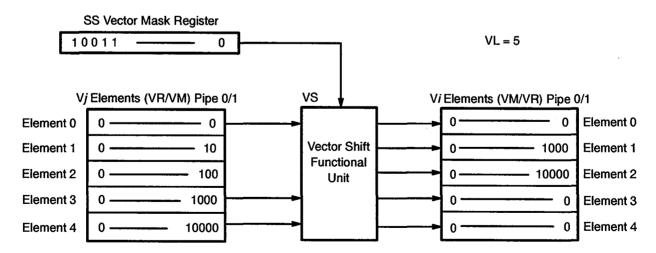

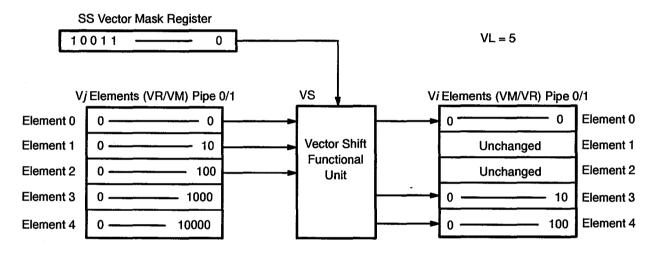

| VECTOR SHIFT    |                                           | 107 |

|                 | Vector Shift Instructions                 | 107 |

|                 | Vector Shift Count Description            | 108 |

|                 | Vector Right Shift 005400 151 <i>ij</i> 0 | 110 |

|                 | Vector Right Double Shift 153ijk          | 111 |

|                 | Vector Transfer 005400 152ijk             | 112 |

|                 | Vector Compress 005400 153 <i>ij</i> 0    | 112 |

|                 | Vector Expand 005400 153 <i>ij</i> 1      | 113 |

| VECTOR POP/POP | P PARITY AND LEADING ZERO                                           | 115 |

|----------------|---------------------------------------------------------------------|-----|

|                | Pop/Parity/Leading Zero Functional Units                            | 117 |

|                | Vector Population Count 174 <i>ij</i> 1                             | 117 |

|                | Vector Population/Parity 174ij2                                     | 117 |

|                | Vector Leading Zero Count 174ij3                                    | 117 |

|                | Vector Population/Parity Instructions                               | 118 |

| GATHER/SCATTER | RINSTRUCTIONS                                                       | 119 |

|                | Gather Instructions                                                 | 119 |

|                | Scatter Instructions                                                | 120 |

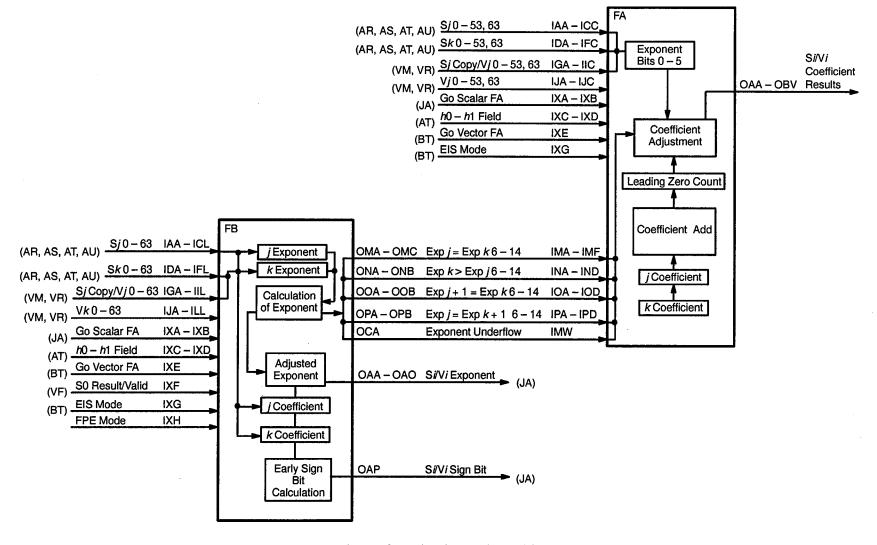

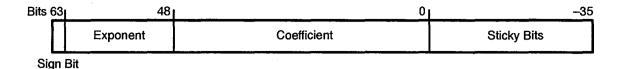

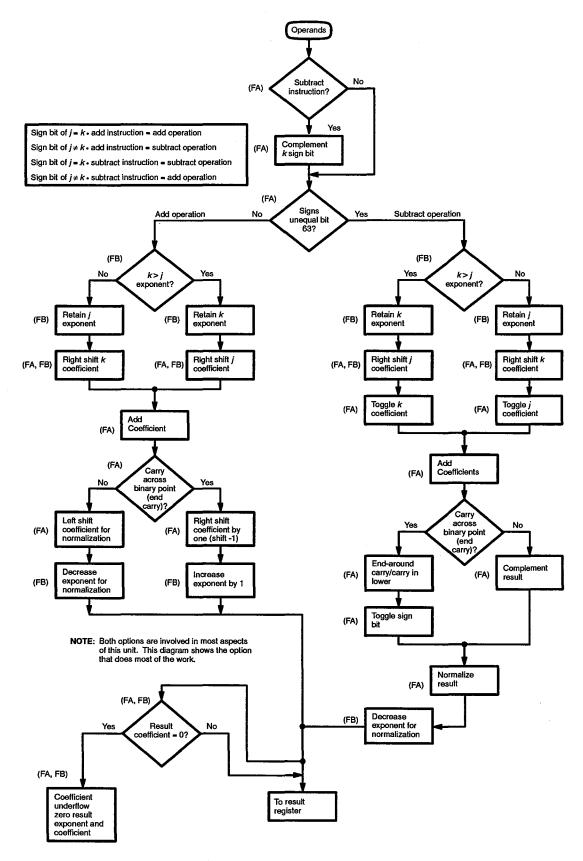

| FLOATING-POINT | ADD                                                                 | 121 |

|                | Floating-point Add Functional Unit Instructions                     | 123 |

|                | Floating-point Format                                               |     |

|                | Floating-point Add Examples                                         | 124 |

|                | Add Instruction (Subtract Operation)                                | 124 |

|                | Subtract Instruction (Add Operation)                                | 125 |

|                | Add Instruction (Subtract Operation with Carry across Binary Point) | 125 |

|                | Add Instruction (Add Operation)                                     |     |

|                | FA Option                                                           |     |

|                | FB Option                                                           |     |

|                | Determining Exponent Size                                           | 127 |

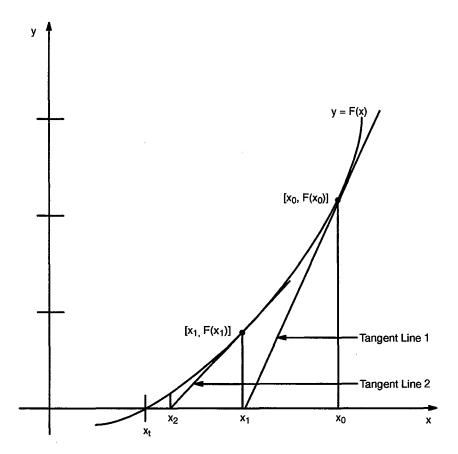

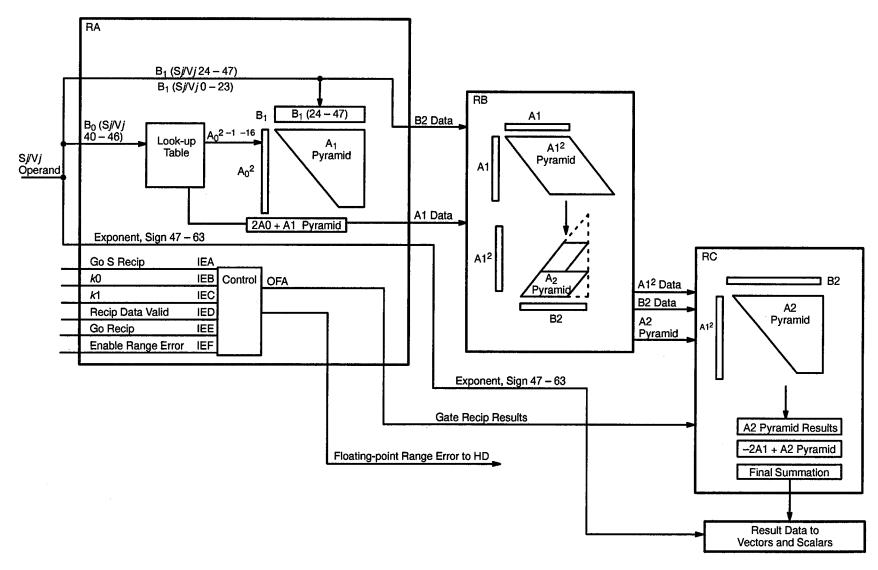

| FLOATING-POINT | RECIPROCAL APPROXIMATION                                            | 131 |

|                | Floating-point Division Algorithm                                   | 131 |

|                | Handling of B Exponent                                              | 138 |

|                | Floating-point Reciprocal Approximation Instructions                | 139 |

|                | RA Option                                                           | 139 |

|                | RB Option                                                           |     |

|                | RC Option                                                           | 139 |

|                | Multiply Algorithm                                                  | 141 |

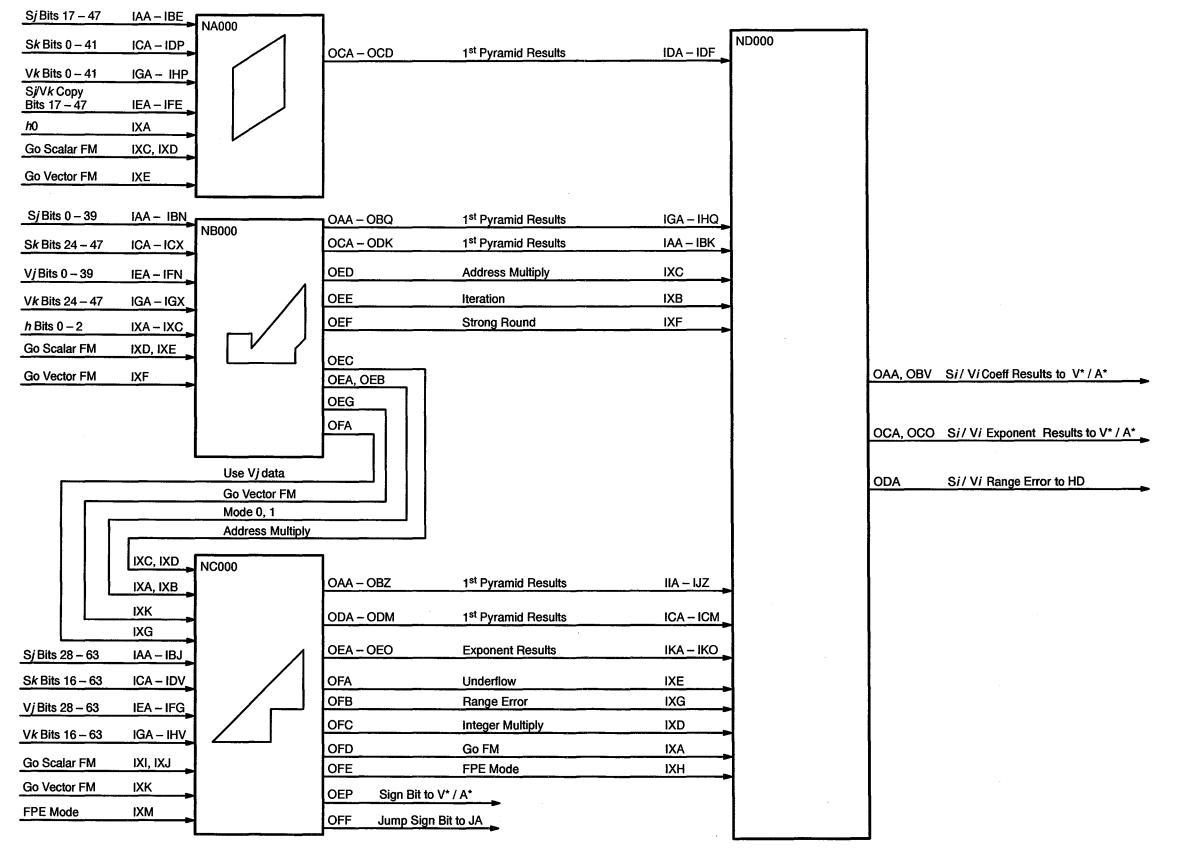

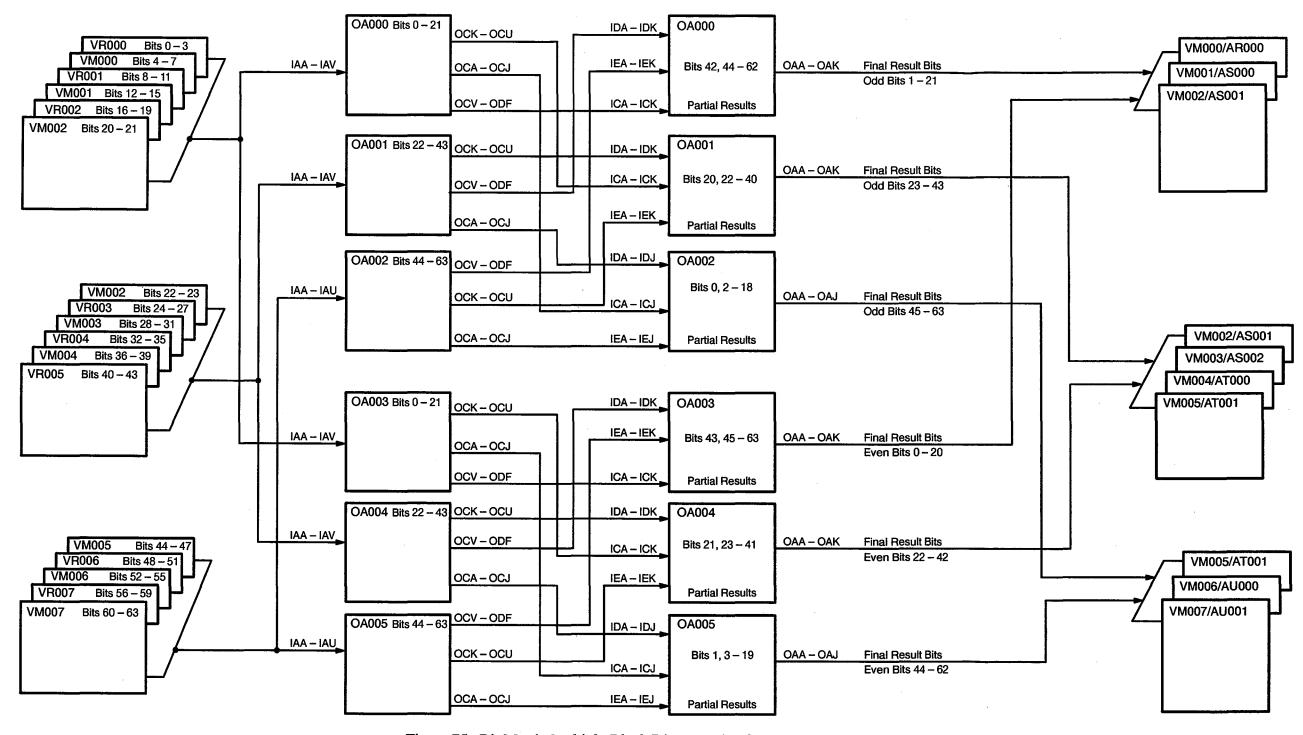

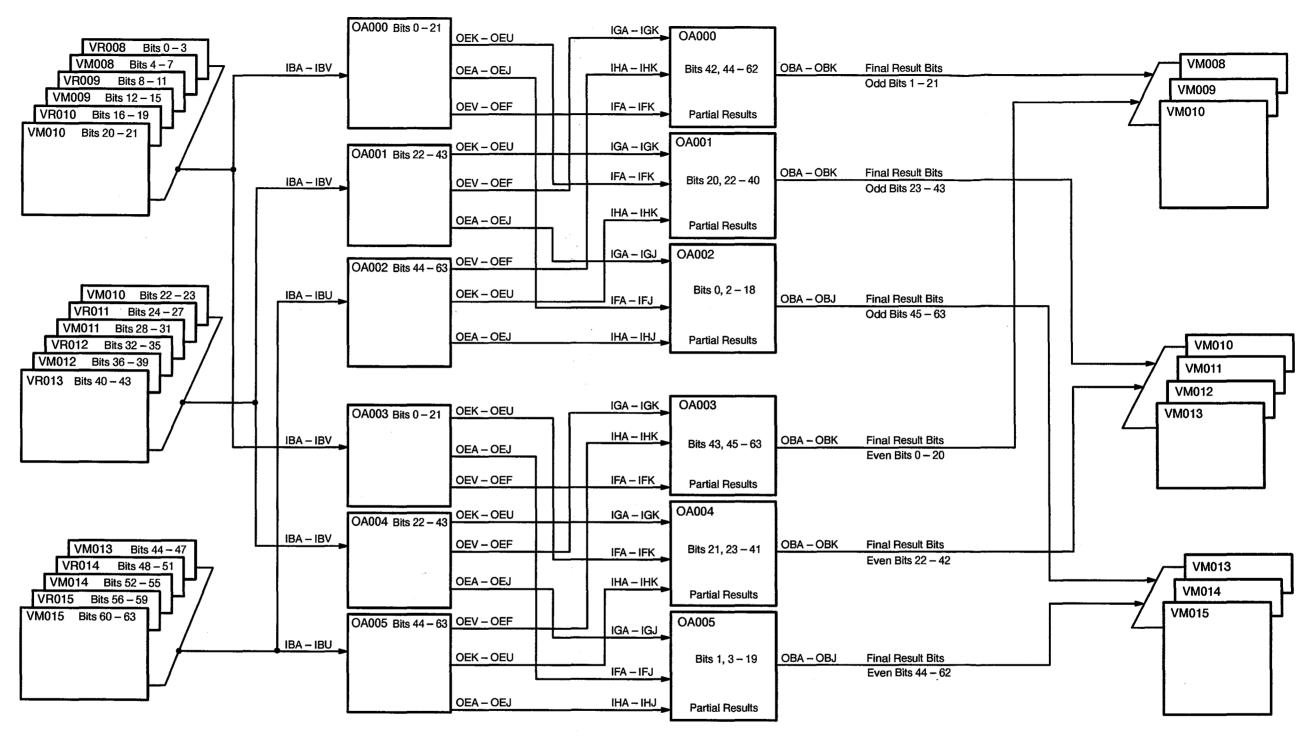

| FLOATING-POINT MU  | JLTIPLY                                              | 143        |

|--------------------|------------------------------------------------------|------------|

|                    | Divide Sequence                                      | 145        |

|                    | Floating-point Multiply Functional Unit Instructions | 146        |

|                    | NA option                                            | 147        |

|                    | NB option                                            | 147        |

|                    | NC option                                            | 147        |

|                    | ND option                                            | 148        |

| BIT MATRIX MULTIPL | .Y                                                   | 153        |

|                    | Bit Matrix Multiply Theory of Operation              | 153        |

|                    | Instructions                                         | 157        |

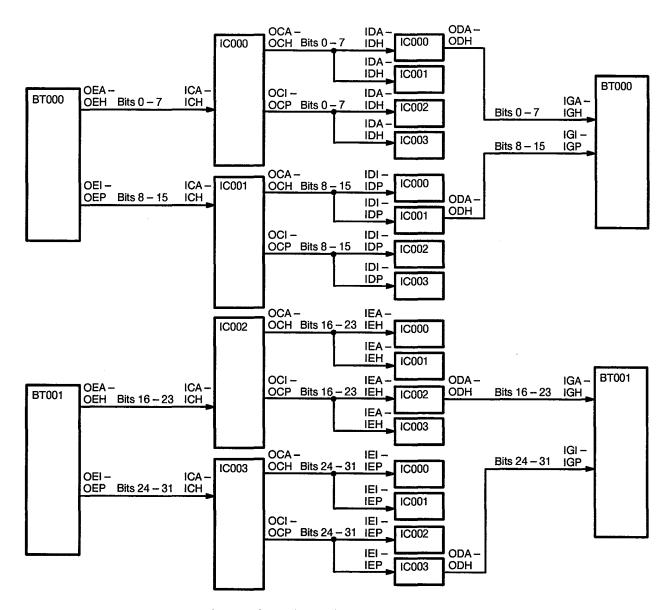

| INSTRUCTION BUFFI  | ERS                                                  | 163        |

|                    | Fetch                                                | 163        |

|                    | Prefetch                                             |            |

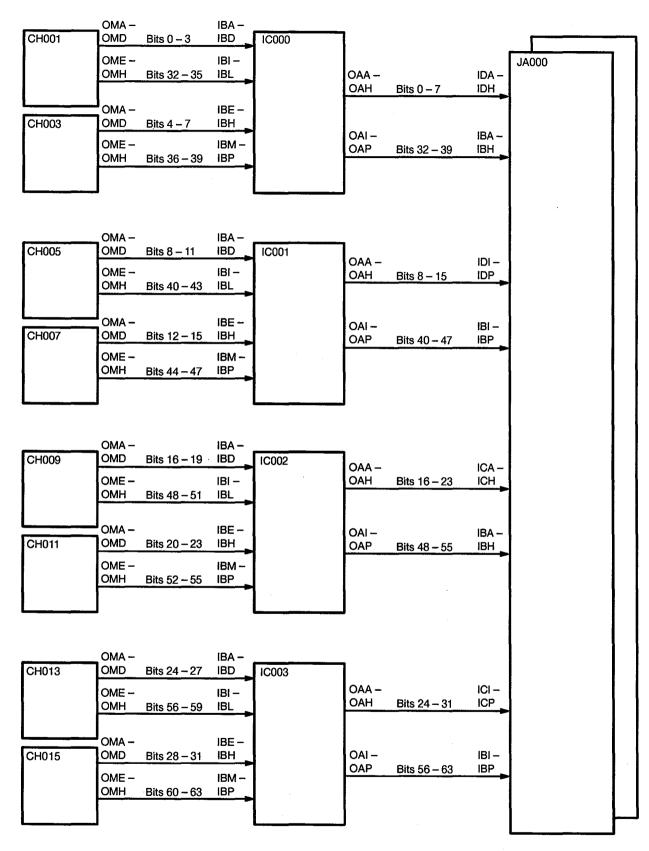

| INSTRUCTION ISSUE  |                                                      | 175        |

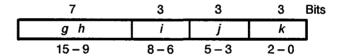

|                    | Instruction Formats                                  | 176        |

|                    | One-parcel Instructions                              | 176        |

|                    | Three-parcel Instructions                            | 176        |

|                    | Four-parcel Instructions                             | 177        |

|                    | Triton-mode Instructions                             | 177        |

|                    | Instruction Decode                                   | 177        |

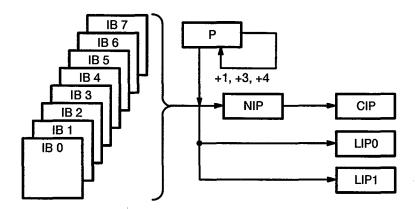

|                    | P Register                                           | 178        |

|                    | Coincidence                                          | 178        |

|                    | Reading the Instruction Buffer                       | 178        |

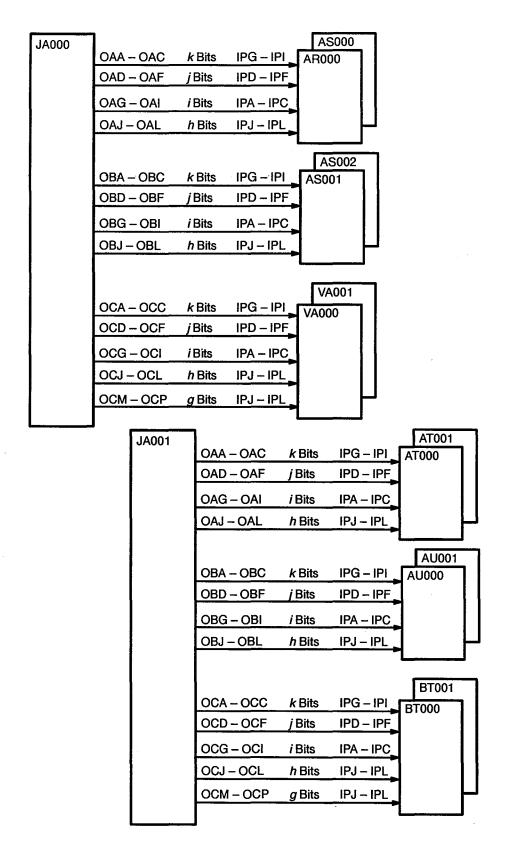

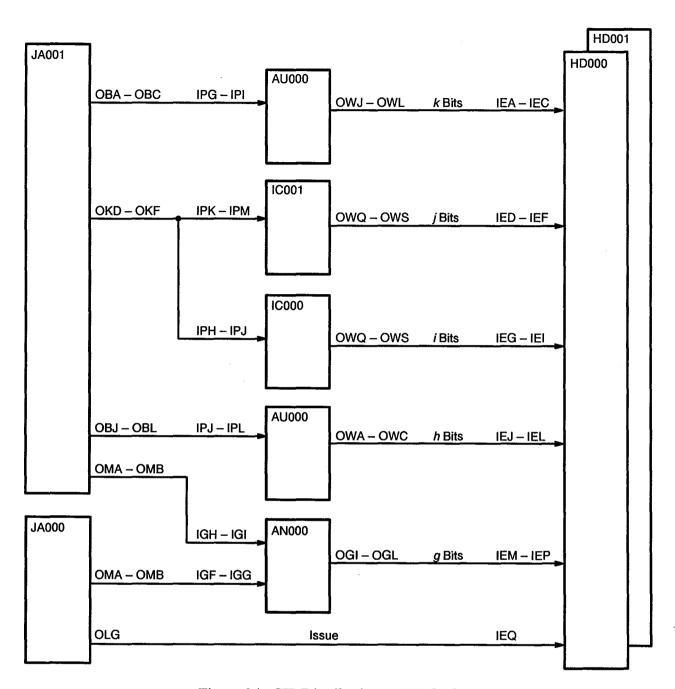

|                    | JA Option                                            | 179        |

|                    | ori Option                                           |            |

|                    | Parcel Data Distribution                             | 179        |

|                    |                                                      |            |

|                    | Parcel Data Distribution                             | 180        |

|                    | Parcel Data Distribution                             | 180<br>180 |

# INSTRUCTION ISSUE (continued)

|          | Common Memory Requests                            | 181 |

|----------|---------------------------------------------------|-----|

|          | Shared Resource Requests                          | 182 |

|          | Branch Requests                                   | 182 |

|          | Exchange Requests                                 | 182 |

|          | Interrupt Requests                                | 183 |

|          | Control Signal Distribution                       | 183 |

|          | Branch Instruction Control                        | 186 |

|          | Conditional Branch Instructions                   | 186 |

|          | Unconditional Branch Instructions                 | 186 |

| ·        | Issue Control                                     | 187 |

| EXCHANGE |                                                   | 199 |

|          | Exchange Process                                  | 199 |

|          | SIPI                                              |     |

|          | Interrupt Flag Set                                |     |

|          | Program Exit                                      |     |

|          | Exchange Sequence                                 |     |

|          | Exchange Package Descriptions                     |     |

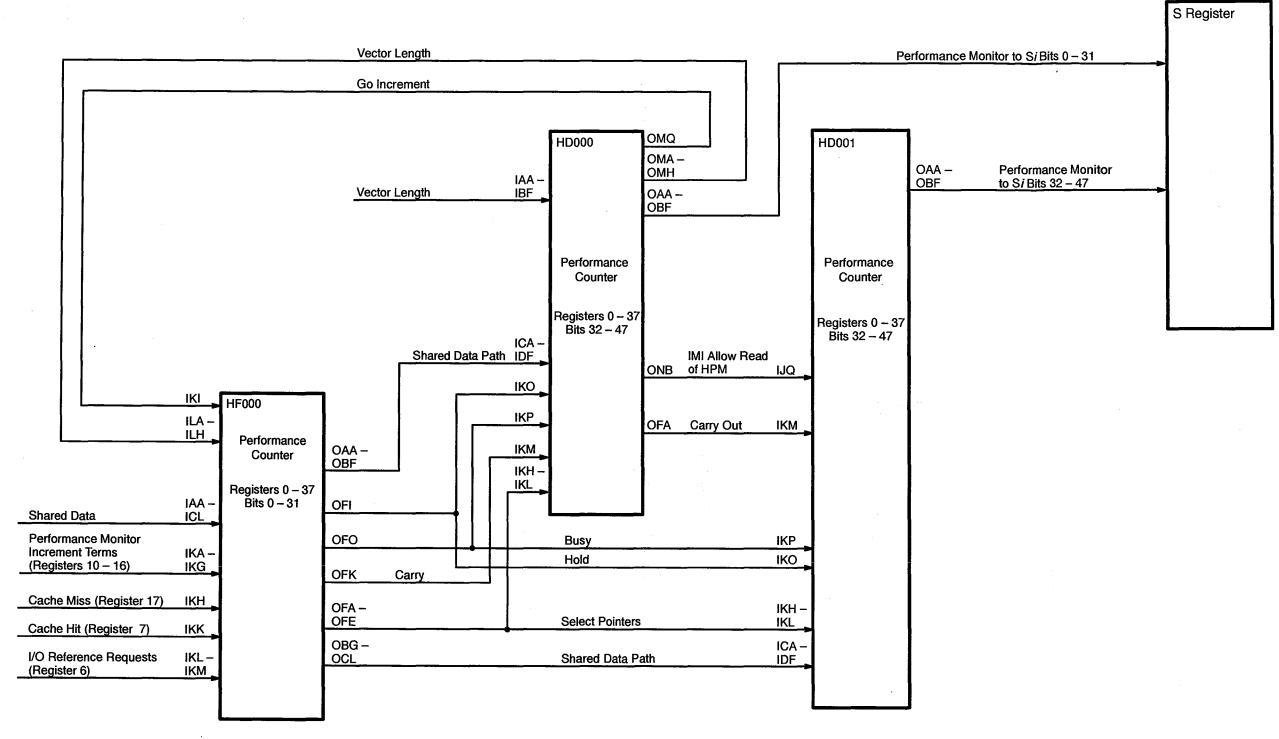

|          | PROGRAMMABLE CLOCK INTERRUPT, PERFORMANCE MONITOR | 211 |

|          | Real-time Clock                                   | 211 |

|          | Programmable Clock                                | 212 |

|          | RTC and PC Instructions                           | 213 |

|          | Performance Monitor                               | 213 |

|          | Performance Monitor Instructions                  | 215 |

|          | Clearing the Performance Counters                 | 215 |

|          | Reading the Performance Monitor                   | 215 |

|          | Performance Monitor Block Diagram                 | 216 |

|          | Status Register                                   | 216 |

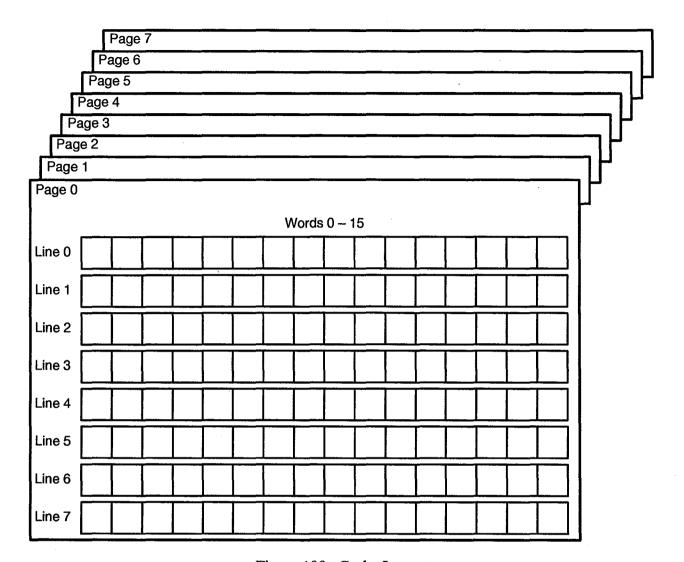

| SCALAR CACHE | <b></b>     |                                                                           | 225 |  |

|--------------|-------------|---------------------------------------------------------------------------|-----|--|

|              | Cache Hit   |                                                                           | 225 |  |

|              | Cache Miss  | S                                                                         | 226 |  |

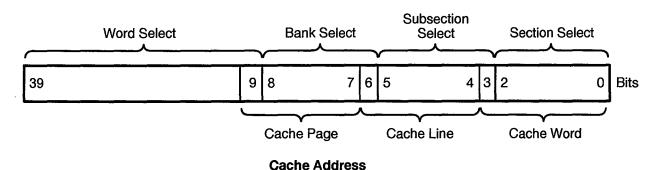

|              | Cache Add   | ressing                                                                   | 227 |  |

|              | Potential C | ache Problems                                                             | 227 |  |

|              | CH Option   |                                                                           | 228 |  |

|              | Scalar Cacl | he Instructions                                                           | 228 |  |

| Figures      |             |                                                                           |     |  |

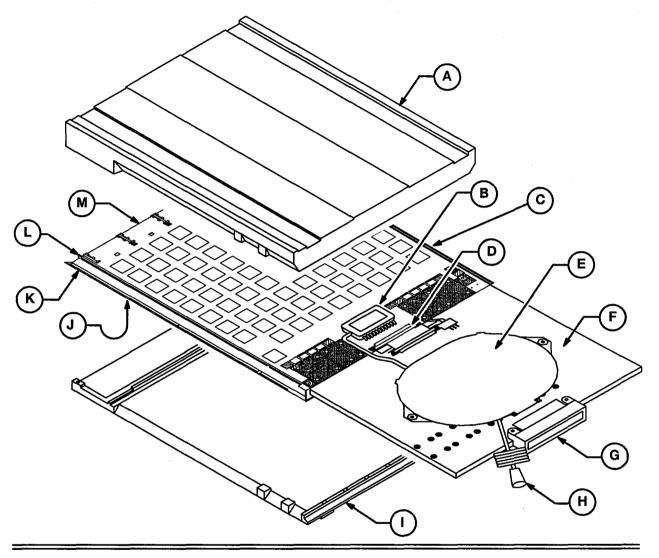

|              | Figure 1.   | CP Module Assembly Components                                             | 2   |  |

|              | Figure 2.   | Option Layout Board 1                                                     | 3   |  |

|              | Figure 3.   | Option Layout Board 2                                                     | 4   |  |

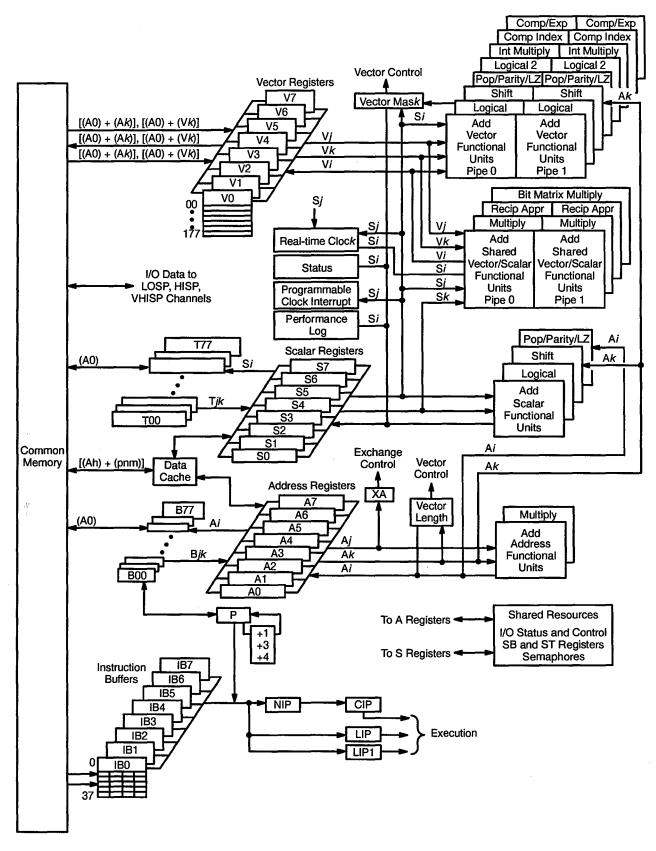

|              | Figure 4.   | CPU Block Diagram                                                         | 5   |  |

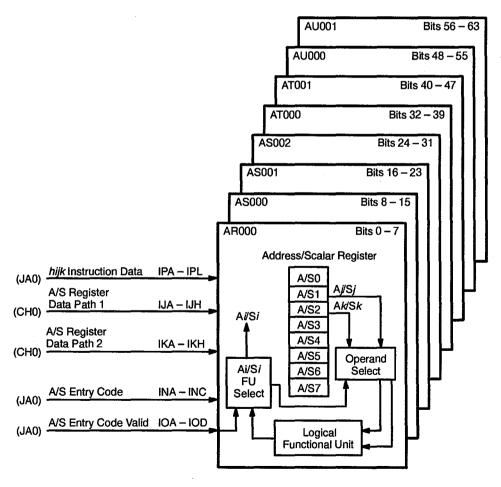

|              | Figure 5.   | Address and Scalar Register Data Paths                                    | 8   |  |

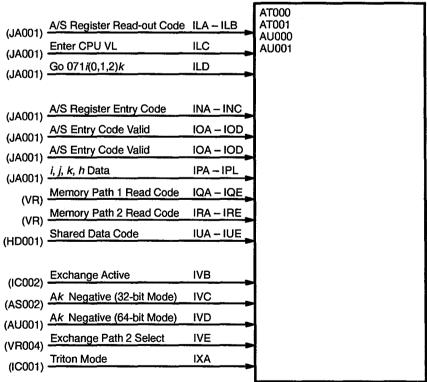

|              | Figure 6.   | A/S Control Terms                                                         | 10  |  |

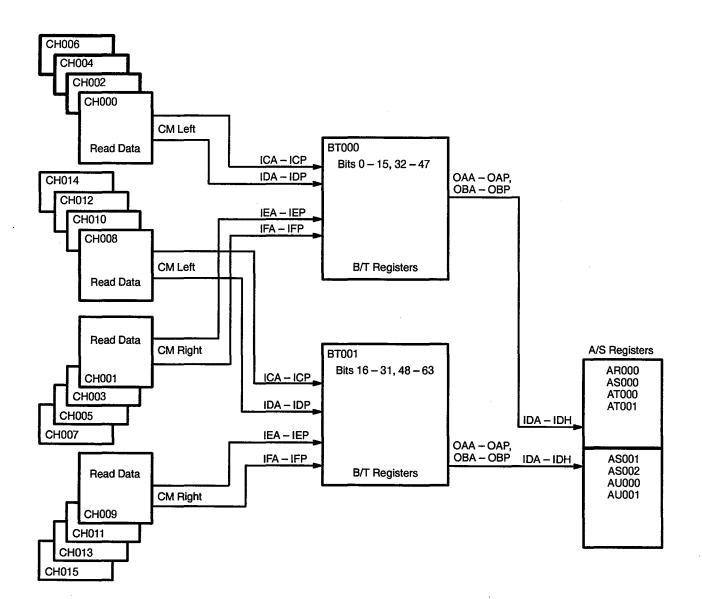

|              | Figure 7.   | Memory to A/S-register Block Diagram                                      | 12  |  |

|              | Figure 8.   | B and T Register Inputs and Outputs                                       | 15  |  |

|              | Figure 9.   | B/T-register-to-memory Block Diagram                                      | 17  |  |

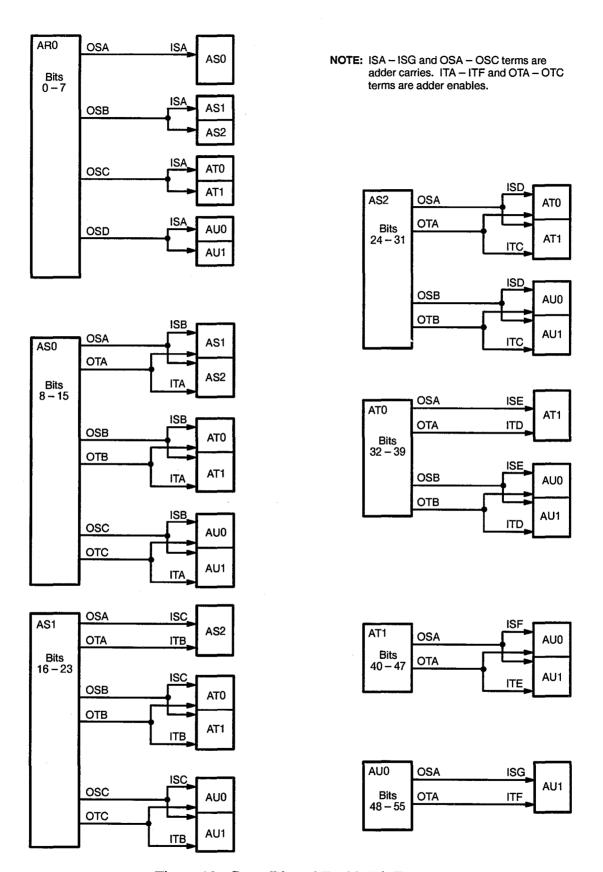

|              | Figure 10.  | Carry Bit and Enable Bit Fanouts                                          | 20  |  |

|              | Figure 11.  | Address/Scalar Logical Block Diagram (Instructions 044ijk through 051ijk) | 21  |  |

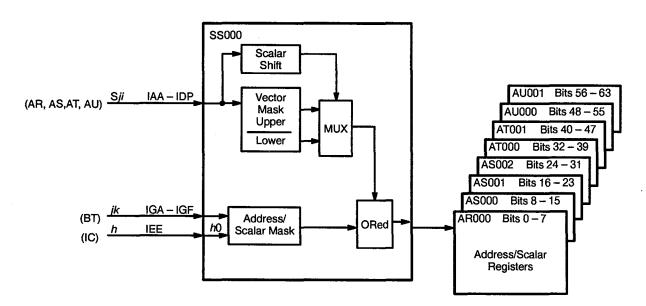

|              | Figure 12.  | Scalar Mask Block Diagram                                                 | 24  |  |

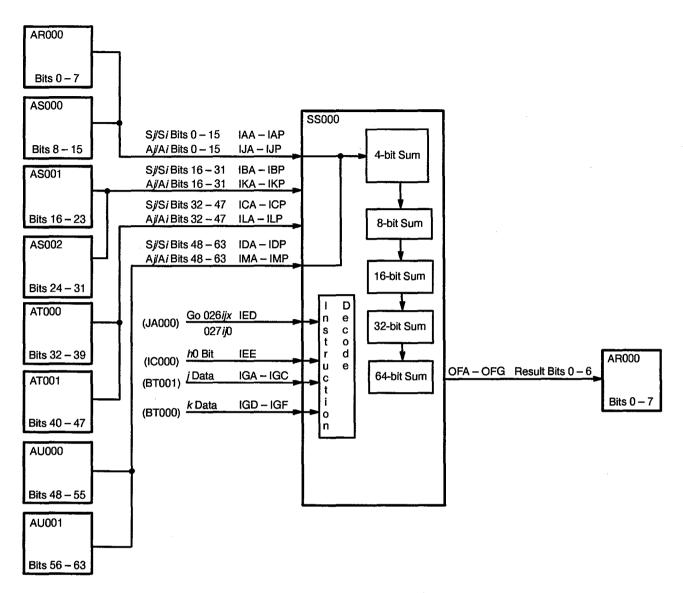

|              | Figure 13.  | A/S Population/Parity/Leading Zero Count                                  | 29  |  |

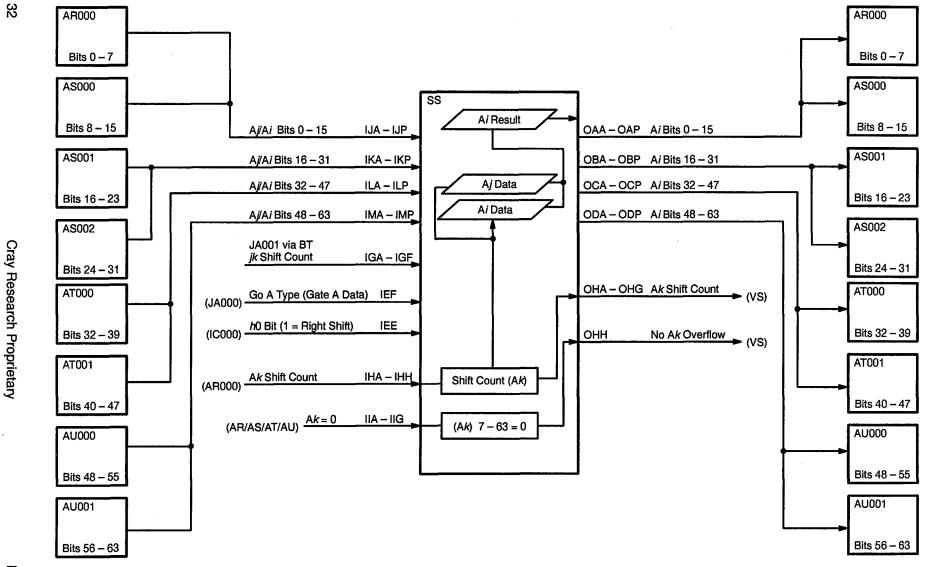

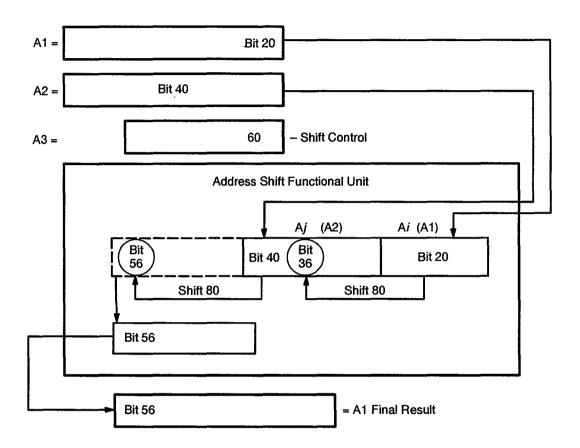

|              | Figure 14.  | Address Register Shift                                                    | 32  |  |

|              | Figure 15.  | Shift Count Breakdown                                                     | 34  |  |

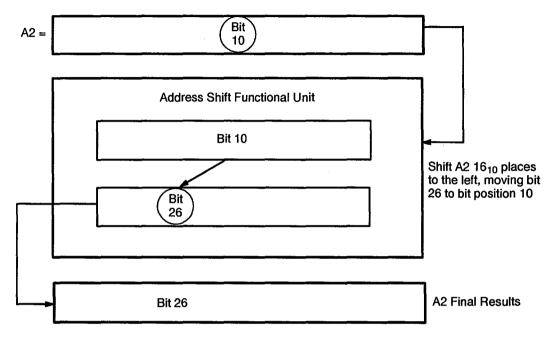

|              | Figure 16.  | Address Register Left Single Shift                                        | 35  |  |

|              | Figure 17.  | Address Register Right Single Shift                                       | 36  |  |

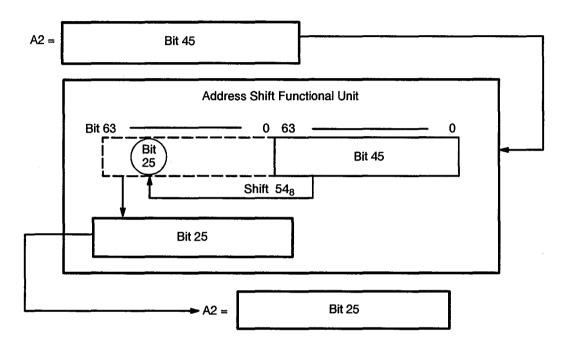

|              | Figure 18.  | Address Register Left Double Shift                                        | 37  |  |

|              | Figure 19.  | Address Register Right Double Shift                                       | 38  |  |

|              | Figure 20.  | Example of an A Register Left Single-shift Instruction                    | 39  |  |

|              | Figure 21.  | Example of an Address Register Left Double-shift Instruction              | 41  |  |

|              | Figure 22.  | Example of an Address Register Right Double-shift Instruction             | 42  |  |

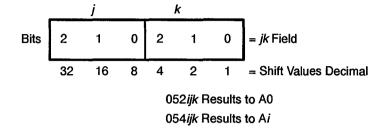

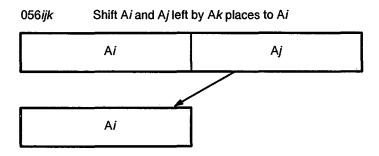

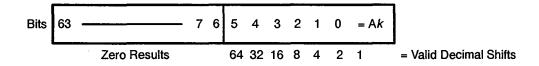

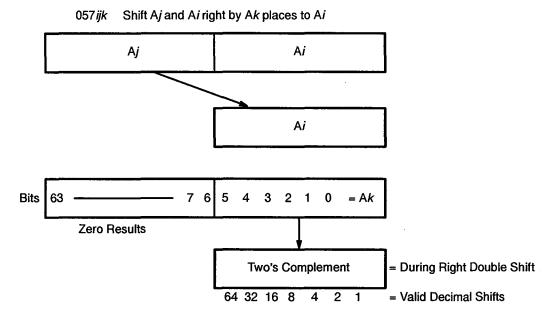

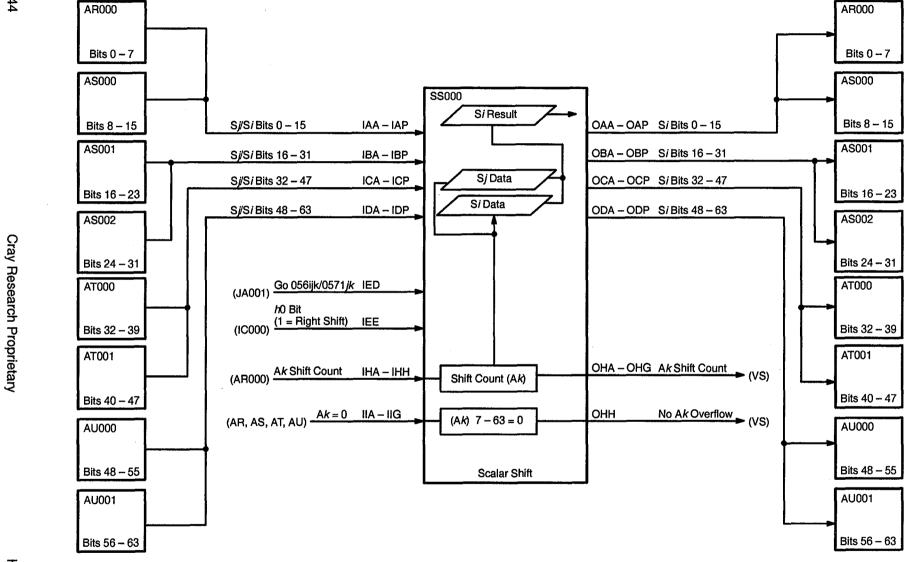

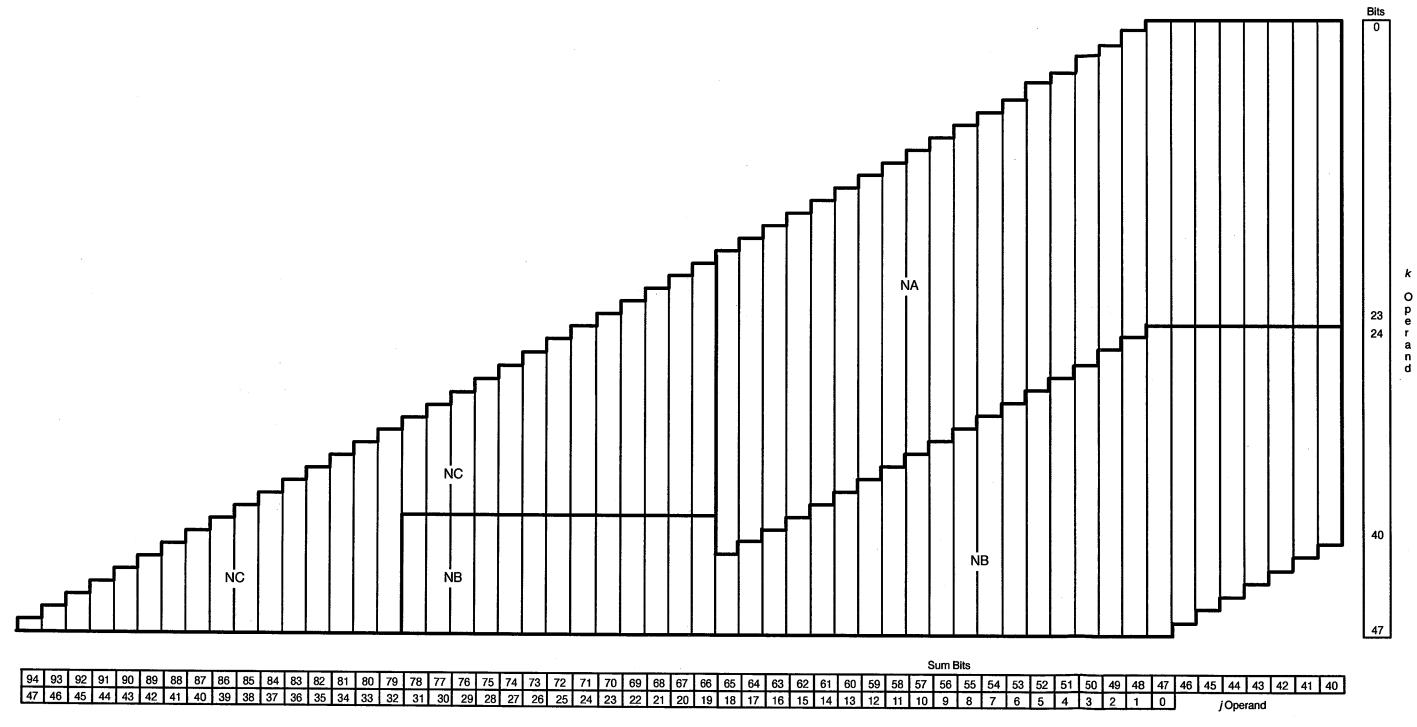

|              | Figure 23.  | Scalar Shift                                                              | 44  |  |

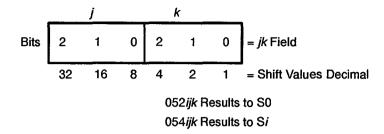

|              | Figure 24.  | Shift Count Breakdown                                                     | 46  |  |

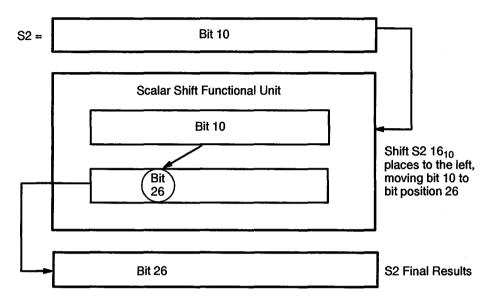

| Figure 25. | Scalar Left Single Shift                                     | 47  |

|------------|--------------------------------------------------------------|-----|

| Figure 26. | Scalar Right Single Shift                                    | 48  |

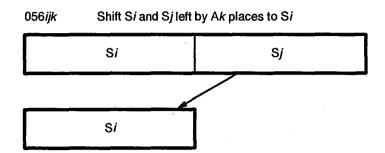

| Figure 27. | Scalar Left Double Shift                                     | 49  |

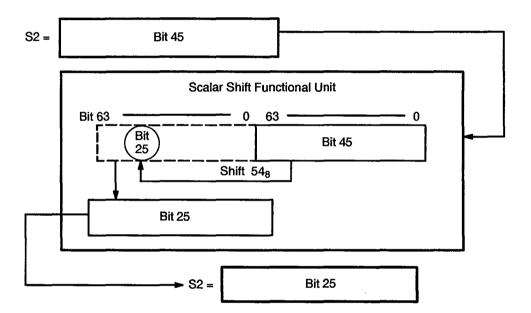

| Figure 28. | Scalar Right Double Shift                                    | 50  |

| Figure 29. | Example of Scalar Left Single-shift Instruction              | 51  |

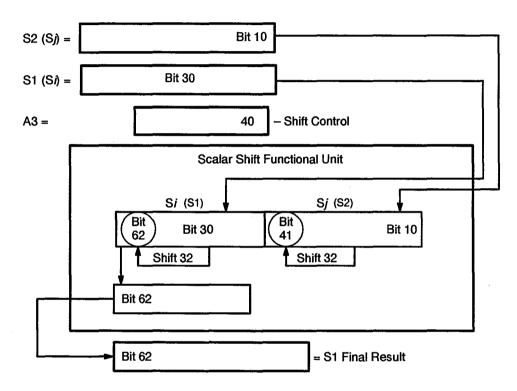

| Figure 30. | Example of a Scalar Register Left Double-shift Instruction   | 53  |

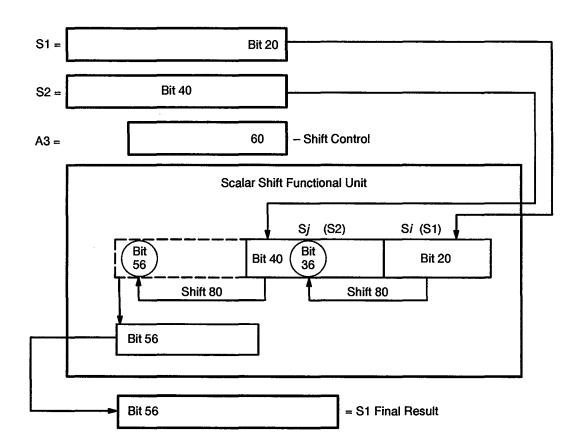

| Figure 31. | Example of a Scalar Register Right Double-shift Instruction  | 54  |

| Figure 32. | AN Option                                                    | 56  |

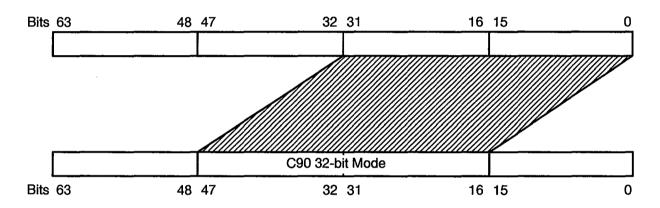

| Figure 33. | C90 Operation Mode                                           | 60  |

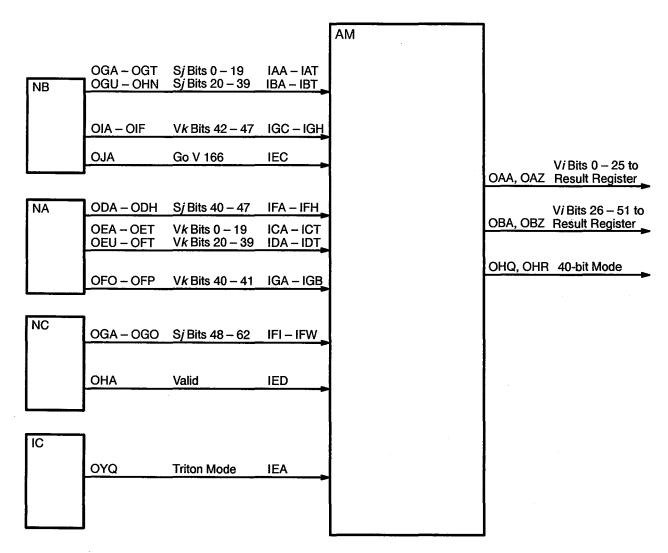

| Figure 34. | AM Option Inputs                                             | 61  |

| Figure 35. | Write Data Path                                              | 69  |

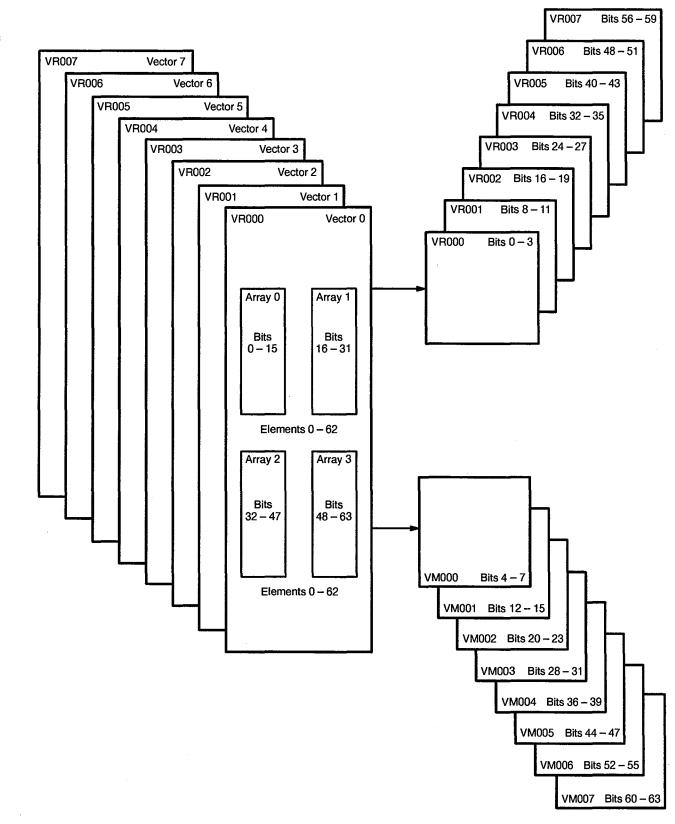

| Figure 36. | Read Data Path for Pipe 0 (Even Elements)                    | 71  |

| Figure 37. | Read Data Path for Pipe 1 (Odd Elements)                     | 72  |

| Figure 38. | Vector Register Write Block Diagram (Pipe 0)                 | 73  |

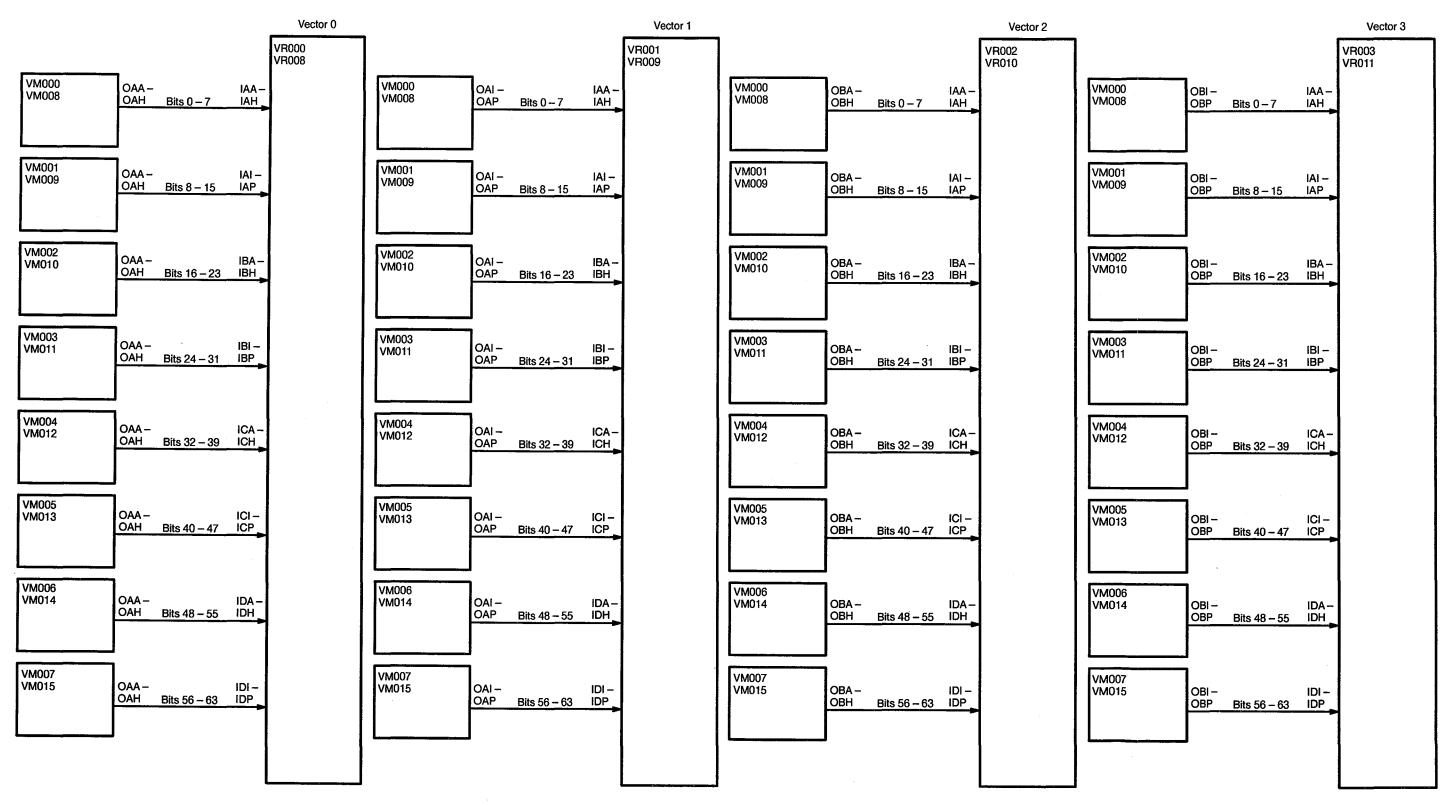

| Figure 39. | Vectors 0 through 3 Pipe 0/1 Read Data Path                  | 75  |

| Figure 40. | Vectors 4 through 7 Pipe 0/1 Read Data Path                  | 77  |

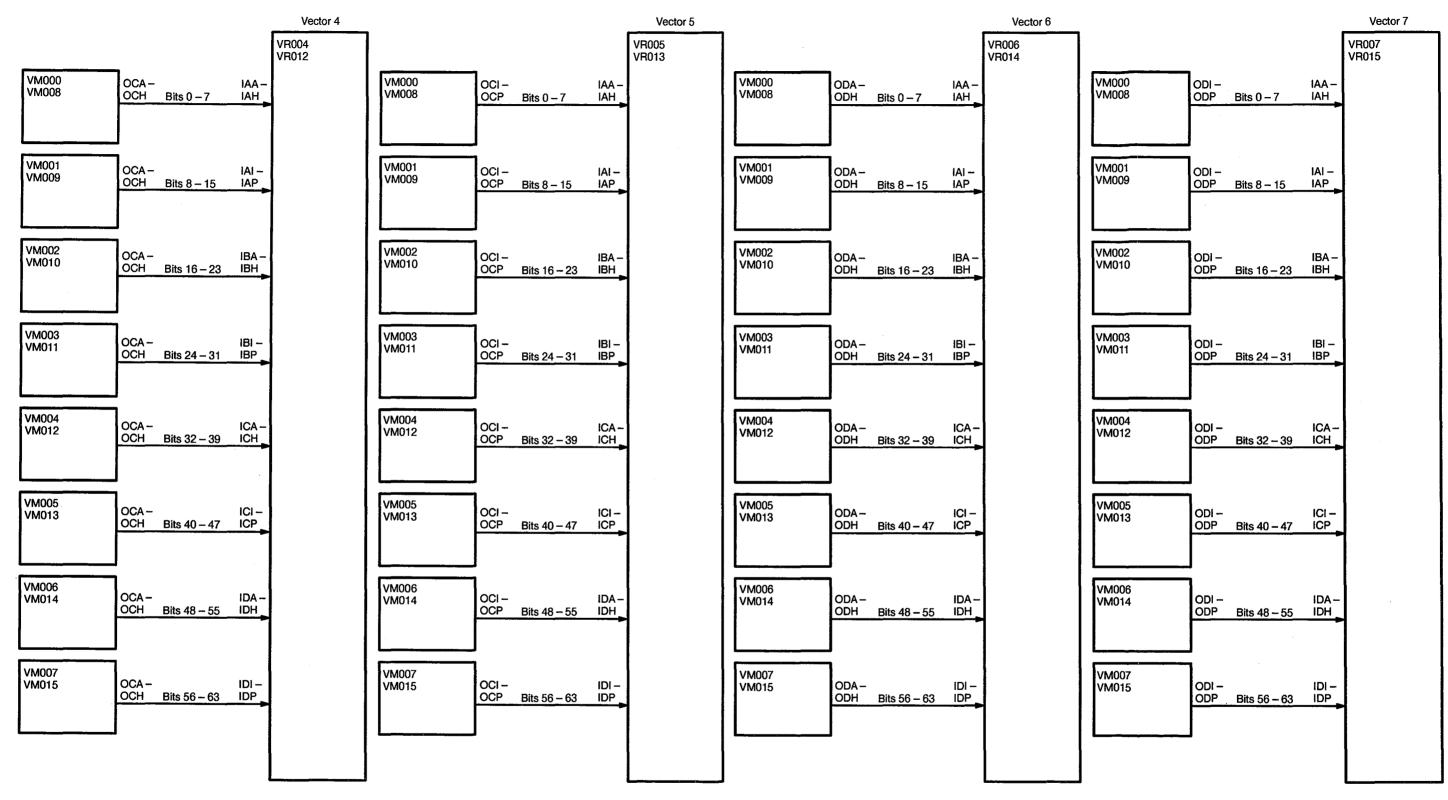

| Figure 41. | Vectors 0 through 3 Pipe 0/1 Write Data Path                 | 79  |

| Figure 42. | Vectors 4 through 7 Pipe 0/1 Write Data Path                 | 81  |

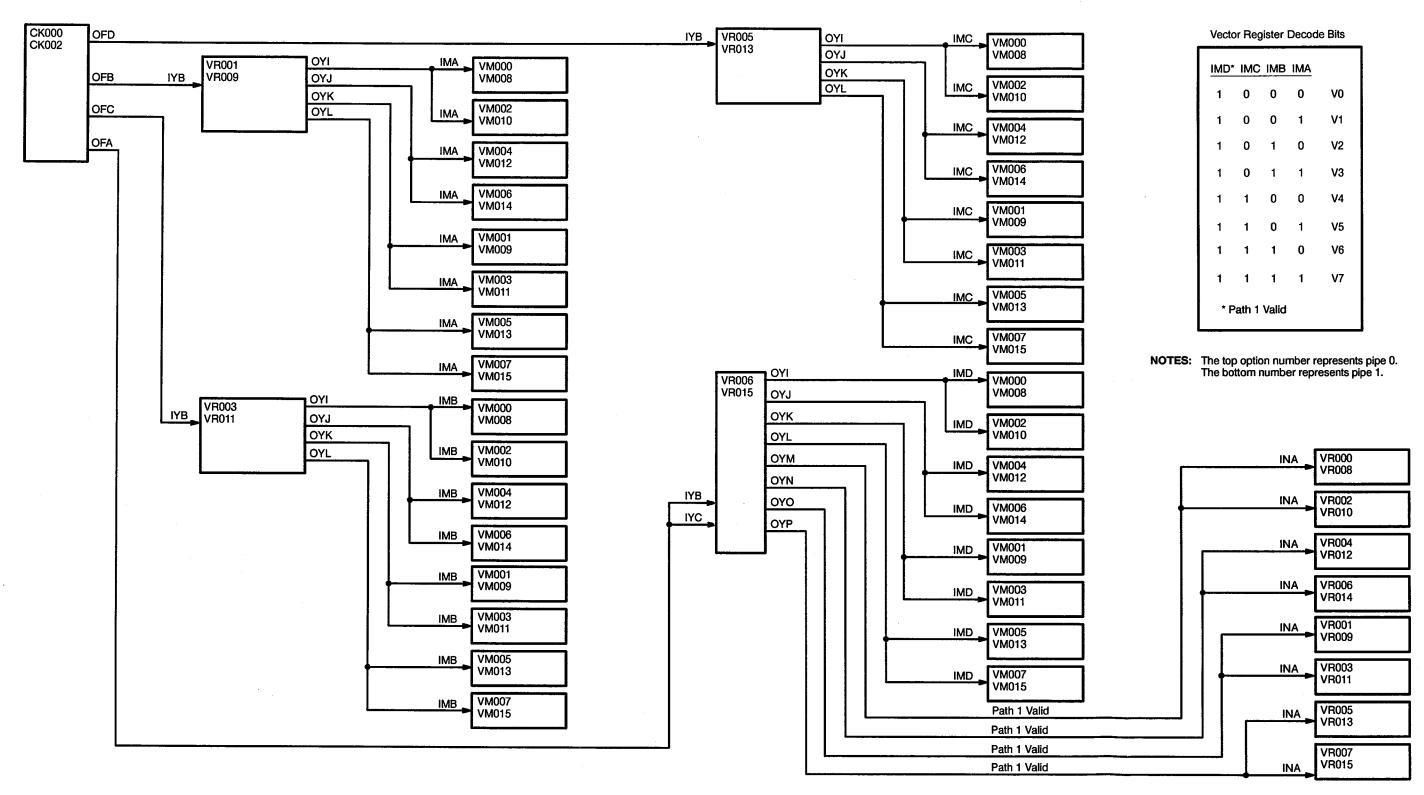

| Figure 43. | Vector Register Decode Bit Fanout (Pipe 0 and 1 Path 1 Only) | 83  |

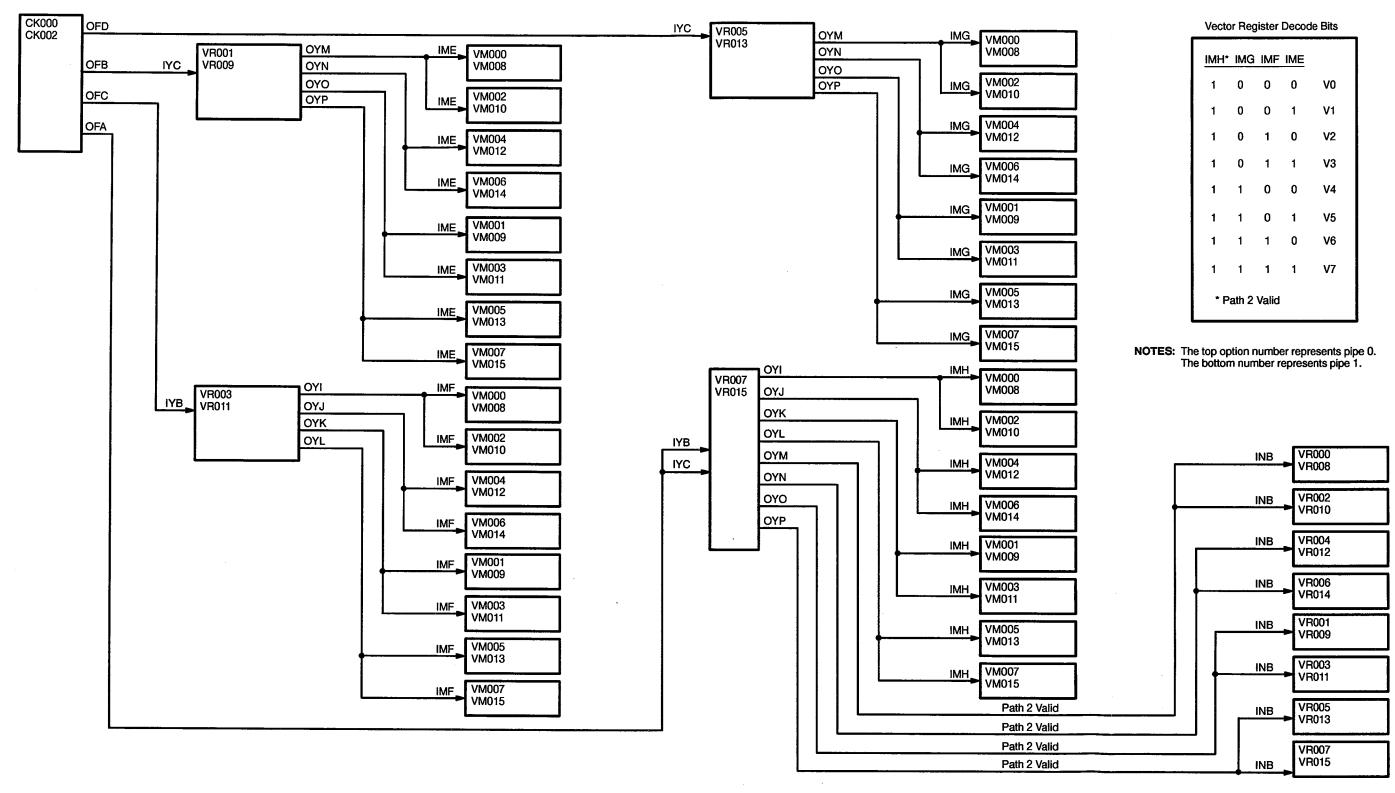

| Figure 44. | Vector Register Decode Bit Fanout (Pipe 0 and 1 Path 2 Only) | 85  |

| Figure 45. | S Register to Vectors                                        | 87  |

| Figure 46. | Memory Data to Vectors (Even Elements)                       | 89  |

| Figure 47. | Memory Data to Vectors (Odd Elements)                        | 91  |

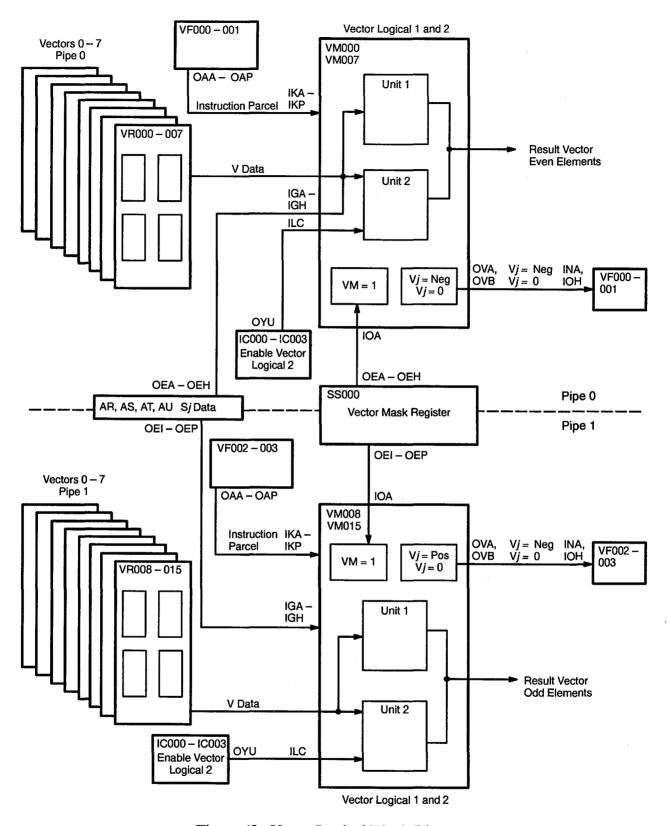

| Figure 48. | Vector Logical Block Diagram                                 | 94  |

| Figure 49. | Vector Merge Operation                                       | 97  |

| Figure 50. | 1750j0 Instructions                                          | 99  |

| Figure 51. | Function of the 175ij4 Instructions                          | 100 |

| Figure 52. | Iota Pipe 0                                                  | 101 |

| Figure 53. | Function of the 070ij1 Instructions                          | 102 |

| Figure 54. | Vector Add Block Diagram                                     | 105 |

| Figure 55. | Shift Count Breakdown                                        | 108 |

| Figure 56. | Vector Shift Block Diagram                                   | 109 |

| Figure 57. | Vector Right Shift                                           | 110 |

| Figure 58. | Vector Right Double Shift                                    | 111 |

# Figures (continued)

| Figure 59 | 9. Vector Transfer                                     | 112 |

|-----------|--------------------------------------------------------|-----|

| Figure 60 | ). Vector Compress                                     | 112 |

| Figure 6  | 1. Vector Expand                                       | 113 |

| Figure 62 | 2. Vector Population/Parity/Leading Zero Block Diagram | 116 |

| Figure 63 | 3. Floating-point Add                                  | 122 |

| Figure 64 | 4. Floating-point Add Sticky Bits                      | 123 |

| Figure 6: | 5. Floating-point Format                               | 123 |

| Figure 6  | 5. Floating-point Add Flowchart                        | 129 |

| Figure 6' | 7. Newton's Method for Approximating Roots             | 132 |

| Figure 6  | 3. Reciprocal Approximation Functional Unit            | 140 |

| Figure 69 | P. Floating-point Multiply Block Diagram               | 149 |

| Figure 70 | ). Floating-point Multiply First-level Summation       | 151 |

| Figure 7  | . Vector Storage of Bit Matrices                       | 154 |

| Figure 72 | 2. Mathematical Representation of Matrices A and B     | 155 |

| Figure 73 | B. B Matrix and B <sup>t</sup> Matrix Relationships    | 155 |

| Figure 74 | 4. Multiplication of A and B <sup>t</sup>              | 156 |

| Figure 7: | 5. Bit Matrix Multiply Block Diagram Pipe 0            | 159 |

| Figure 70 | 5. Bit Matrix Multiply Block Diagram Pipe 1            | 161 |

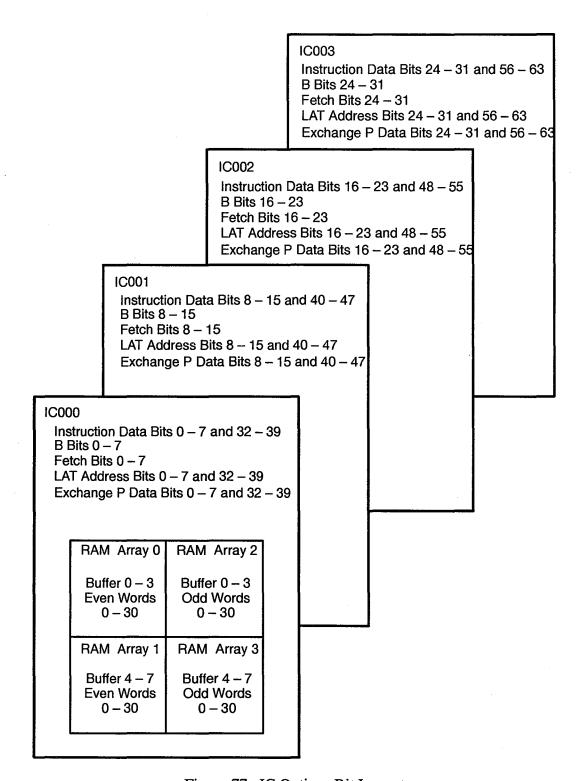

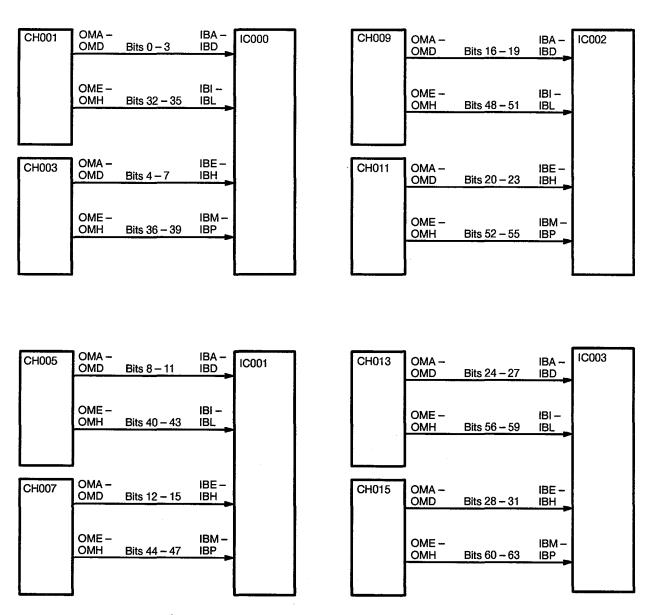

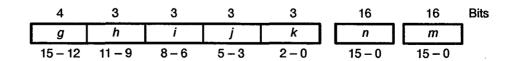

| Figure 7  | 7. IC Options Bit Layout                               | 166 |

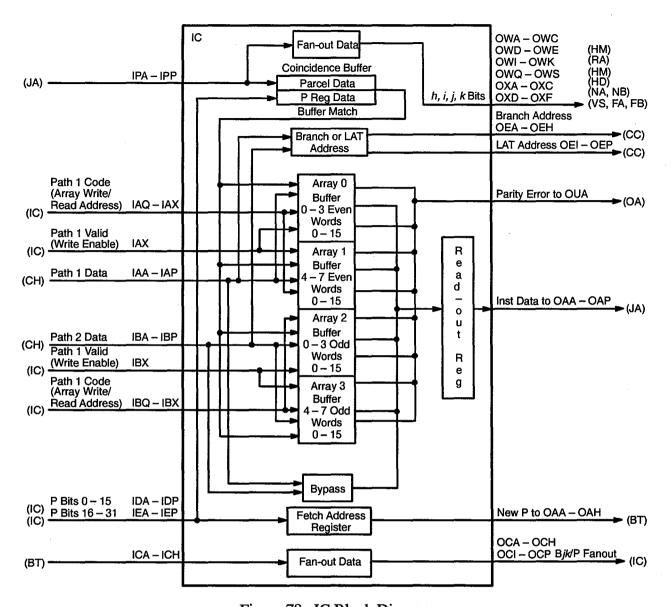

| Figure 78 | 3. IC Block Diagram                                    | 167 |

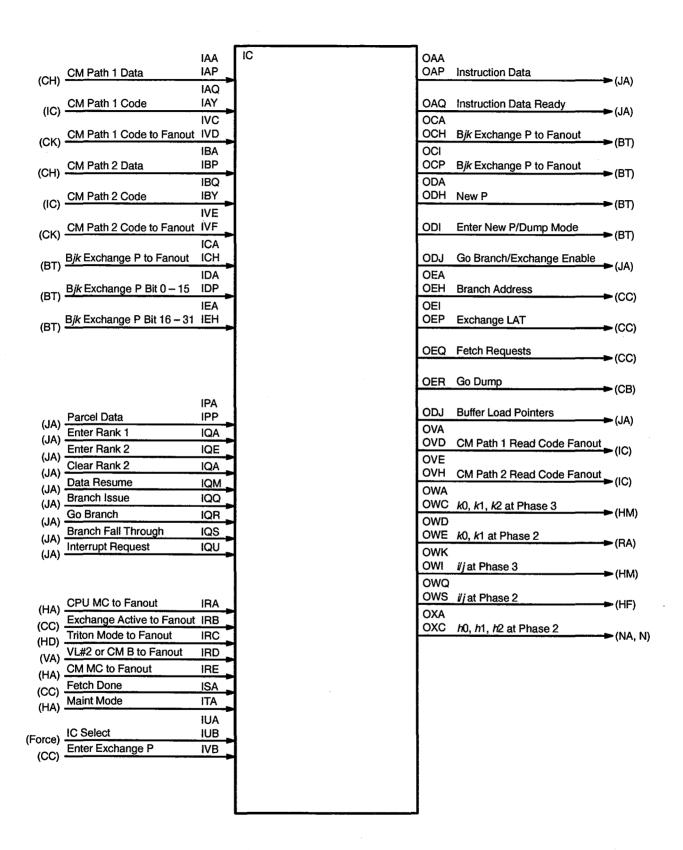

| Figure 79 | O. IC Option Terms                                     | 168 |

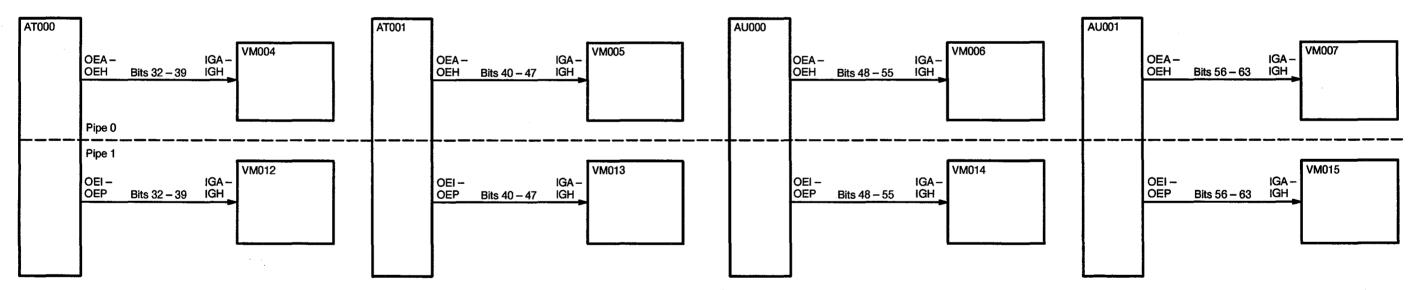

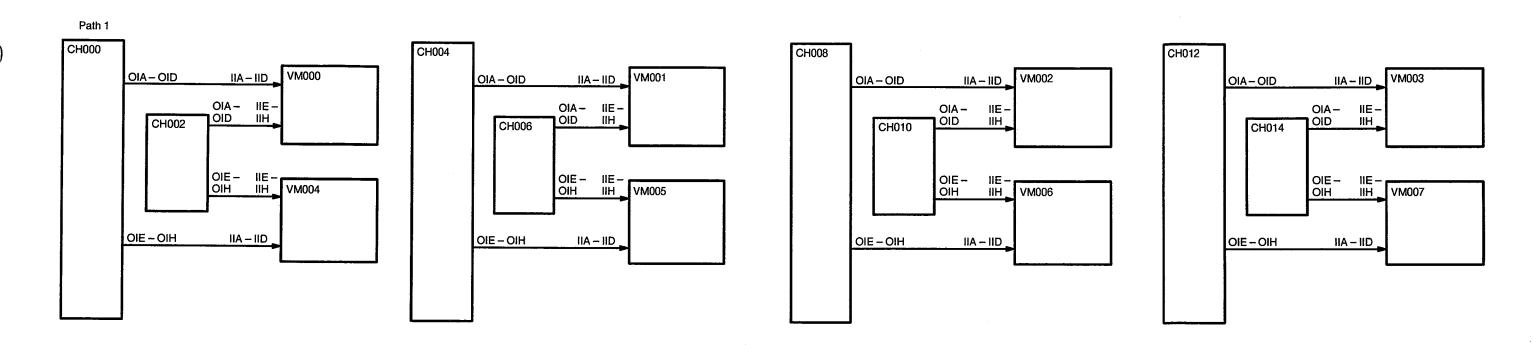

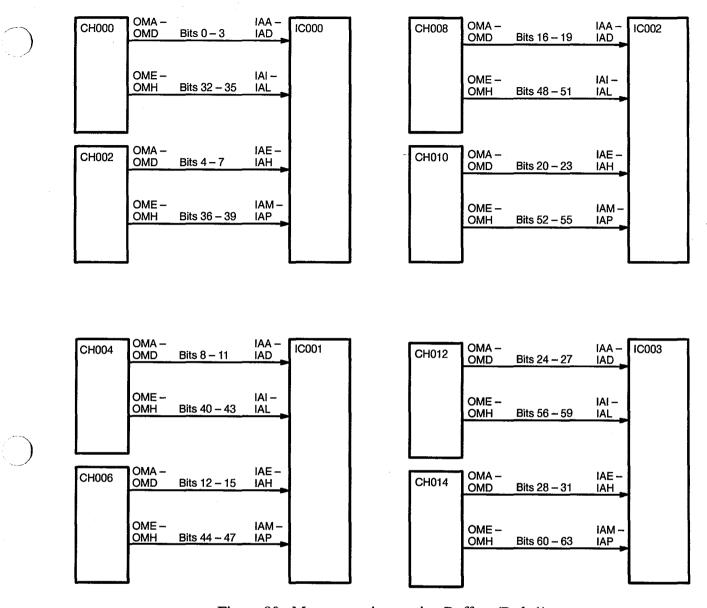

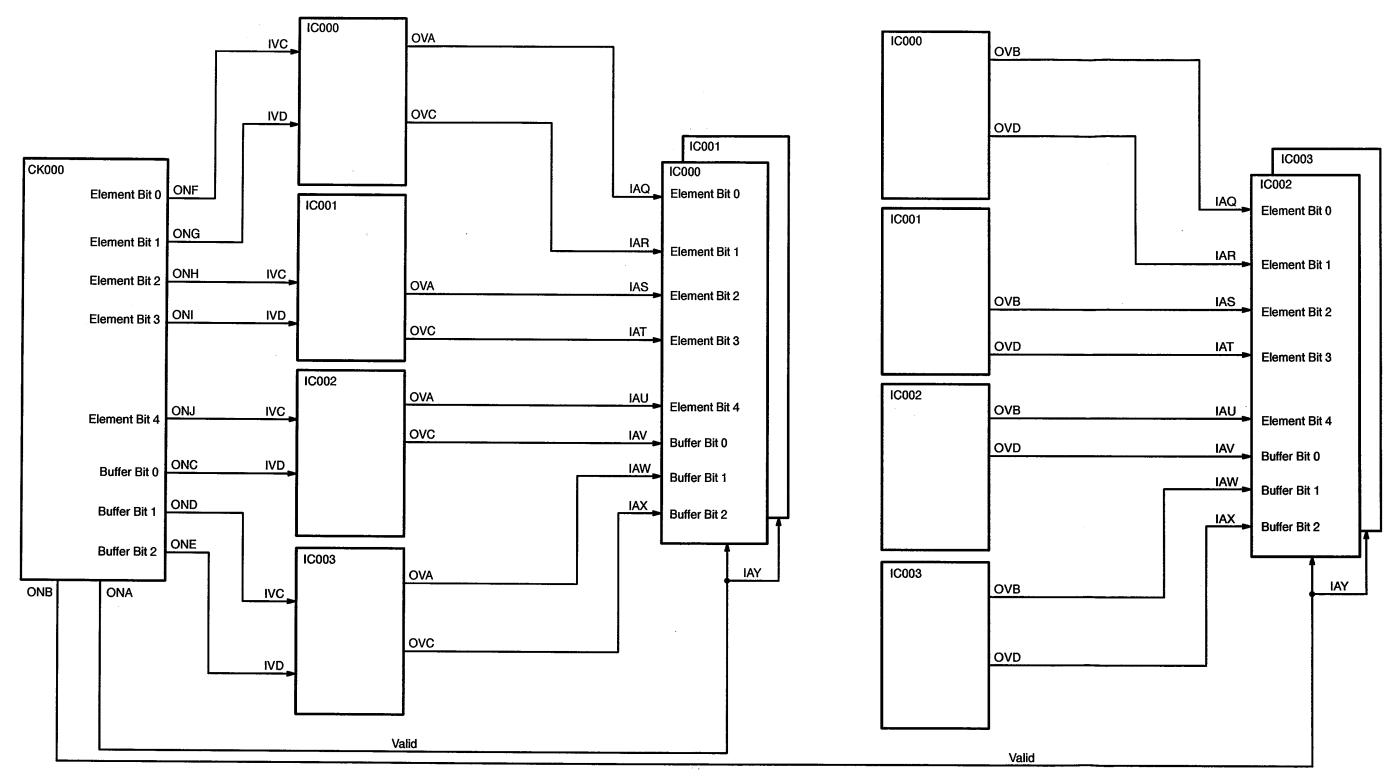

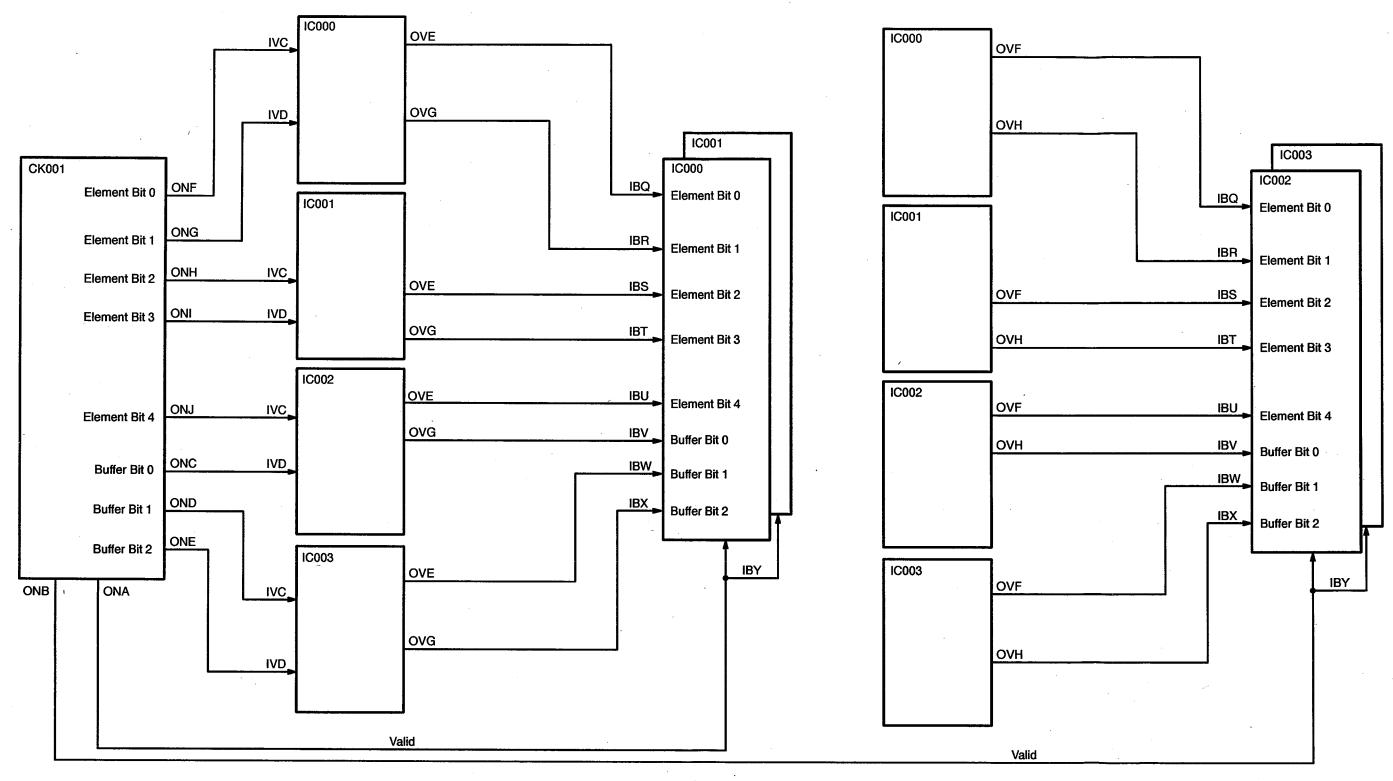

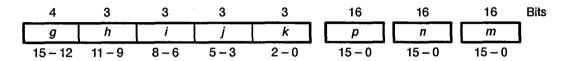

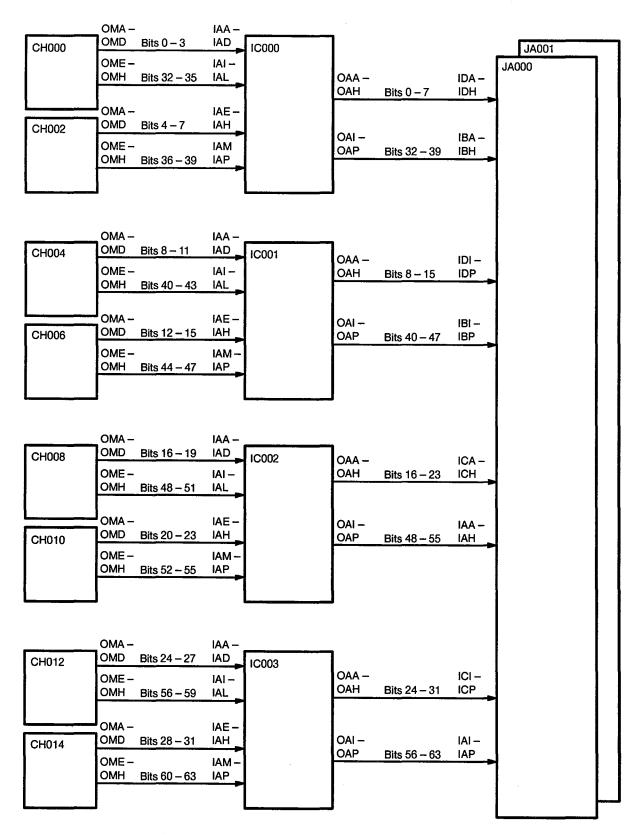

| Figure 80 | O. Memory-to-instruction Buffers (Path 1)              | 169 |

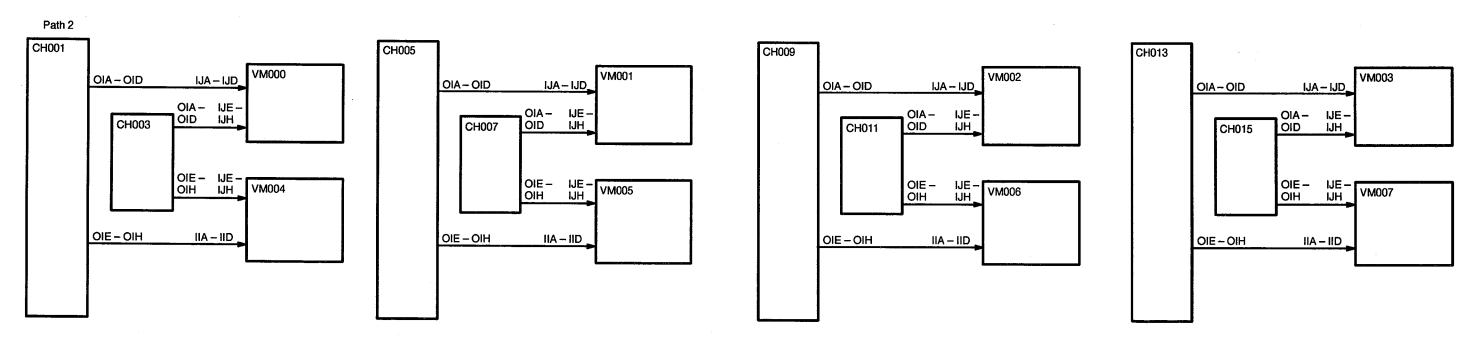

| Figure 8  | . Memory-to-instruction Buffers (Path 2)               | 170 |

| Figure 82 | 2. Common Memory Path Code 1 Fanouts                   | 171 |

| Figure 83 | 3. Common Memory Path Code 2 Fanouts                   | 173 |

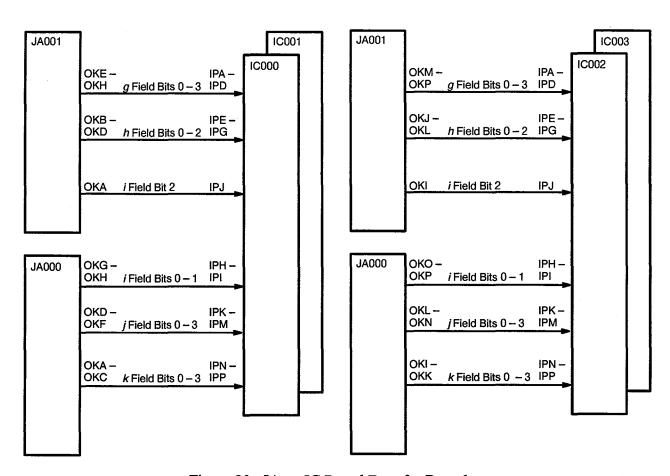

| Figure 84 | 4. Instruction Issue Block Diagram                     | 175 |

| Figure 8: | 5. Format for a 1-parcel Instruction                   | 176 |

| Figure 80 | 5. Format for a 3-parcel Instruction                   | 176 |

| Figure 8' | 7. Format for a 4-parcel Instruction                   | 177 |

| Figure 88 | B. Bjk (Exchange P) Fan-out Bits                       | 188 |

| Figure 89 | 9. JA-to-IC Parcel Data for Branches                   | 189 |

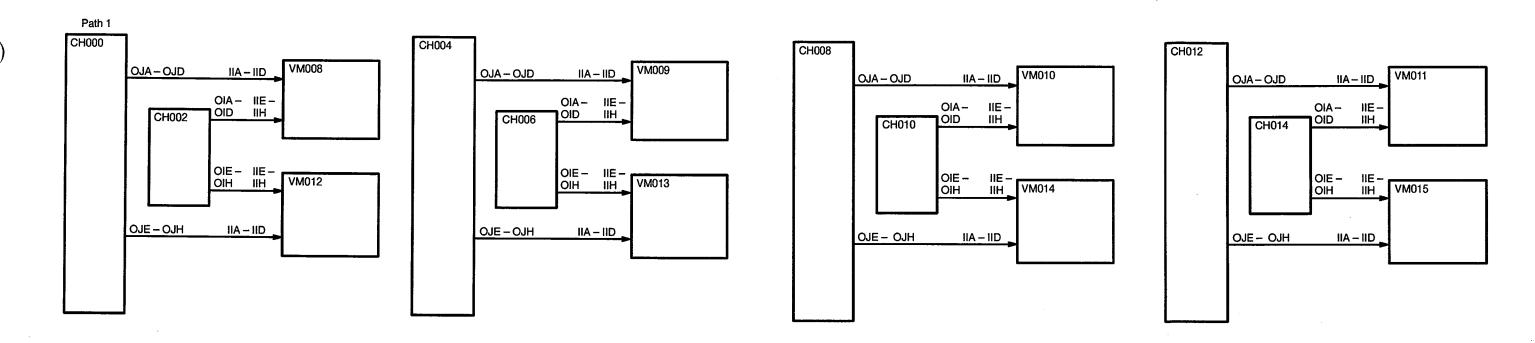

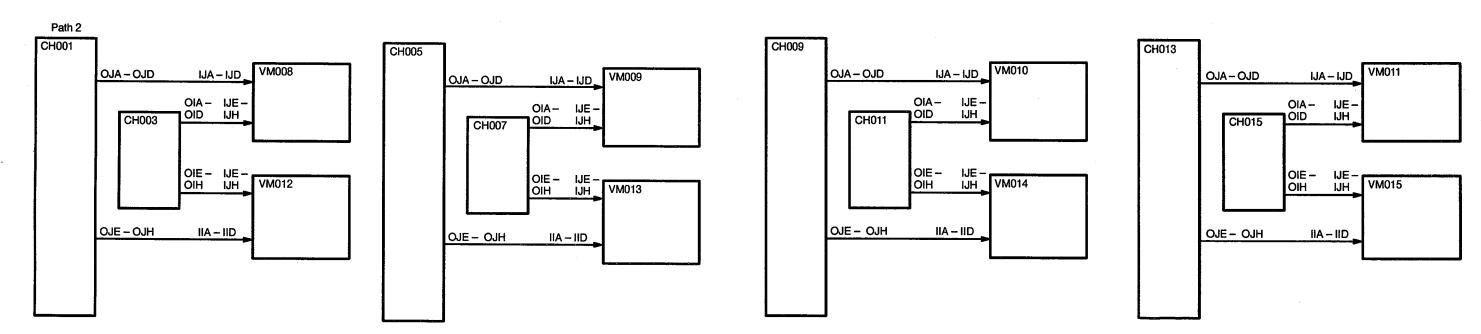

| Figure 90 | D. Path 1 CH to IC to JA Option                        | 190 |

| Figure 9  | Path 2 CH to IC to JA Option                           | 191 |

| Figure 92 | 2. JA Option Block Diagram                             | 193 |

| Figure 9  | Instruction Data Distribution A/S/R/T/V Registers      | 195 |

# Figures (continued)

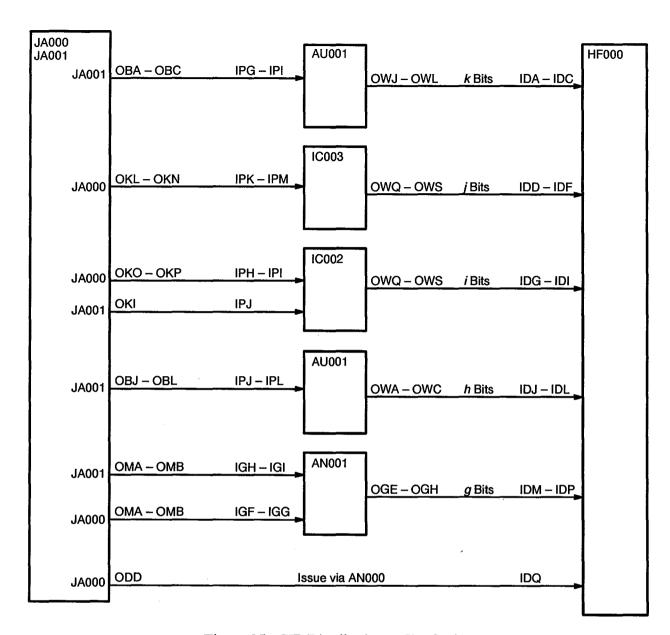

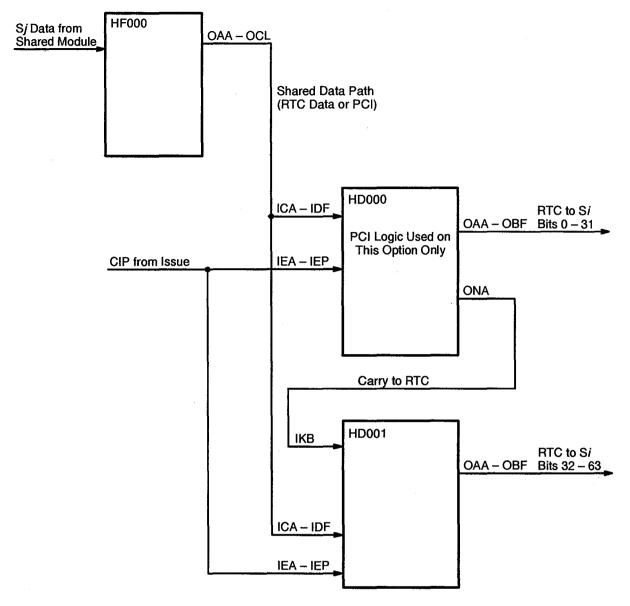

|        | Figure 94.  | CIP Distribution to HD Options                              | 196 |

|--------|-------------|-------------------------------------------------------------|-----|

|        | Figure 95.  | CIP Distribution to HF Option                               | 197 |

|        | Figure 96.  | Exchange Package                                            | 204 |

|        | Figure 97.  | RTC and PCI Block Diagram                                   | 212 |

|        | Figure 98.  | Performance Monitor Block Diagram                           | 217 |

|        | Figure 99.  | Status Registers                                            | 219 |

|        | Figure 100. | Cache Layout                                                | 226 |

|        | Figure 101. | Memory Addresses                                            | 227 |

| Tables |             |                                                             |     |

|        | Table 1.    | A/S Register Entry Codes                                    | 9   |

|        | Table 2.    | B/T Register Instructions                                   | 16  |

|        | Table 3.    | A/S Adder Instructions                                      | 19  |

|        | Table 4.    | Scalar Logical Functional Unit Instructions                 | 22  |

|        | Table 5.    | Address Logical Functional Unit Instructions                | 23  |

|        | Table 6.    | Scalar Mask Instructions                                    | 23  |

|        | Table 7.    | Address Mask Instructions                                   | 24  |

|        | Table 8.    | Transmit nm to Si Instructions                              | 25  |

|        | Table 9.    | Scalar Pop Count/Parity and Leading Zero Count Instructions | 28  |

|        | Table 10.   | Address Register Shift Instructions                         | 31  |

|        | Table 11.   | Scalar Shift Instructions                                   | 43  |

|        | Table 12.   | Recode Groups                                               | 56  |

|        | Table 13.   | Vector Register Options                                     | 64  |

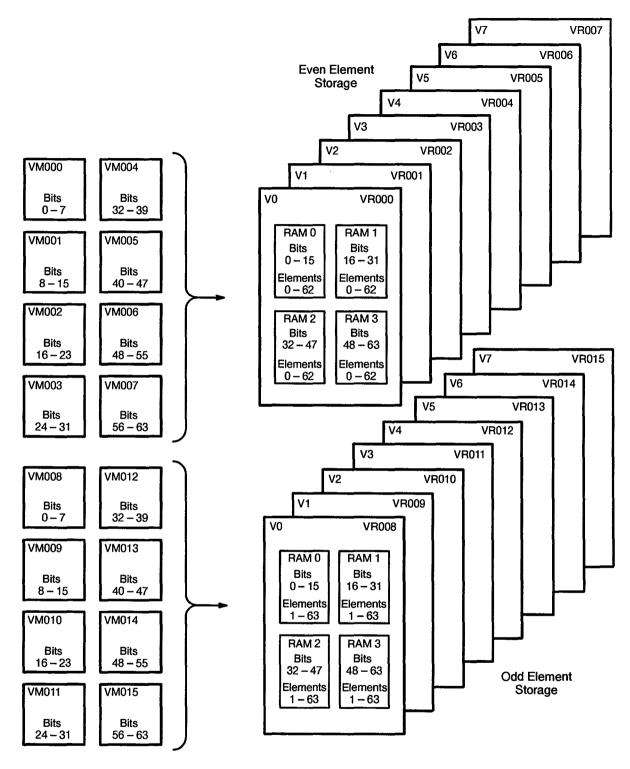

|        | Table 14.   | VM/VR Data Steering                                         | 68  |

|        | Table 15.   | Vector Logical Instructions                                 | 95  |

|        | Table 16.   | Vector Merge Instructions                                   | 96  |

|        | Table 17.   | Vector Mask Operations                                      | 98  |

|        | Table 18.   | Vector Mask Test Operations                                 | 99  |

|        | Table 19.   | Iota Instruction                                            | 100 |

|        | Table 20.   | Vector Add Instructions                                     | 103 |

|        | Table 21.   | Vector Shift Instructions                                   | 107 |

|        | Table 22.   | Vector Population/Parity Instructions                       | 118 |

|        | Table 23.   | Floating-point Add Functional Unit Instructions             | 123 |

|        | Table 24.   | Reciprocal Approximation Values                             | 135 |

#### Tables (continued)

| Table 25. | Floating-point Reciprocal Approximation              |     |

|-----------|------------------------------------------------------|-----|

|           | Instructions                                         | 139 |

| Table 26. | Floating-point Multiply Functional Unit Instructions | 146 |

| Table 27. | Bit Matrix Multiply Instructions                     | 157 |

| Table 28. | IC Options                                           | 163 |

| Table 29. | Read-out Path Codes                                  | 179 |

| Table 30. | Interrupt Modes Register Bit Assignments             | 206 |

| Table 31. | Flag Register Bit Assignments                        | 207 |

| Table 32. | LAT Fields                                           | 209 |

| Table 33. | RTC and PC Instructions                              | 213 |

| Table 34. | Performance Monitor                                  | 214 |

| Table 35. | Performance Monitor Instructions                     | 215 |

| Table 36. | Status Register (SR0)                                | 220 |

| Table 37. | Status Register 4 (SR4)                              | 221 |

| Table 38. | Destination Codes                                    | 221 |

| Table 39. | Status Register 7 Bit Definitions                    | 222 |

| Table 40. | Register Parity Error Code                           | 222 |

| Table 41. | CH Option Bits                                       | 228 |

| Table 42  | Scalar Cache Instructions                            | 228 |

|            |  | · |  |  |  |

|------------|--|---|--|--|--|

| $\bigcirc$ |  |   |  |  |  |

|            |  |   |  |  |  |

|            |  |   |  |  |  |

|            |  |   |  |  |  |

|            |  |   |  |  |  |

|            |  |   |  |  |  |

|            |  |   |  |  |  |

|            |  |   |  |  |  |

|            |  |   |  |  |  |

|            |  |   |  |  |  |

|            |  |   |  |  |  |

|            |  |   |  |  |  |

|            |  |   |  |  |  |

|            |  |   |  |  |  |

|            |  |   |  |  |  |

|            |  |   |  |  |  |

|            |  |   |  |  |  |

|            |  |   |  |  |  |

|            |  |   |  |  |  |

|            |  |   |  |  |  |

|            |  |   |  |  |  |

|            |  |   |  |  |  |

|            |  |   |  |  |  |

|            |  |   |  |  |  |

|            |  |   |  |  |  |

|            |  |   |  |  |  |

|   | · |  |     |

|---|---|--|-----|

|   | 7 |  |     |

|   |   |  | . • |

|   |   |  |     |

|   |   |  |     |

|   |   |  |     |

|   |   |  |     |

|   |   |  |     |

|   |   |  |     |

|   |   |  |     |

|   |   |  |     |

|   |   |  |     |

|   |   |  |     |

| · |   |  |     |

|   |   |  |     |

|   |   |  |     |

|   |   |  |     |

|   |   |  |     |

|   |   |  |     |

|   |   |  |     |

|   |   |  |     |

|   |   |  |     |

|   |   |  |     |

|   |   |  |     |

|   |   |  |     |

|   |   |  |     |

|   |   |  | ·   |

|   |   |  | ·   |

| •       | • |    |   |   |   |                    |   |      |     |   |

|---------|---|----|---|---|---|--------------------|---|------|-----|---|

|         |   |    |   |   |   |                    |   |      |     |   |

|         | N |    |   |   |   |                    |   |      | •   |   |

|         |   |    |   |   |   |                    |   |      |     |   |

|         |   |    |   |   |   |                    |   |      |     |   |

|         |   |    |   |   |   |                    |   |      |     |   |

|         |   |    |   |   |   |                    |   |      |     |   |

| •       |   |    |   |   |   |                    |   |      |     |   |

|         |   |    |   |   | • |                    |   |      |     |   |

|         |   | ٠. |   |   |   |                    |   |      |     |   |

|         |   |    |   |   |   |                    |   |      |     |   |

|         | A |    |   |   |   |                    |   |      |     |   |

| •       |   |    |   |   |   |                    |   |      |     |   |

|         | , |    |   |   |   |                    |   |      |     |   |

|         |   |    |   |   |   |                    |   |      |     |   |

| · ·     |   |    |   |   |   |                    |   |      |     |   |

|         |   | •  |   |   |   |                    |   |      |     |   |

|         |   |    |   |   |   | -                  |   |      |     |   |

|         |   |    |   | • |   |                    |   |      |     |   |

|         |   |    |   |   |   |                    |   | . •. |     |   |

|         |   |    |   |   |   |                    |   |      |     |   |

|         |   |    | • |   |   |                    |   |      | *   |   |

| 419<br> |   |    |   |   |   |                    |   |      |     |   |

|         |   |    |   |   |   |                    |   |      |     |   |

|         |   |    |   |   |   |                    |   |      |     | : |

|         |   |    |   |   |   |                    |   |      |     |   |

|         |   |    |   |   |   |                    |   |      |     |   |

|         |   |    |   |   |   |                    |   |      |     |   |

|         |   |    |   |   |   |                    |   |      |     |   |

|         |   |    |   |   |   |                    |   | •    |     |   |

|         |   |    |   |   |   |                    |   |      |     |   |

|         |   |    |   |   | • |                    |   |      |     |   |

|         | • | •  |   |   |   |                    |   |      |     | 1 |

|         |   |    |   |   |   |                    |   |      |     | 1 |

|         |   |    |   | • |   |                    |   |      |     |   |

|         |   |    |   |   |   |                    |   |      |     | ı |

|         |   |    |   |   |   |                    |   |      |     | 1 |

|         |   |    |   |   |   |                    |   |      | ,   |   |

|         |   |    |   |   |   |                    |   |      | ,   | 1 |

|         |   |    |   |   |   | *                  |   |      |     | l |

|         |   |    |   |   |   |                    | , |      |     |   |

|         |   |    | * |   |   |                    |   |      |     |   |

|         |   |    |   |   |   |                    |   |      | ı   |   |

|         |   |    |   |   |   | * ** <sub>**</sub> |   |      | . ' |   |

|         |   |    |   |   |   |                    |   |      | 1   |   |

|         |   |    |   |   |   |                    |   |      |     |   |

|         | • |    | • |   |   |                    |   |      |     |   |

|         |   |    |   |   |   |                    |   | •    | 1   |   |

|         |   |    | • |   |   |                    |   |      | 1   |   |

|         |   |    |   |   |   |                    |   |      |     |   |

#### **CP02 MODULE**

#### **CP02 General Description**

The CP02 module contains the central processing unit (CPU) for the CRAY T90 series computer systems. There is one CPU per CP02 module. The CRAY T90 series CPU is compatible with the CRAY C90 series CPU. This means that code compiled on the CRAY C90 series system will run on a CRAY T90 series system.

There have been many enhancements to the CRAY T90 series CPU and several new instructions added to increase the performance. Figure 1 illustrates CP module components. Figure 2 and Figure 3 show the basic functions and locations of all options on a CP module. Figure 4 shows a block diagram of the CPU.

The CP modules are arranged in stacks in the system. A CRAY T94 system contains one stack of as many as four modules. A CRAY T916 systems contains up to two stacks of as many as eight modules. A CRAY T932 system contains up to four stacks of as many as 8 modules.

Each module in a stack is independent of the other CP modules in the stack; there are no interconnections between modules in a stack. The CP modules connect directly with either the memory modules, as in the CRAY T94 system, or with the system interconnect board (SIB), as in larger systems.

#### **Module Assembly Components**

Refer to Figure 1 for an illustration of the CP module assembly components. This illustration is provided to show the basic components that are part of all mainframe modules. Sizes of various components differ between modules.

- A Flow Block, Board 1

- **B** Optical Receiver

- C PC Board Edge Shim

- D Maintenance Connector Flex Assembly

- E Fiber-optic Spool Assembly

- F Voltage Regulator Board Assembly

- **G** Maintenance Connector

- H Fiber-optic Coupler

- I Flow Block, Board 2

- J PC Logic Board 2

- K Outer Rail

- L Inner Rail

- M PC Logic Board 1

Figure 1. CP Module Assembly Components

| HB000                      |                                               |                                                      |                                               |                                                  |                                                  |                                                |                                                        |                                              |

|----------------------------|-----------------------------------------------|------------------------------------------------------|-----------------------------------------------|--------------------------------------------------|--------------------------------------------------|------------------------------------------------|--------------------------------------------------------|----------------------------------------------|

| I/O<br>Control             |                                               |                                                      |                                               |                                                  |                                                  |                                                |                                                        |                                              |

|                            | NA000                                         | RC000                                                | TZ000                                         | HM000                                            | MZ000                                            | TW010                                          | RC001                                                  | NA001                                        |

|                            | Fit Mult                                      | Recip                                                | Clock                                         | Logic<br>Monitor                                 | BS Fanout                                        | Not Used                                       | Recip                                                  | Fit Mult                                     |

| TW000                      | NC000                                         | RB000                                                | FA000                                         | TW006                                            | FA001                                            | OA002                                          | RB001                                                  | NC001                                        |

| Not Used                   | Fit Mult                                      | Recip                                                | Flt Add<br>Coeff                              | Not Used                                         | Fit Add<br>Coeff                                 | BMM<br>and<br>Parity                           | Recip                                                  | Flt Mult                                     |

| TW002                      | VM007                                         | AU000                                                | VM006                                         | SS000                                            | OA000                                            | OA001                                          | VM014                                                  | VM015                                        |

| Not Used                   | Vector Even<br>R Bit 60 – 63<br>W Bit 56 – 63 | A/S Reg<br>Bits 48 - 55                              | Vector Even<br>R Bit 52 – 55<br>W Bit 48 – 55 | Shift<br>Pop<br>LZ                               | BMM<br>and<br>Parity                             | BMM<br>and<br>Parity                           | Vector Odd<br>R Bit 52 – 55<br>W Bit 48 – 55           | Vector Odd<br>R Bit 60 – 63<br>W Bit 56 – 63 |

| HD000                      | VM005                                         | AT000                                                | VM004                                         | JA000                                            | VA000                                            | CG000                                          | VM012                                                  | VM013                                        |

| CIP<br>Exchange<br>Package | Vector Even<br>R Bit 44 – 47<br>W Bit 40 – 47 | A/S Reg<br>Bits 32 - 39                              | Vector Even<br>R Bit 36 – 39<br>W Bit 32 – 39 | Issue<br>Control                                 | Vector<br>Control                                | Check-bit<br>Generation                        | Vector Odd<br>R Bit 36 – 39<br>W Bit 32 – 39           | Vector Odd<br>R Bit 44 – 47<br>W Bit 40 – 47 |

| VF000                      | VM003                                         | AS001                                                | VM002                                         | ВТ000                                            | CD000                                            | CB000                                          | VM010                                                  | VM011                                        |

| Vector<br>Control          | Vector Even<br>R Bit 28 – 31<br>W Bit 24 – 31 | A/S Reg<br>Bits 16 – 23                              | Vector Even<br>R Bit 20 – 23<br>W Bit 16 – 23 | B/T/P Reg<br>Bits 0 – 15<br>Bits 32 – 47         | Ports E<br>Cache<br>HIT                          | Ports C                                        | Vector Odd<br>R Bit 20 – 23<br>W Bit 16 – 23           | Vector Odd<br>R Bit 28 – 31<br>W Bit 24 – 31 |

| TW004                      | VM001                                         | AR000                                                | VM000                                         | CH010                                            | CH008                                            | CA000                                          | VM008                                                  | VM009                                        |

| Not Used                   | Vector Even<br>R Bit 12 – 15<br>W Bit 8 – 15  | A/S Reg<br>Bits 0 - 7                                | Vector Even<br>R Bit 4 – 7<br>W Bit 0 – 7     | Data MUX<br>Cache<br>20 – 23<br>52 – 55          | Data MUX<br>Cache<br>16 – 19<br>48 – 51          | Ports A, A'                                    | Vector Odd<br>R Bit 4 – 7<br>W Bit 0 – 7               | Vector Odd<br>R Bit 12 – 15<br>W Bit 8 – 15  |

| I/O to Mem<br>SBCDBD       | CC000<br>Ports<br>D                           | IC000<br>Inst<br>Buffers<br>Bit 0 - 7<br>Bit 32 - 39 | CH002<br>Data MUX<br>Cache<br>4-7<br>36-39    | CH014<br>Data MUX<br>Cache<br>28 – 31<br>60 – 63 | CH012<br>Data MUX<br>Cache<br>24 – 27<br>56 – 59 | CH000<br>Data MUX<br>Cache<br>0 - 3<br>32 - 35 | IC002<br>Inst<br>Buffers<br>Bit 16 – 23<br>Bit 48 – 55 | VF002<br>Vector<br>Control                   |

| HA002                      | CF004                                         | CF000                                                | CK000                                         | CH006                                            | CH004                                            | CK002                                          | CF002                                                  | TW008                                        |

| I/O to Mem<br>SBCDBD       | Write Data<br>Conflicts                       | Write Data<br>Conflicts                              | Data<br>Steering                              | Data MUX<br>Cache<br>12 - 15<br>44 - 47          | Data MUX<br>Cache<br>8 – 11<br>40 – 43           | Data<br>Steering                               | Write Data<br>Conflicts                                | Not Used                                     |

| HG000                      | CI000                                         | C1000                                                | CI004                                         | CJ004                                            | CI002                                            | CJ002                                          | CI006                                                  | CJ006                                        |

| Maint<br>Channel           | Section<br>Driver<br>Section 0                | Section<br>Receiver<br>Section 0                     | Section<br>Driver<br>Section 4                | Section<br>Receiver<br>Section 4                 | Section<br>Driver<br>Section 2                   | Section<br>Receiver<br>Section 2               | Section<br>Driver<br>Section 6                         | Section<br>Receiver<br>Section 6             |

| ZE                         | 3008                                          | ZB00                                                 | 0 [                                           | ZB004                                            |                                                  | ZB002                                          | Z                                                      | B006                                         |

Figure 2. Option Layout Board 1

| 3                                       |                                               | [                                             | į                                                |                                                  |                                               |                                              |                                          | HC000                      |

|-----------------------------------------|-----------------------------------------------|-----------------------------------------------|--------------------------------------------------|--------------------------------------------------|-----------------------------------------------|----------------------------------------------|------------------------------------------|----------------------------|

|                                         |                                               |                                               |                                                  |                                                  |                                               |                                              |                                          | I/O Relay<br>Data          |

| VD001                                   | AM001                                         | TW011                                         |                                                  | HM001                                            |                                               | AM002                                        | ND000                                    |                            |

| Fit Mult                                | Integer<br>Multi                              | Not Used                                      |                                                  | Logic<br>Monitor                                 |                                               | Integer<br>Multi                             | Fit Mult                                 |                            |

| VB001                                   | RA001                                         | OA005                                         | FB001                                            | TW007                                            | FB000                                         | RA000                                        | NB000                                    | TW001                      |

| Fit Mult                                | Recip                                         | BMM<br>and<br>Parity                          | Fit Add<br>Exponent                              | Not Used                                         | Fit Add<br>Exponent                           | Recip                                        | Fit Mult                                 | Not Used                   |

| VR015                                   | VR014                                         | OA004                                         | OA003                                            | V\$000                                           | VR006                                         | AU001                                        | VR007                                    | TW003                      |

| Vector 7<br>Odd                         | Vector 6<br>Odd                               | BMM<br>and                                    | BMM<br>and                                       | Vector<br>Shift                                  | Vector 6<br>Even                              | A/S Reg                                      | Vector 7<br>Even                         | Not Used                   |

| Bits 56 - 59                            | Bits 48 - 51                                  | Parity                                        | Parity                                           | Office                                           | Bits 48 - 51                                  | Bits 56 - 63                                 | Bits 56 - 59                             |                            |

| VR013<br>Vector 5<br>Odd                | VR012<br>Vector 4<br>Odd                      | CG001<br>Checkbit                             | VA001<br>Vector                                  | JA001<br>Issue                                   | VR004<br>Vector 4<br>Even                     | AT001<br>A/S Reg                             | VR005<br>Vector 5<br>Even                | HD001<br>CIP               |

| Bits 40 - 43                            | Bits 32 - 35                                  | Generation                                    | Control                                          | Control                                          | Bits 32 - 35                                  | Bits 40 - 47                                 | Bits 40 - 43                             | Exchange<br>Package        |

| VR011<br>Vector 3<br>Odd                | VR010<br>Vector 2<br>Odd                      | CB001<br>Port<br>C'                           | CD001 Port E Cache                               | BT001<br>B/T/P Reg<br>Bits 16 – 31               | VR002<br>Vector 2<br>Even                     | AS002<br>A/S Reg                             | VR003<br>Vector 3<br>Even                | VF001<br>Vector<br>Control |

| Bits 24 – 27                            | Bits 16 - 19                                  |                                               | Control                                          | Bits 48 – 63                                     | Bits 16 19                                    | Bits 24 - 31                                 | Bits 24 - 27                             | Control                    |

| VR009<br>Vector 1<br>Odd<br>Bits 8 – 11 | VR008<br>Vector 0<br>Odd<br>Bits 0 – 3        | CA001<br>Port<br>B, B'                        | CH009<br>Data MUX<br>Cache<br>16 – 19<br>48 – 51 | CH011<br>Data MUX<br>Cache<br>20 23<br>52 55     | VR000<br>Vector 0<br>Even<br>Bits 0 – 3       | AS000<br>A/S Reg<br>Bits 8 – 15              | VR001<br>Vector 1<br>Even<br>Bits 8 – 11 | AN000<br>Address<br>Multi  |

| VF003                                   | IC003                                         | CH001                                         | CH013                                            | CH015                                            | CH003                                         | IC001                                        | TW005                                    | HA001                      |

| Vector<br>Control                       | Inst<br>Buffers<br>Bit 24 – 31<br>Bit 56 – 63 | Data MUX<br>Cache<br>0 - 3<br>32 - 35         | Data MUX<br>Cache<br>24 – 27<br>56 – 59          | Data MUX<br>Cache<br>28 – 31<br>60 – 63          | Data MUX<br>Cache<br>4 - 7<br>36 - 39         | Inst<br>Buffers<br>Bit 8 – 15<br>Bit 40 – 47 | Not Used                                 | I/O<br>SECDED              |

| TW009<br>Not Used                       | CF003<br>Write Data<br>Conflicts              | CK003<br>Data<br>Steering<br>Cache<br>Control | CH005<br>Data MUX<br>Cache<br>8 - 11<br>40 - 43  | CH007<br>Data MUX<br>Cache<br>12 - 15<br>44 - 47 | CK001<br>Data<br>Steering<br>Cache<br>Control | CF001<br>Write Data<br>Conflicts             | CF005<br>Write Data<br>Conflicts         | HA003<br>Maint<br>Channel  |

| CI007                                   | CJ007                                         | CI003                                         | CJ003                                            | CI005                                            | CJ005                                         | Cl001                                        | CJ001                                    | HF000                      |

| Section<br>Driver<br>Section 7          | Section<br>Receiver<br>Section 7              | Section<br>Driver<br>Section 3                | Section<br>Receiver<br>Section 3                 | Section<br>Driver<br>Section 5                   | Section<br>Receiver<br>Section 5              | Section<br>Driver<br>Section 1               | Section<br>Receiver<br>Section 1         | Perf<br>Monitor            |

Figure 3. Option Layout Board 2

Figure 4. CPU Block Diagram

|   |   |   | * . |   |   |

|---|---|---|-----|---|---|

|   |   |   |     |   |   |

|   |   |   |     |   |   |

|   |   |   |     |   |   |

|   |   |   |     |   |   |

|   |   |   |     |   | • |

|   | • |   |     |   |   |

|   |   |   |     |   |   |

|   |   |   |     |   |   |

|   |   |   |     |   |   |

| , |   |   | •   |   |   |

|   |   |   |     |   |   |

|   |   |   |     |   |   |

|   |   |   |     |   | * |

|   |   |   |     |   |   |

|   |   |   |     | • |   |

| • |   |   |     |   |   |

|   |   |   |     |   |   |

|   |   |   |     |   |   |

|   |   |   |     |   |   |

|   |   |   |     |   |   |

|   |   |   |     |   |   |

|   |   | · |     |   |   |

|   |   |   |     |   |   |

| ÷ |   |   |     |   |   |

|   | • |   |     |   |   |

|   |   |   |     |   |   |

|   |   |   |     |   |   |

|   |   |   |     |   |   |

|   |   |   | ·   |   |   |

|   |   |   |     |   |   |

|   |   |   |     |   |   |

|   |   |   |     |   |   |

|   |   |   |     |   |   |

|   |   |   |     |   |   |

|   |   |   |     |   |   |

|   |   |   |     |   |   |

|  |                                       |   |   | i    |  |

|--|---------------------------------------|---|---|------|--|

|  |                                       |   |   | 4. 1 |  |

|  |                                       |   |   |      |  |

|  |                                       |   |   |      |  |

|  |                                       |   | • |      |  |

|  |                                       |   |   |      |  |

|  |                                       |   |   |      |  |

|  |                                       |   |   |      |  |

|  | · · · · · · · · · · · · · · · · · · · |   |   |      |  |

|  |                                       |   |   |      |  |

|  |                                       | , |   | •    |  |

|  |                                       |   |   |      |  |

|  |                                       |   |   |      |  |

|  |                                       |   |   |      |  |

|  |                                       |   |   |      |  |

|  |                                       |   |   |      |  |

|  |                                       |   |   |      |  |

|  |                                       |   |   |      |  |

## ADDRESS AND SCALAR REGISTERS

The address and scalar registers are located on the same options. The following subsections describe the address and scalar registers.

## **Address Registers**

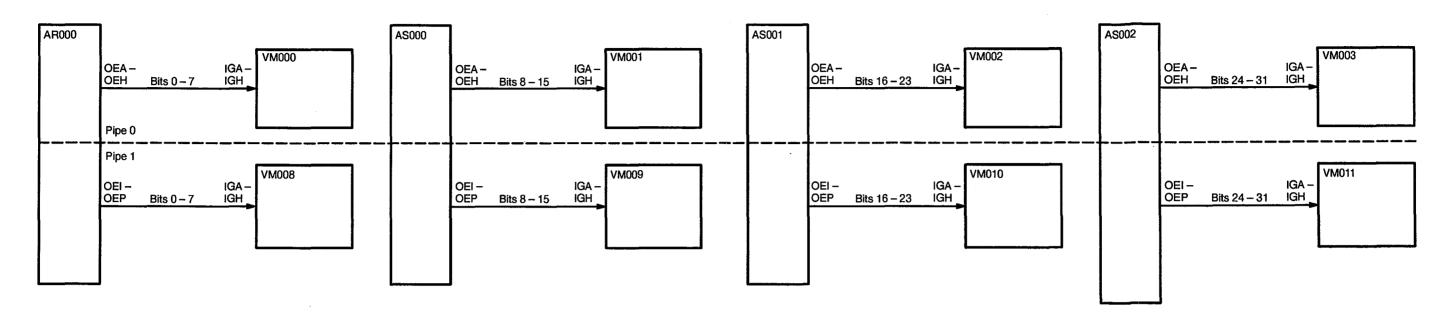

The address and scalar registers are contained on eight options: one AR option, three AS options, two AT options, and two AU options. Each CRAY T90 series CPU contains eight address registers designated A0 through A7. Each register is 64 bits wide (32 bits in C90 mode) and performs the following functions:

- Determines addresses for memory references

- Provides memory reference indexing

- Provides loop control

- Determines shift counts

- Provides I/O channel set-up

- Determines I/O channel status

- Receives results from scalar leading zero and pop count

- Determines vector length

- Provides an exchange address (monitor mode only)

- Provides an index for shared registers and B and T instructions

- Provides operands and results for address add and address multiply

- Transfers data to and from scalar registers

- Provides integer-to-floating-point conversion

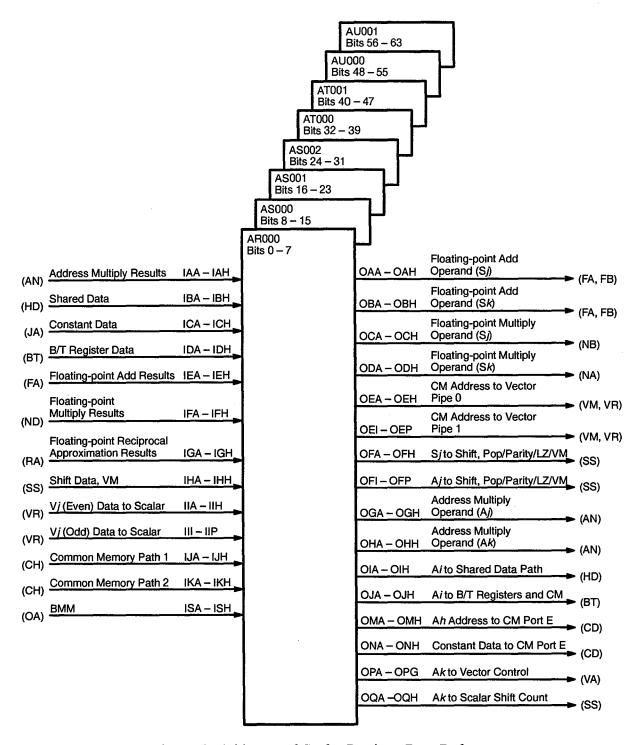

As shown in Figure 5, the AR000, AS000, AS001, AS002, AT000, AT001, AU000, and AU001 options each contain an 8-bit slice of the address registers. Figure 5 also illustrates the input and output data paths for the address and scalar registers.

Figure 5. Address and Scalar Register Data Paths

#### **Entry Codes**

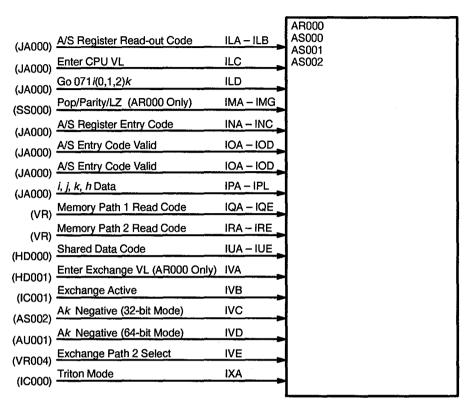

As part of the instruction decode on the JA option, the JA option sends an A/S entry code to the A/S register options; this code generates the control necessary to complete the operations. The operand data is then transmitted to the appropriate resources, and a destination delay chain is entered on the option. Refer to Table 1 for the address/scalar (A/S) register entry codes and to Figure 6 for an illustration of the A/S control terms.

Table 1. A/S Register Entry Codes

| Entry Code | Instruction                                             |

|------------|---------------------------------------------------------|

| 0          | 020i Constants                                          |

| 1          | 023 <i>ij</i> 0 S <i>j</i>                              |

| 2          | 023ij1 VL data                                          |

| 3          | 024 <i>ijk</i> B data                                   |

| 4          | 030,031 <i>ijk</i> Add                                  |

| 5          | 026 <i>ij</i> (0 – 3), 027 <i>ij</i> (0 – 1) pop/par/lz |

| 6          | 032 <i>ijk</i> A multiply                               |

| 7          | 022 ijk, 04 (2 - 3) jk/mask data                        |

| 10         | N/A                                                     |

| 11         | 073i (2 - 3) 0 VM data                                  |

| 12         | N/A                                                     |

| 13         | N/A                                                     |

| 14         | 04 (4 - 7) ijk, 05 (0 - 1) ijk Logical                  |

| 15         | N/A                                                     |

| 16         | 05 (2 - 5) ijk, 05 (6 - 7) ijk Shift                    |

| 17         | N/A                                                     |

Figure 6. A/S Control Terms

#### A Register Memory References

Refer to Figure 7 for an A/S-register-to-memory block diagram. The address registers write or read 1 word of memory per instruction. The B registers provide intermediate storage for the address registers. B registers perform memory block references that enable a group of operands to be read from memory with one instruction. These operands are then used by the A registers to generate results that are sent to the B registers and block-stored to memory. Using the B registers as buffer storage is advantageous because it takes fewer clock periods to do a block reference than to issue several individual address or scalar references.

The A registers also have an access path to cache memory. This provides access to common memory data without having to reference memory directly. If the requested address resides in cache, a *cache hit* is initiated and the data is read from cache memory instead of common memory.

#### **Special Register Values**

The A0 register has special features that the other A registers do not have. The A0 register holds the starting address for all block transfers for the B, T, and V registers and branch control. A0 is the only register that can be tested for equal-to-zero, not-equal-to-zero, positive, or negative conditions using A0 conditional branch instructions. This register also has a special feature for reading data.

If A0 is specified as an operand in the h, j, or k field of an instruction, it will not send the actual contents of the register. Instead, the register sends a value of 0 if A0 is used in the j or k field, or it sends a value of 1 if A0 is used in the k field. If A0 is used in the k field, the actual contents of the A0 register are sent.

Because the A registers in this system are now 64 bits wide, special Triton mode instructions have been implemented. These instructions are part of the extended instruction set (EIS). These instructions make the A registers functionally equal to S registers and enable A registers to be shifted and logical operations to be performed. To execute these instructions, an EIS 005400 instruction must precede the actual A register instruction. If a Triton mode instruction is issued while the system is in C90 mode, the results of the operation are undefined.

Figure 7. Memory to A/S-register Block Diagram

#### **Scalar Registers**

The CPU contains eight scalar registers that are designated S0 through S7 and are 64 bits in length. The scalar registers are contained on the AR, AS, AT, and AU options (refer again to Figure 5).

The scalar registers send operands to, and get results from, the scalar functional units and the floating-point functional units. The functional units perform integer and floating-point arithmetic as well as logical operations. The scalar registers read and write central memory through the T registers and also read and write the data cache. In addition, there are paths to the vector registers, vector mask, real-time clock, status register, programmable clock interrupt, and the performance monitor.

#### Instruction Issue

When an instruction issues, the scalar register receiving the data is reserved until the result is latched in the register. If an instruction in the current instruction parcel (CIP) register requires the reserved result register, that CIP instruction holds issue until the register is available. The S0 register, however, is an exception. If the S0 register is reserved as a result register and is needed as an Sj or Sk operand in a following instruction, no hold issue occurs because the S0 register has special register values as an operand.

The issue hardware also develops scalar functional unit codes. These codes select the input terms to be gated from the proper functional unit into the scalar register multiplexer.

#### **S Register Memory References**

The scalar registers write or read 1 word of memory per instruction. The T registers provide intermediate storage for the scalar registers. T registers can perform memory block references, enabling a group of operands to be read from memory with one instruction. These operands are then used by the scalar registers to generate results that can be sent to the T registers and block-stored to memory. Using the T registers as buffer storage is advantageous because it takes fewer clock periods to do a block reference than to issue several individual scalar references.

The S registers also have an access path to cache memory. This provides access to common memory data without having to reference memory directly. If the requested address resides in cache, a *cache hit* is initiated and the data is read from cache instead of from common memory.

#### **Special Register Values**

S0 has special register values when Sj or Sk is used as an operand. When the j field equals 0, the value sent out is 0, no matter what value is stored in S0. When the k field is 0, bit 63 is set to a 1.

#### Lower/Upper Scalar Register Load

It is possible to load either the lower- or upper-half of a scalar register with a 32-bit quantity. The following four instructions load constants into scalar registers.

- 040i00 nm Si exp: loads the quantity nm into the lower 32 bits of register Si. The upper 32 bits are cleared.

- 041*i*00 *nm* S*i exp*: loads the one's complement of *nm* into the lower 32 bits of register S*i*. The upper 32 bits are all 1's.

- 040*i*20 *nm* S*i exp*: loads the quantity *nm* into the lower 32 bits of register S*i*. The upper 32 bits are unchanged.

- 040*i*40 S*i exp*: loads the quantity *nm* into the upper 32 bits of register S*i*. The lower 32 bits are unchanged.

#### **BAND T REGISTERS**

Each CPU contains 64 (100<sub>8</sub>) B registers and 64 T registers. The B and T registers act as intermediate registers for the address and scalar registers, respectively. Each B and T register contains 64 bits.

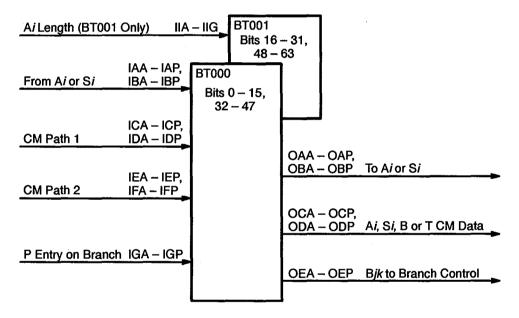

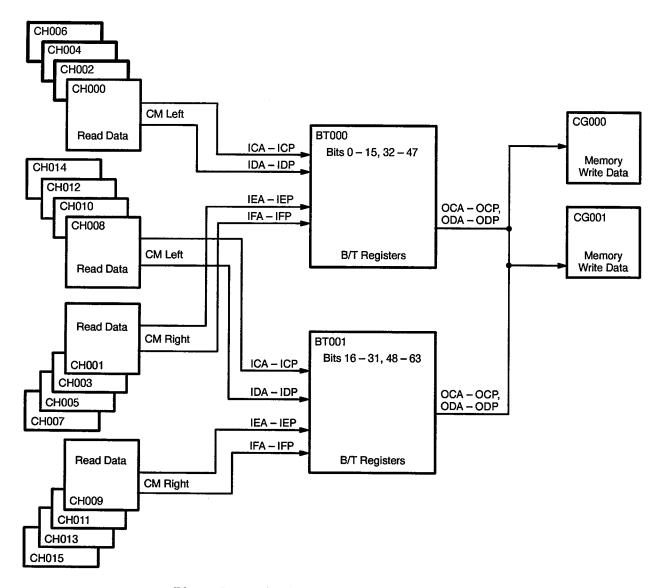

Two BT options, BT000 and BT001, contain the B and T registers. Each option contains 32 bits of each register. BT000 contains bits 00 through 15 and 32 through 47. BT001 contains bits 16 through 31 and 48 through 63. As shown in Figure 8, the B and T registers can be loaded from the address and scalar registers, common memory, and branch control.

Figure 8. B and T Register Inputs and Outputs

The B and T registers are used primarily for block transfers to and from common memory. Refer to Table 2 for a list of the B and T register instructions. Refer also to Figure 9 for a B/T-register-to-memory block diagram.

Table 2. B/T Register Instructions

| Instruction      | CAL                         | Description                                                                                            |

|------------------|-----------------------------|--------------------------------------------------------------------------------------------------------|

| 0050 <i>jk</i>   | J B <i>jk</i>               | Jump to Bjk                                                                                            |

| 0051 <i>jk</i> O | JINV B <i>jk</i>            | Jump to Bjk (invalidate instruction buffers)                                                           |

| 024 <i>ijk</i> D | Ai Bjk                      | Transmit (Bjk) to Ai                                                                                   |

| 025 <i>ijk</i> D | Bjk Ai                      | Transmit (Ai) to Bjk                                                                                   |

| 034 <i>ijk</i> D | B <i>jk</i> A <i>i</i> , A0 | Transmit (Ai) words from common memory starting at address (A0) to B registers starting at register jk |

| 035 <i>ijk</i> D | ,A0 B <i>jk</i> ,A <i>i</i> | Transmit (Ai) words from B registers starting at register jk to memory starting at address (A0)        |

| 036 <i>ijk</i> D | T <i>jk</i> Ai, A0          | Transmit (Ai) words from memory starting at address (A0) to T register starting at register <i>jk</i>  |

| 037 <i>ijk</i> D | ,A0 T <i>jk</i> ,A <i>i</i> | Transmit (Ai) words from T registers starting at register jk to memory starting at address (A0)        |

| 074 <i>ijk</i>   | Si Tjk                      | Transmit (Tjk) to Si                                                                                   |

| 075 <i>ijk</i>   | T <i>jk</i> Si              | Transmit (Si) to Tjk                                                                                   |

O denotes a maintenance mode instruction only.

D denotes a difference between Triton mode and C90 mode.

Figure 9. B/T-register-to-memory Block Diagram

|  |       | 1   |

|--|-------|-----|

|  |       | 1   |

|  |       |     |

|  |       | 1   |

|  |       | 1   |

|  |       | . 1 |

|  |       | . 1 |

|  |       | 1   |

|  |       | 1   |

|  |       | 1   |

|  |       |     |

|  |       | 1   |

|  | -     | !   |

|  | ÷     |     |

|  |       |     |

|  |       |     |

|  |       |     |

|  |       |     |

|  |       |     |

|  | • . • | •   |

|  |       |     |

|  |       |     |

|  |       |     |

|  |       | •   |

|  |       | . • |

|  |       |     |

|  |       |     |

|  |       |     |

|  |       |     |

|  |       |     |

|  |       |     |

|  |       |     |

|  |       |     |

|  |       |     |

|  |       |     |

|  |       |     |

|  |       |     |

|  |       |     |

|   | 1   |

|---|-----|

|   |     |

|   |     |

|   |     |

|   | 1   |

|   |     |

|   |     |

|   |     |

|   | * 1 |

| , | 1   |

|   | 1   |

|   | 1   |

|   |     |

|   |     |

|   |     |

|   | e e |

|   |     |

|   |     |

# ADDRESS/SCALAR ADD

The address and scalar registers are contained on eight options: one AR option, three AS options, two AT options, and two AU options. Each option contains 8 bits of the 64-bit address registers. These options also contain the address and scalar add functional unit. Table 3 describes the instructions that use the address and scalar add functional unit.

Table 3. A/S Adder Instructions

| Instruction                  | CAL                  | Description                                                                              |  |  |  |  |

|------------------------------|----------------------|------------------------------------------------------------------------------------------|--|--|--|--|

| 030 <i>ijk</i> D             | Ai Aj+Ak             | Transmit integer sum of (A)) and (Ak) to Ai                                              |  |  |  |  |

| 030 <i>i</i> 0 <i>k</i> D    | Ai Ak <sup>S</sup>   | Transmit (Ak) to Ai                                                                      |  |  |  |  |

| 030 <i>ij</i> 0 <sup>D</sup> | Ai Aj+1 <sup>S</sup> | Transmit integer sum of (Aj) and 1 to Ai                                                 |  |  |  |  |

| 031 <i>ijk</i> D             | Ai Aj–Ak             | Transmit integer difference of (Aj) and (Ak) to Ai                                       |  |  |  |  |

| 031 <i>i</i> 0 <i>k</i> D    | Ai –Ak <sup>S</sup>  | Transmit inverse of (Ak) to Ai                                                           |  |  |  |  |

| 031 <i>ij</i> 0 <sup>D</sup> | Ai Aj–1 <sup>S</sup> | Transmit integer difference of (Aj) and 1 to Ai                                          |  |  |  |  |

| 060 <i>ijk</i>               | Si Sj+Sk             | Transmit integer sum of (Sj) and (Sk) to Si                                              |  |  |  |  |

| 061 <i>ijk</i>               | Si Sj-Sk             | Transmit integer difference of (S <sub>i</sub> ) and (S <sub>k</sub> ) to S <sub>i</sub> |  |  |  |  |

| 061 <i>i</i> 0 <i>k</i>      | Si –Sk               | Transmit inverse of (Sk) to Si                                                           |  |  |  |  |

D denotes a difference between Triton mode and C90 mode.

The address add and scalar functional units perform a 64-bit add; each option performs the add function on the bits of the operands contained on that option. Carry and enable bits generated during the add are passed on to the next option, as shown in Figure 10. The 64-bit result is stored in the destination register in 4 clock periods.

S denotes a special CAL syntax.

Address/Scalar Add CPU

Figure 10. Carry Bit and Enable Bit Fanouts

### SCALAR LOGICAL

The scalar logical functional unit performs logical operations on the scalar registers. Logical operations include OR, AND, and XOR operations and merges.

Refer to Figure 11 for an illustration of the address/scalar registers. The scalar registers are contained on eight options: one AR option, three AS options, two AT options, and two AU options. Each option contains 8 bits of the 64-bit address registers. These options also contain the scalar logical functional unit. The operands are latched and the logical operation is completed in 1 clock period; the result is then entered into the proper destination register.

Figure 11. Address/Scalar Logical Block Diagram (Instructions 044*ijk* through 051*ijk*)

Table 4 and Table 5 list the instructions used in the address and scalar logical functional unit. The instructions listed in Table 5 must be preceded by a 005400 instruction; they are for Triton mode only.

Table 4. Scalar Logical Functional Unit Instructions

| Instruction             | CAL             | Description                                                                               |  |  |  |  |

|-------------------------|-----------------|-------------------------------------------------------------------------------------------|--|--|--|--|

| 044 <i>ijk</i>          | Si Sj&Sk        | Logical product of (Sj) and (Sk) to Si                                                    |  |  |  |  |

| 044 <i>ij</i> 0         | Si Sj&SB        | Sign bit of (S/) to S/                                                                    |  |  |  |  |

| 044 <i>ij</i> 0         | Si SB&Sj        | Sign bit of (Sj) to Si (Sj $\neq$ 0)                                                      |  |  |  |  |

| 045 <i>ijk</i>          | Si#Sk&Sj        | Logical product of (S) and one's complement of (Sk) to Si                                 |  |  |  |  |

| 045 <i>ij</i> 0         | Si#SB&Sj        | (Sj) with sign bit cleared to Si                                                          |  |  |  |  |

| 046 <i>ijk</i>          | Si Sj\Sk        | Logical difference of (Sj) and (Sk) to Si (Sj $\neq$ 0)                                   |  |  |  |  |

| 046 <i>ij</i> 0         | S <i>i</i> SASB | Transmit (Sj) with sign bit toggled to Si                                                 |  |  |  |  |

| 046 <i>ij</i> 0         | Si SB\Sj        | Transmit (Sj) with sign bit toggled to Si (Sj $\neq$ 0)                                   |  |  |  |  |

| 047 <i>ijk</i>          | Si#S∫\Sk        | Logical equivalence of (Sk) and (Sj) to Si                                                |  |  |  |  |

| 047 <i>i</i> 0 <i>k</i> | Si#Sk           | Transmit one's complement of (Sk) to Si                                                   |  |  |  |  |

| 047 <i>ij</i> 0         | Si#SASB         | Logical equivalence of (S) and sign bit to Si                                             |  |  |  |  |

| 047 <i>ij</i> 0         | Si#SB\Sj        | Logical equivalence of (Sj) and sign bit to Si (Sj $\neq$ 0)                              |  |  |  |  |

| 047,00                  | Si #SB          | Enter one's complement of sign bit into Si                                                |  |  |  |  |

| 050 <i>ijk</i>          | Si Sj!Si&Sk     | Logical product of (Si) and (Sk) complement ORed with logical product of (Sj) and (Sk)    |  |  |  |  |

| 050 <i>ij</i> 0         | Si Sj!Si&SB     | Scalar merge of (Si) and sign bit of (Sj) to Si                                           |  |  |  |  |

| 051 <i>ijk</i>          | Si Sj!Sk        | Logical sum of (Sj) and (Sk) to Si                                                        |  |  |  |  |

| 051 <i>i</i> 0 <i>k</i> | SiSk            | Transmit (Sk) to Si                                                                       |  |  |  |  |

| 051 <i>ij</i> 0         | Si Sj!SB        | Logical sum of (S <sub>j</sub> ) and sign bit to S <sub>i</sub> (S <sub>j</sub> $\neq$ 0) |  |  |  |  |

| 051,00                  | SiSB            | Enter sign bit into Si                                                                    |  |  |  |  |

Table 5. Address Logical Functional Unit Instructions

| Instruction             | CAL                                | Description                                                                                               |  |  |  |  |

|-------------------------|------------------------------------|-----------------------------------------------------------------------------------------------------------|--|--|--|--|

| 044 <i>ijk</i>          | Ai Aj&Ak                           | Logical product of (A) and (Ak) to Ai                                                                     |  |  |  |  |

| 045 <i>ijk</i>          | Ai#Ak&Aj                           | Logical product of (A) and one's complement of (Ak) to Ai                                                 |  |  |  |  |

| 046 <i>ijk</i>          | Α <i>i</i> ΑλΑ <i>k</i>            | Logical difference of (A <sub>j</sub> ) and (A <sub>k</sub> ) to A <sub>i</sub> (A <sub>j</sub> $\neq$ 0) |  |  |  |  |

| 047 <i>ijk</i>          | Α <i>i</i> #Α <i>j</i> \Α <i>k</i> | Logical equivalence of (Ak) and (Aj) to Ai                                                                |  |  |  |  |

| 047 <i>i</i> 0 <i>k</i> | Ai#Aj                              | Transmit one's complement of (Ak) to Ai                                                                   |  |  |  |  |

| 050 <i>ijk</i>          | Ai Aj!Ai&Ak                        | Logical product of (Ai) and (Ak) complement ORed with logical product of (Aj) and (Ak)                    |  |  |  |  |

| 051 <i>ijk</i>          | Ai Aj!Ak                           | Logical sum of (Aj) and (Ak) to Ai                                                                        |  |  |  |  |

### **Address and Scalar Mask**