# CRAY X-MP™ AND CRAY-1® COMPUTER SYSTEMS

I/O SUBSYSTEM

MODEL B

HARDWARE REFERENCE MANUAL

HR-0030

Copyright® 1976, 1977, 1979, 1982, 1983, 1985, 1986 by CRAY RESEARCH, INC. This manual or parts thereof may not be reproduced in any form without permission of CRAY RESEARCH, INC.

#### **RECORD OF REVISION**

PUBLICATION NUMBER HR-0030

Each time this manual is revised and reprinted, all changes issued against the previous version are incorporated into the new version and the new version is assigned an alphabetic level.

Every page changed by a reprint with revision has the revision level in the lower righthand corner. Changes to part of a page are noted by a change bar in the margin directly opposite the change. A change bar in the margin opposite the page number indicates that the entire page is new. If the manual is rewritten, the revision level changes but the manual does not contain change bars.

Requests for copies of Cray Research, Inc. publications should be directed to the Distribution Center and comments about these publications should be directed to:

CRAY RESEARCH, INC. 2520 Pilot Knob Road

Suite 310

Mendota Heights, Minnesota 55120

| Revision | Description October 1982 - Original printing; this publication and publication HR-0029, the CRAY-1 S Series Mainframe Reference Manual, obsolete publication HR-0808.                                                                                                      |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 01       | December 1983 - This change packet incorporates information pertaining to the use of the Memory (100 Mbyte) Channel with a Solid-state Storage Device and changes in how system errors are reported in machines with serial numbers of 21 and higher.                      |

| 02       | February 1985 - This change packet adds information for the DD-49 Disk Storage Unit, corrects information for instructions 047, 065, and 077, and corrects other minor technical errors.                                                                                   |

| A        | October 1985 - Reprint with revision. Information from change packets 01 and 02 has been incorporated. No other changes were made.                                                                                                                                         |

| В        | May 1986 - Reprint with revision. Disk storage unit interface information has been removed, and is now in HR-0077, Disk Systems Hardware Reference Manual. In addition, miscellaneous technical and editorial changes have been made. All previous printings are obsolete. |

## **PREFACE**

This publication describes the operation of the Cray Research, Inc. I/O Subsystem (IOS), which handles external communication and mass storage for Cray Research computer systems. This publication is written to assist programmers and engineers, and assumes the reader has a familiarity with digital computers.

The four sections of an I/O Processor are described in this publication. These four sections are the memory section, control section, computation section, and input/output section. Also described in this publication are instructions and their formats, interface requirements to peripheral devices, and Buffer Memory of an IOS.

Additionally, appendixes contain detailed reference information.

Details of Cray Research, Inc., mainframes that use the Cray IOS are given in the following manuals:

HR-0029 CRAY-1 S Series Mainframe Reference Manual

HR-0032 CRAY X-MP Dual-processor Mainframe Reference Manual

HR-0064 CRAY-1 M Series Mainframe Reference Manual

HR-0088 CRAY X-MP Single-processor Mainframe Reference Manual

HR-0097 CRAY X-MP Four-processor Mainframe Reference Manual

Details of how the IOS interfaces to DD-29, DD-39, and DD-49 Disk Storage Units are provided in CRI publication HR-0077, Disk Systems Hardware Reference Manual.

#### WARNING

This equipment generates, uses, and can radiate radio frequency energy and if not installed and used in accordance with the instructions manual, may cause interference to radio communications. It has been tested and found to comply with limits for a Class A computing device pursuant to Subpart J of Part 15 of FCC Rules, which are designed to provide reasonable protection against such interference when operated in a commercial environment. Operation of this equipment in a residential area is likely to cause interference in which case the user at his own expense will be required to take whatever measures may be required to correct the interference.

HR-0030 iv B

# **CONTENTS**

| PREF | FACE                                     | iii   |

|------|------------------------------------------|-------|

| 1.   | GENERAL INFORMATION                      | 1-1   |

|      | I/O PROCESSOR FUNCTIONS                  | 1-1   |

|      | Master I/O Processor responsibilities    | 1-3   |

|      | Buffer I/O Processor responsibilities    | 1-4   |

|      | Disk I/O Processor responsibilities      | 1-4   |

|      | Auxiliary I/O Processor responsibilities | 1-4   |

|      | I/O PROCESSOR ORGANIZATION               | 1-4   |

|      | Local Memory section                     | 1-5   |

|      | Control section                          | 1-6   |

|      | Computation section                      | 1-6   |

|      | Input/output section                     | 1-7   |

|      | REQUIRED INTERFACES                      | 1-8   |

|      | BUFFER MEMORY                            | 1-8   |

|      | I/O SUBSYSTEM CLOCK                      | 1-8   |

|      | CONVENTIONS                              | 1-8   |

|      |                                          |       |

| 2.   | LOCAL MEMORY SECTION                     | 2-1   |

|      | LOCAL MEMORY SPEEDS                      | 2-1   |

|      | LOCAL MEMORY ORGANIZATION                | 2-2   |

|      | LOCAL MEMORY ACCESS                      | 2-2   |

|      | LOCAL MEMORY ADDRESSING                  | 2-2   |

|      | LOCAL MEMORY DATA PROTECTION             | 2-3   |

| 3.   | IOP CONTROL SECTION                      | 3-1   |

|      |                                          |       |

|      | INSTRUCTION FORMATS                      | 3-1   |

|      | INSTRUCTION STACK                        | 3 – 3 |

|      | Forward relative branch                  | 3-5   |

|      | Backward relative branch                 | 3-5   |

|      | INSTRUCTION ISSUE REGISTER               | 3 – 5 |

|      | B REGISTER                               | 3-6   |

|      | REGISTER POINTER REGISTER                | 3-6   |

|      | DESTINATION POINTER REGISTER             | 3-6   |

|      | PROGRAM ADDRESS REGISTER                 | 3 – 7 |

| 3. | IOP | CONTROL | SECTION | (continued) |

|----|-----|---------|---------|-------------|

|----|-----|---------|---------|-------------|

|    | PROGRAM EXIT STACK                    | 3-7  |

|----|---------------------------------------|------|

|    | Subroutine calls                      | 3-7  |

|    | Program exit stack and I/O interrupts | 3-10 |

|    | PROGRAM FETCH REQUEST FLAG            | 3-11 |

| 4. | IOP COMPUTATION SECTION               | 4-1  |

|    | OPERAND REGISTERS                     | 4-1  |

|    | MEMORY ADDRESS REGISTER               | 4-2  |

|    | FUNCTIONAL UNITS                      | 4-2  |

|    | Adder functional unit                 | 4-2  |

|    | Shifter functional unit               | 4-3  |

|    | ACCUMULATOR                           | 4-3  |

|    | Carry Bit register                    | 4-4  |

|    | Addend register                       | 4-4  |

| 5. | INPUT/OUTPUT SECTION                  | 5-1  |

|    |                                       |      |

|    | I/O CONFIGURATION                     | 5-1  |

|    | I/O SPEEDS                            | 5-2  |

|    | CHANNEL CHARACTERISTICS               | 5-2  |

|    | Accumulator channels                  | 5-2  |

|    | Function Designators signal           | 5-3  |

|    | Function Strobe signal                | 5-3  |

|    | Accumulator Data signal               | 5-3  |

|    | Read Done signal                      | 5-3  |

|    | Read Busy signal                      | 5-3  |

|    | Busy/done signal                      | 5-3  |

|    | Master Clear signal                   | 5-4  |

|    | Clock signal                          | 5-4  |

|    | Interrupt signal                      | 5-4  |

|    | Channels using a DMA port             | 5-4  |

|    | Local Memory Data signal              | 5-4  |

|    | Local Memory Address signal           | 5-5  |

|    | Request Read signal                   | 5-5  |

|    | Request Write signal                  | 5-5  |

|    | Acknowledge Read signal               | 5-5  |

|    | Acknowledge Write signal              | 5-5  |

|    | Read sequence                         | 5-6  |

|    | Write sequence                        | 5-6  |

|    | STANDARD CHANNELS                     | 5-6  |

|    | I/O request channel                   | 5-9  |

|    | Program fetch request channel         | 5-9  |

|    | Program exit stack channel            | 5-10 |

|    | Deadstart sequence                    | 5-11 |

|    | Local Memory error channel            | 5-11 |

|    | Real-time clock channel               | 5-12 |

|    | STANDARD CHANNELS (continued)                 |            |

|----|-----------------------------------------------|------------|

|    | Buffer Memory channel                         | 5-13       |

|    | Error handling                                | 5-15       |

|    | Buffer Memory interface deadstart             | 5-15       |

|    | Buffer Memory interface dead dump             | 5-16       |

|    | I/O Processor input channels                  | 5-16       |

|    | I/O Processor output channels                 | 5-16       |

|    | INTERRUPT SEQUENCE                            | 5-19       |

|    |                                               |            |

| 6. | IOP INSTRUCTIONS                              | 6-1        |

|    | INSTRUCTION FORMAT                            | 6-1        |

|    | INSTRUCTION DESCRIPTIONS                      | 6-2        |

| 7. | INTERFACES                                    | 7-1        |

|    |                                               |            |

|    | INTERFACE CHARACTERISTICS                     | 7-1<br>7-2 |

|    | CONSOLE KEYBOARD CHANNEL                      |            |

|    | CONSOLE DISPLAY CHANNEL                       | 7-5<br>7-5 |

|    | PERIPHERAL EXPANDER CHANNEL                   | 7-5<br>7-6 |

|    | Interface registers                           | 7-0<br>7-7 |

|    | Channel assignments                           | 7-7        |

|    | EXB: 0 - Idle channel                         | 7-7        |

|    | EXB: 1 - DIA                                  | 7-8        |

|    | EXB : 2 - DIB                                 | 7-8        |

|    | EXB : 3 - DIC                                 | 7-8        |

|    | EXB: 4 - Read busy/done, interrupt number     | 7-8        |

|    | EXB: 5 - Load device address                  | 7-9        |

|    | EXB: 6 - MSKO mask out                        | 7-9        |

|    | EXB : 7 - Set interrupt mode                  | 7-10       |

|    | EXB : 10 - Read data bus status               | 7-10       |

|    | EXB : 11 - Read status 1                      | 7-11       |

|    | EXB : 13 - Read status 2                      | 7-11       |

|    | EXB : 14 - DOA (Data out A)                   | 7-11       |

|    | EXB: 15 - DOB (Data out B)                    | 7-11       |

|    | EXB : 16 - DOC (Data out C)                   | 7-11       |

|    | EXB: 17 - Send control                        | 7-13       |

|    | Delayed functions                             | 7-14       |

|    | Transfer speeds                               | 7-14       |

|    | CHANNEL FOR INPUT FROM CRAY MAINFRAME CHANNEL | 7-14       |

|    | Local Memory Address register                 | 7-15       |

|    | CIA: 0 - Clear channel                        | 7-15       |

|    | CIA: 1 - Enter Local Memory address           | 7-16       |

|    | CIA: 2 - Enter parcel count                   | 7-16       |

|    | CIA: 3 - Clear Channel Parity Error flags     | 7-16       |

|    | CIA: 4 - Clear ready waiting                  | 7-16       |

|    | CIA: 6 - Clear Interrupt Enable flag          | 7-16       |

| CHANNEL FOR INPUT FROM CRAY MAINFRAME CHANNEL (continued)                       |              |

|---------------------------------------------------------------------------------|--------------|

| CIA: 7 - Set Interrupt Enable flag                                              | 7-17         |

| CIA: 10 - Read memory address                                                   | 7-17         |

| CIA: 11 - Read ready waiting/error flags                                        | 7-17         |

| CHANNEL FOR OUTPUT TO CRAY MAINFRAME CHANNEL                                    | 7-17         |

| Local Memory Address register                                                   | 7-18         |

| COA: 0 - Clear channel                                                          | 7-18         |

| COA: 1 - Enter Local Memory address                                             | 7-19         |

| COA: 2 - Enter parcel count                                                     | 7-19         |

| COA: 3 - Clear Error flag                                                       | 7-19         |

| COA: 4 - Set/clear external control signals                                     | 7-19         |

| COA: 6 - Clear Interrupt Enable flag                                            | 7-20         |

| COA: 7 - Set Interrupt Enable flag                                              | 7-20         |

| COA: 10 - Read Local Memory address                                             | 7-20         |

| COA: 11 - Read error flags                                                      | 7-20         |

| MEMORY (100 MBYTE) CHANNEL                                                      | 7-21         |

| Signal descriptions                                                             | 7-21         |

| Cray mainframe or SSD to I/O Processor input channel                            | 7-22         |

| Data (to IOP)                                                                   | 7-22         |

| Check Byte (to IOP)                                                             | 7-22         |

| Data Ready (to IOP)                                                             | 7-23         |

| Last Word (to IOP)                                                              | 7-23         |

| Unrecoverable Error (to IOP)                                                    | 7-23         |

| Address Error (to IOP)                                                          | 7-23         |

| Transmit Address (to IOP)                                                       | 7-23         |

| Go 8 Banks (to IOP)                                                             | 7-23         |

| Transmit Data (to Central Memory or SSD)                                        | 7-24         |

| Clear Channel (to Central Memory or SSD)                                        | 7-24         |

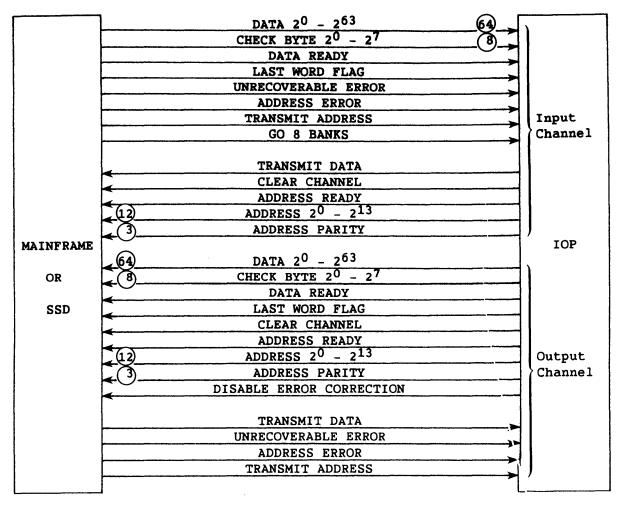

| Address Ready (to Central Memory or SSD)                                        | 7-24         |

| Address (to Central Memory or SSD)                                              | 7-25         |

| Address Parity (to Central Memory or SSD)                                       | 7-25         |

| I/O Processor Output Channel to Cray mainframe                                  | 7 20         |

| or SSD                                                                          | 7-26         |

| Data (to Central Memory or SSD)                                                 | 7-26         |

| Check Byte (to Central Memory or SSD)                                           | 7-26         |

| Data Ready (to Central Memory or SSD) Last Word Flag (to Central Memory or SSD) | 7-26         |

|                                                                                 | 7-26         |

| Clear Channel (to Central Memory or SSD)                                        | 7-27         |

| Address Ready (to Central Memory or SSD)                                        | 7-27<br>7-27 |

| Address (to Central Memory or SSD)                                              | 7-27         |

| Address Parity (to Central Memory or SSD)                                       | 1-21         |

| Disable Error Correction (to Central Memory or SSD)                             | 7 20         |

| SSD)                                                                            | 7-28<br>7-28 |

| Unrecoverable Error (to IOP)                                                    | 7-28         |

|                                                                                 | 7-29         |

| Address Error (to IOP)                                                          | 7-29         |

| TIGNOMIL AUGUESS LLO CENCIGI MEMOLV OF SOLL                                     | . – . 4      |

HR-0030 viii B

| MEMORY (100 MBYTE) CHANNEL FUNCTIONS FOR INPUT           |      |

|----------------------------------------------------------|------|

| FROM CENTRAL MEMORY OR SSD                               | 7-29 |

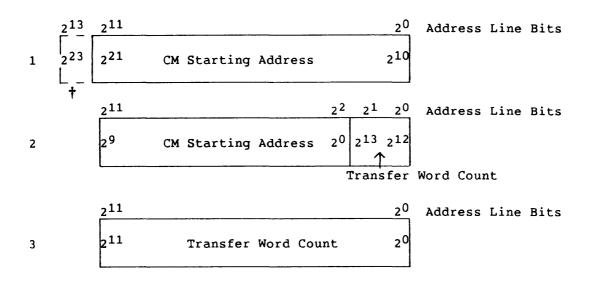

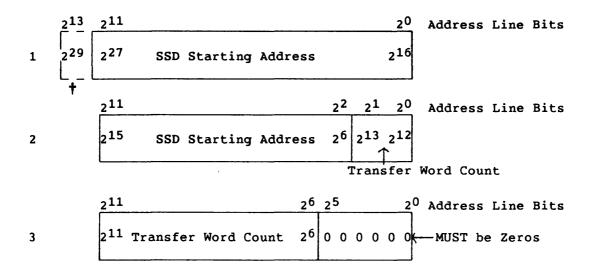

| Interface registers                                      | 7-30 |

| HIA: 0 - Clear Channel Busy and Channel Done flags       | 7-31 |

| HIA: 1 - Enter Local Memory starting address             | 7-31 |

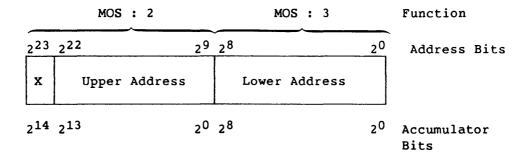

| HIA: 2 - Enter upper Central Memory or SSD address       | 7-31 |

| HIA: 3 - Enter lower Central Memory or SSD address       | 7-31 |

| HIA: 4 - Read Central Memory or SSD, enter block length  | 7-32 |

| HIA: 6 - Clear interrupt enable                          | 7-32 |

| HIA: 7 - Set interrupt enable                            | 7-32 |

| HIA: 14 - Enter diagnostic mode                          | 7-32 |

|                                                          | 7-32 |

| Memory (100 Mbyte) Channel input error processing        |      |

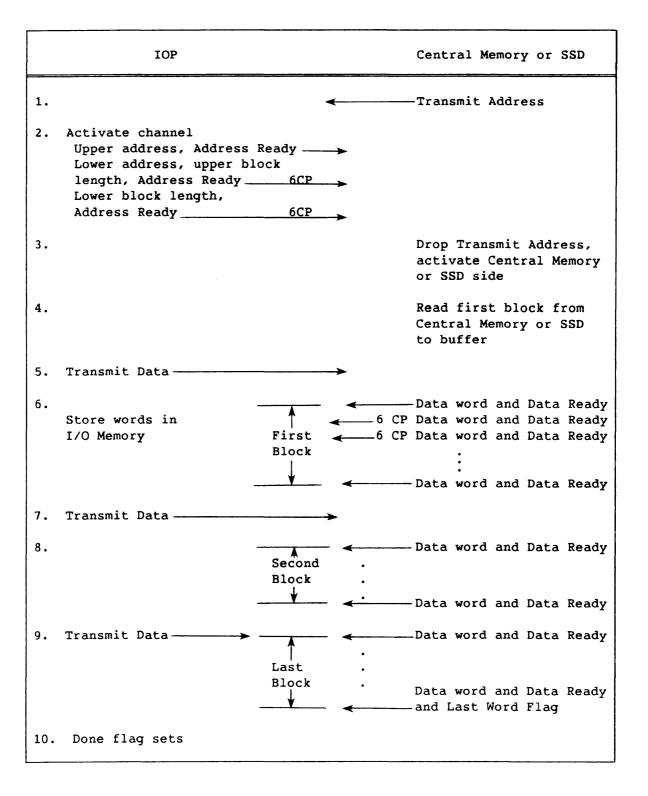

| Memory (100 Mbyte) Channel input sequence                | 7-33 |

| MEMORY (100 MBYTE) CHANNEL FUNCTIONS FOR OUTPUT TO       |      |

| CENTRAL MEMORY OR SSD                                    | 7-36 |

| Interface registers                                      | 7-36 |

| HOA: 0 - Clear Channel Busy, Done flags                  | 7-37 |

| HOA: 1 - Enter Local Memory address                      | 7-37 |

| HOA: 2 - Enter upper Central Memory or SSD address       | 7-37 |

| HOA: 3 - Enter lower Central Memory or SSD address       | 7-37 |

| HOA: 5 - Write Central Memory or SSD, enter block length | 7-38 |

| HOA: 6 - Clear interrupt enable                          | 7-38 |

| HOA: 7 - Set interrupt enable                            | 7-38 |

| HOA: 14 - Enter diagnostic mode                          | 7-38 |

| Central Memory or SSD output error processing            | 7-39 |

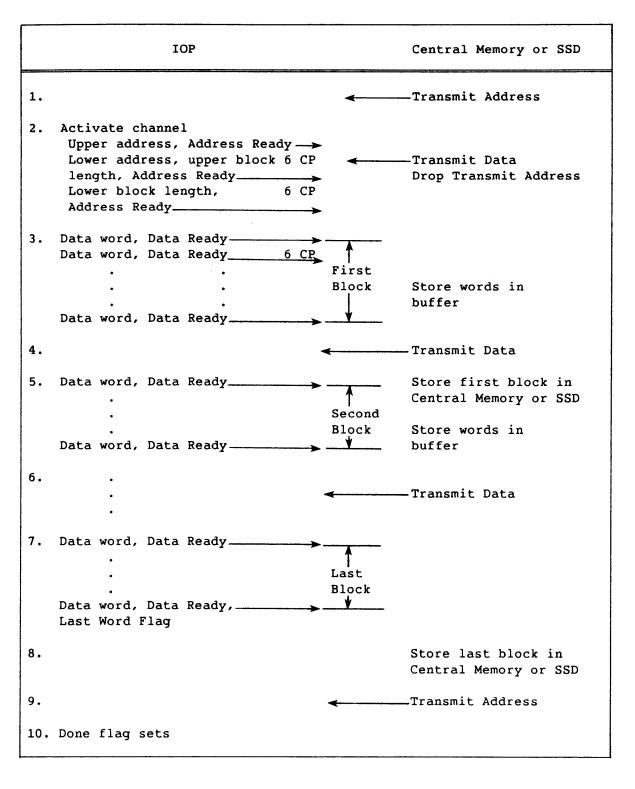

| Memory (100 Mbyte) Channel output sequence               | 7-40 |

| ERROR LOGGING CHANNEL (Serial No. 20 and below)          | 7-40 |

|                                                          |      |

| Interface registers                                      | 7-41 |

| ERA: 0 - Idle channel                                    | 7-43 |

| ERA: 6 - Clear Interrupt Enable flag                     | 7-43 |

| ERA: 7 - Set Interrupt Enable flag                       | 7-43 |

| ERA: 10 - Read error status                              | 7-43 |

| ERA: 11 - Read error information (first parameter)       | 7-44 |

| ERA: 12 - Read error information (second parameter)      | 7-46 |

| ERA: 13 - Read error information (third parameter)       | 7-46 |

| ERROR LOGGING CHANNEL (Serial No. 21 and above)          | 7-47 |

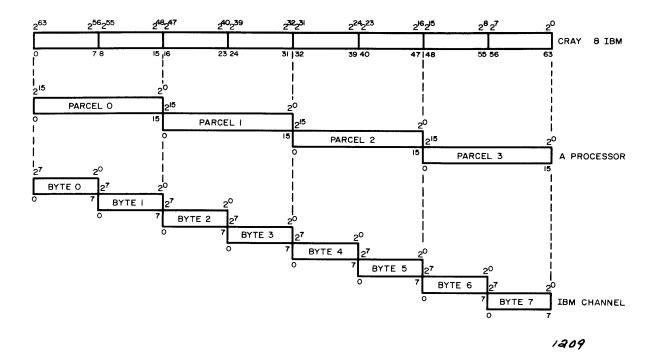

| BLOCK MULTIPLEXER CHANNEL                                | 7-48 |

| General characteristics                                  | 7-49 |

| Transfer rates                                           | 7-49 |

| Data handling                                            | 7-49 |

| Record size                                              | 7-50 |

| Parity                                                   | 7-51 |

|                                                          | 7-51 |

| Interrupts                                               |      |

| BMA: 0 - Clear Channel Busy and Done flags               | 7-51 |

| BMA: 1 - Send reset function                             | 7-51 |

| Parameter xxxxx0 - Clear output tag lines                | 7-52 |

| Parameter xxxxx1 - Interface disconnect                  | 7-52 |

| Parameter xxxxx2 - Selective reset                       | 7-52 |

| Parameter YYYYY3 _ System reset                          | 7_53 |

|      | BLOCK MULTIPLEXER CHANNEL (continued)          |      |

|------|------------------------------------------------|------|

|      | BMA: 2 - Channel command                       | 7-53 |

|      | Parameter command bits                         | 7-54 |

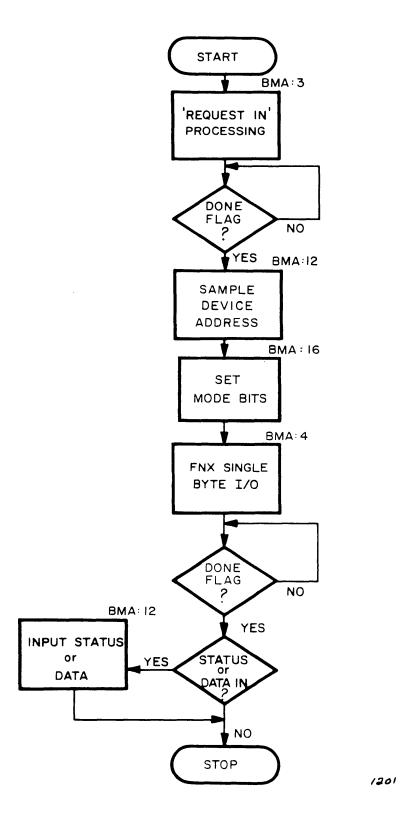

|      | BMA: 3 - Read request-in address               | 7-55 |

|      | BMA: 4 - Asynchronous I/O                      | 7-56 |

|      | BMA: 5 - Delay counter diagnostic              | 7-57 |

|      | BMA: 6 - Clear Channel Interrupt Enable flag   | 7-57 |

|      | BMA: 7 - Set Channel Interrupt Enable flag     | 7-57 |

|      | BMA: 10 - Read Local Memory address            | 7-59 |

|      | BMA: 11 - Read byte counter                    | 7-59 |

|      | BMA : 12 - Read status/address                 | 7-61 |

|      | BMA: 13 - Read input tags                      | 7-62 |

|      | BMA: 14 - Enter Local Memory address           | 7-63 |

|      | BMA: 15 - Enter byte count                     | 7-63 |

|      | BMA: 16 - Enter device address/mode            | 7-64 |

|      | Parameter mode bits                            | 7-64 |

|      | Skip flag                                      | 7-64 |

|      | Stack Status flag                              | 7-65 |

|      | Command chaining mode select                   | 7-65 |

|      | Interrupt mode select                          | 7-65 |

|      | Channel type mode select                       | 7-65 |

|      | BMA: 17 - Enter output tags                    | 7-66 |

|      | Programming examples                           | 7-67 |

|      | CHANNEL INTERFACE TO DISK STORAGE UNITS        | 7-68 |

|      | • • • • • • • • • • • • • • • • • • • •        |      |

|      |                                                |      |

| 8.   | BUFFER MEMORY                                  | 8-1  |

|      |                                                |      |

|      | MEMORY ORGANIZATION                            | 8-1  |

|      | MEMORY ACCESS                                  | 8-2  |

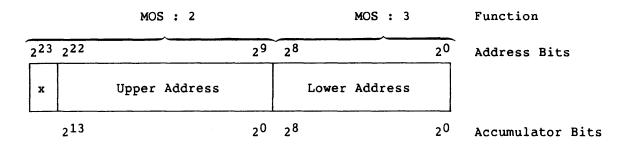

|      | MEMORY ADDRESSING                              | 8-3  |

|      | ERROR PROTECTION                               | 8-3  |

|      |                                                |      |

|      |                                                |      |

| APPE | ENDIX SECTION                                  |      |

|      | ,                                              |      |

|      |                                                |      |

| Α.   | I/O PROCESSOR INSTRUCTION SUMMARY              | A-1  |

|      |                                                |      |

|      |                                                |      |

| В.   | I/O PROCESSOR PROGRAMMING CONSIDERATIONS       | B-1  |

|      |                                                |      |

|      | EXIT STACK TIMING                              | B-1  |

|      | EXIT STACK INTERRUPT HANDLING                  | B-1  |

|      | SYSTEM INTERRUPT ENABLE                        | B-1  |

|      | SYSTEM INTERRUPT DISABLE                       | B-2  |

|      | SYSTEM INTERRUPT CLEARED OR SET BY ENABLES FOR |      |

|      |                                                | B-2  |

|      |                                                | B-2  |

|      |                                                | B-2  |

|      | BUFFER MEMORY DEADSTART TIME                   |      |

|      |                                                |      |

| В.      | B. I/O PROCESSOR PROGRAMMING CONSIDERATIONS |    | (continued) |     |     |     |    |    |    |    |    |   |   |      |

|---------|---------------------------------------------|----|-------------|-----|-----|-----|----|----|----|----|----|---|---|------|

|         | ERROR LOGGING AND BLOCK MULTIPLEXER CHANN   | N  | EL          | ıs  | ( : | SEI | RI | λL | NO | o. | 20 | ) |   |      |

|         | AND BELOW)                                  |    |             |     |     |     |    | •  |    |    |    | • |   | B-3  |

|         | I/O INSTRUCTIONS AFTER DEADSTART            |    |             |     |     |     |    |    |    |    |    |   |   | B-3  |

|         | PERIPHERAL EXPANDER CHANNEL TRANSFERS .     |    | •           | •   | •   | •   | •  | •  | •  | •  | •  | • | • | B-3  |

|         |                                             |    |             |     |     |     |    |    |    |    |    |   |   |      |

| c.      | SYSTEM CHANNEL ASSIGNMENTS                  |    |             |     |     |     |    |    |    |    |    |   |   | C-1  |

|         |                                             |    |             |     |     |     |    |    |    |    |    |   |   |      |

| D.      | ABBREVIATIONS                               |    |             |     |     | •   |    |    |    |    |    |   |   | D-1  |

|         |                                             |    |             |     |     |     |    |    |    |    |    |   |   |      |

| FIGU    | RES                                         |    |             |     |     |     |    |    |    |    |    |   |   |      |

|         |                                             |    |             |     |     |     |    |    |    |    |    |   |   |      |

| 1-1     | I/O Subsystem Chassis                       |    |             |     |     |     |    |    |    |    |    |   |   | 1-2  |

| 1-2     | Four Processor IOS Configuration            |    |             |     |     |     |    |    |    |    |    |   |   | 1-3  |

| 1-3     | Basic Organization of an I/O Processor .    |    | •           | •   | •   | •   | •  | •  | •  | •  | •  | • | • | 1-5  |

| 2-1     | Local Memory Address Format                 |    | •           | •   | •   | •   | •  | •  | •  | •  | •  | • | • | 2-3  |

| 3-1     | I/O Processor Block Diagram                 |    | •           | •   | •   | •   | •  | •  | •  | •  | •  | • | • | 3-2  |

| 3-2     | Instruction Formats                         |    | •           | •   | •   | •   | •  | •  | •  | •  | •  | • | • | 3-3  |

| 3-3     | Instruction Stack Operation                 |    | •           | •   | •   | •   | •  | •  | •  | •  | •  | • | • | 3-4  |

| 3-4     | Program Exit Stack                          |    | •           | •   | •   | •   | •  | •  | •  | •  | •  | • | • | 3-8  |

| 5-1     | Buffer Memory Address Formation             |    | •           | •   | •   | •   | •  | •  | •  | •  | •  | • | • | 5-14 |

| 6-1     | Instruction Formats                         |    |             |     |     |     |    |    |    |    |    |   |   | 6-1  |

| 7-1     | Memory (100 Mbyte) Channel Signals          |    |             |     |     |     |    |    |    |    |    |   |   | 7-22 |

| 7-2     | Address and Word Count Formats for Centra   |    |             |     |     |     |    |    |    |    |    |   |   | 7-25 |

| 7-3     | Address and Word Count Formats for SSD .    |    |             |     |     |     |    | •  | •  | •  | •  | • | • | 7-26 |

| 7 – 4   | Memory (100 Mbyte) Channel Sequence on Ir   |    |             |     |     |     |    |    |    |    |    |   |   |      |

|         | I/O Processor                               |    |             |     |     |     |    |    | •  | •  | ٠  | • | • | 7-35 |

| 7-5     | Memory (100 Mbyte) Channel Sequence on Ou   |    | _           |     |     |     |    |    |    |    |    |   |   |      |

|         | I/O Processor                               |    |             |     |     |     |    |    |    |    |    |   |   | 7-42 |

| 7-6     | BMC-4 Data Assembly/Disassembly             |    |             |     |     |     |    |    |    |    |    |   |   | 7-50 |

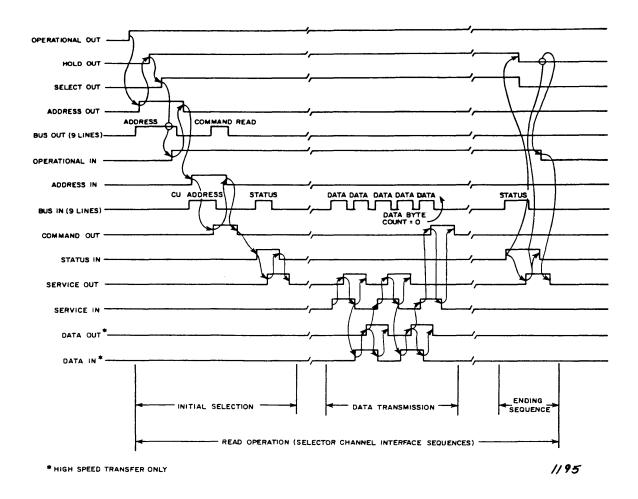

| 7-7     | Channel Read Sequence                       |    |             |     |     |     |    |    |    |    |    |   |   | 7-55 |

| 7-8     | Channel I/O Sequence                        |    |             |     |     |     |    |    |    |    |    |   |   | 7-56 |

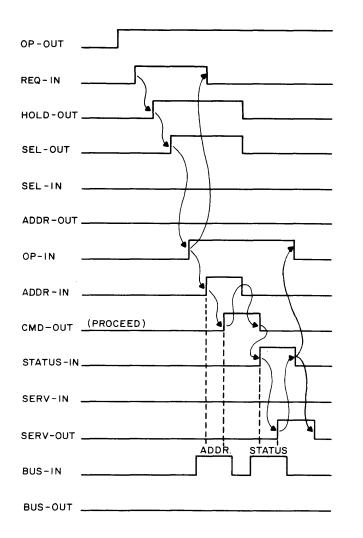

| 7-9     | Asynchronous Data and Status Processing     |    |             |     |     |     |    |    |    |    |    |   |   | 7-58 |

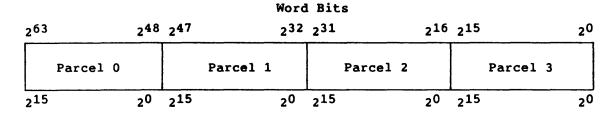

| 8-1     | Parcel Packing in Buffer Memory Word        |    |             |     |     |     |    | •  | •  | •  | •  | • | • | 8-2  |

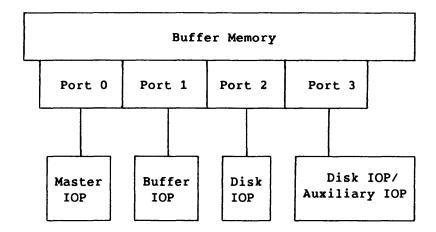

| 8-2     | Buffer Memory Port Assignments              |    |             |     |     | •   | •  | •  | •  | •  | •  | • | • | 8-2  |

| 8-3     | Buffer Memory Address Formation             | ,  | •           | •   | •   | •   | •  | •  | •  | •  | •  | • | • | 8-3  |

| <b></b> |                                             |    |             |     |     |     |    |    |    |    |    |   |   |      |

| TABLI   | <u>ES</u>                                   |    |             |     |     |     |    |    |    |    |    |   |   |      |

| 5-1     | IOP Standard Channel Assignments (in rela   | a۱ | tί          | or. | ı t | .0  | th | ıe | ΜI | OF | )  |   |   | 5-7  |

| 5-2     | Standard Channel Functions                  |    |             |     |     |     |    |    |    |    |    |   |   | 5-7  |

| 7-1     | Interface Functions                         | ,  | •           |     |     |     |    |    |    |    |    |   |   | 7-2  |

| 7 – 2   | Peripheral Device Mask Bits for Interrupt   | t  | D           | is  | ab  | li  | nc | ſ  |    |    |    |   |   | 7-10 |

| 7-3     | Read Status 1 Bit Assignments               |    |             |     |     |     | _  |    |    |    |    |   |   | 7-12 |

| 7-4     | Read Status 2 Bit Assignments               |    | •           |     |     |     |    |    |    |    |    |   |   | 7-13 |

HR-0030

## TABLES (continued)

| 7-5  | Accumulator Bit Control Signals .   | •   | •    | • | •  | •  | •  | • | • | • | • | • | • | • | • | 7-14   |

|------|-------------------------------------|-----|------|---|----|----|----|---|---|---|---|---|---|---|---|--------|

| 7-6  | Ready Waiting/Error Flags           | •   | •    |   |    |    |    |   |   |   |   |   | • |   |   | 7-17 / |

| 7-7  | External Control Signal Bits        |     | •    | • |    |    | •  | • |   |   | • | • | • |   | • | 7-20   |

| 7-8  | Error Flags                         |     |      | • |    |    | •  | • |   | • | • | • | • |   |   | 7-21   |

| 7-9  | Input Channel Diagnostic Modes      |     |      | • |    | •  | •  | • |   |   | • |   | • | • |   | 7-33   |

| 7-10 | Input Channel Error Codes           |     |      | • |    | •  | •  | • |   |   | • |   | • |   | • | 7-34   |

| 7-11 | Output Channel Diagnostic Modes .   | •   |      | • | •  |    | •  | • |   |   | • | • | • |   |   | 7-39   |

| 7-12 | Output Channel Error Codes          | •   |      | • |    |    | •  | • |   |   | • |   | • |   | • | 7-40   |

|      | Error Status Register Bits          |     |      |   |    |    |    |   |   |   |   |   |   |   |   | 7-44   |

| 7-14 | First Error Parameter Selection .   | •   | •    | • | •  | •  |    | • | • | • | • | • | • | • |   | 7-45   |

| 7-15 | Send Reset Function Parameters      | •   |      | • | •  | •  |    | • | • |   | • | • | • |   | • | 7-51   |

| 7-16 | Channel Command Function Parameter  | В   | its  | 5 | •  | •  |    | • | • |   | • | • | • | • | • | 7-53   |

| 7-17 | Channel Command Bit Assignments .   |     | •    | • |    | •  |    |   | • | • |   | • |   | • | • | 7-54   |

|      | Read Local Memory Address Response  |     |      |   |    |    |    |   |   |   |   |   |   |   |   | 7-60   |

|      | Status Register Bits                |     |      |   |    |    |    |   |   |   |   |   |   |   |   | 7-61   |

| 7-20 | Input Tags Status Bits              |     | •    | • |    | •  |    |   | • |   |   | • |   |   | • | 7-62   |

|      | Local Memory Address Register Bits  |     |      |   |    |    |    |   |   |   |   |   |   |   |   | 7-63   |

| 7-22 | Device Address Register Bits        |     | •    | • |    | •  | •  |   | • | • | • | • |   |   | • | 7-64   |

|      | Command Chaining Mode Selection .   |     |      |   |    |    |    |   |   |   |   |   |   |   |   | 7-65   |

| 7-24 | Interrupt Mode Selection            |     |      | • | •  | •  | •  | • |   | • | • |   | • |   | • | 7-65   |

| 7-25 | Channel Type Mode Selection         |     | •    |   |    |    |    |   | • |   |   |   | • |   |   | 7-66   |

| 7-26 | Output Tags Register Bits           |     | •    |   | •  | •  |    | • |   | • |   |   | • |   | • | 7-66   |

| C_1  | Typical Model S/4400 System Channel | ١ : | ٠. د |   | mm | an | +0 |   |   |   |   |   |   |   |   | C 1    |

### INDEX

The Cray Research, Inc. Input/Output Subsystem (IOS) provides high-capacity data communications between Central Memory of a Cray mainframe and peripheral devices, storage devices, and front-end computers. The IOS is a required component of the CRAY-1 S series computer systems, models S/1200 through S/4400; all models of the CRAY X-MP series of computer systems; and all models of the CRAY-1 M series of computer systems. System overviews are provided in the relevant mainframe reference manuals.

The IOS is housed in a chassis (see figure 1-1) similar to a Cray Research, Inc. mainframe chassis and is composed of two to four I/O Processors, a group of interfaces, and Buffer Memory.

An I/O Processor (IOP) is a fast, multipurpose computer capable of transferring data at extremely high rates. A 16-bit processor and a fast bipolar Local Memory combine to support high-speed I/O operations by an IOP. (Local Memory, contained in each IOP, is distinguished from Buffer Memory, which is common to all IOPs.) The input and output capabilities make the IOP useful for network control, mass storage access, and computer interfacing.

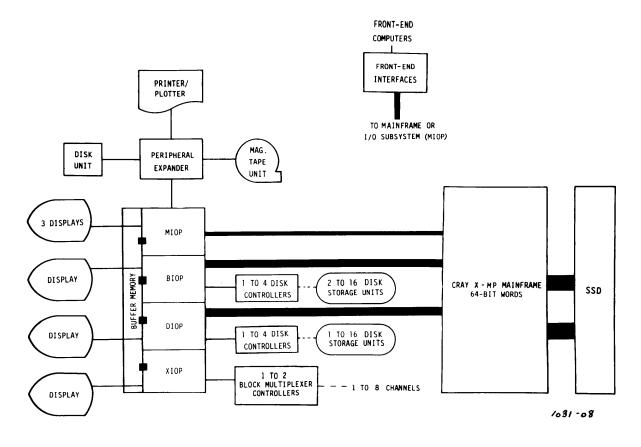

An I/O Subsystem has a minimum of two IOPs. The Master I/O Processor (MIOP) and a Buffer I/O Processor (BIOP) are mandatory. In addition, the IOS can have one or two Disk I/O Processors (DIOPs), permitting a maximum of 48 disk units to be connected to the system. An Auxiliary I/O Processor (XIOP) controls block multiplexer channels and can be selected as an alternative to a DIOP.

An example of a four-processor IOS configuration is shown in figure 1-2. Configurations are factory hard-wired. Available configurations are described in the relevant mainframe reference manuals.

#### I/O PROCESSOR FUNCTIONS

In the I/O Subsystem, each IOP runs independently and is responsible for its own set of functions. IOP functions are defined by the way the IOP is attached to the other IOPs (and the mainframe) and by the peripheral equipment attached to it.

Software in each IOP performs specific functions and is structured to perform its tasks as efficiently as possible. Each IOP logs information and keeps statistics about channel use and error detection and recovery. The IOPs share Buffer Memory for communicating with each other. By using this communication mechanism, the processors can perform functions for each other.

Figure 1-1. I/O Subsystem Chassis

- 6 Mbyte channel

- 100 Mbyte channel

- 1250 Mbyte channel

Figure 1-2. Four Processor IOS Configuration

#### MASTER I/O PROCESSOR RESPONSIBILITIES

The MIOP handles all communication with the Cray mainframe, including disk and tape requests and station communications. The MIOP supports front-end and station software, and handles input and output operations on the Peripheral Expander channel.

The MIOP is the first IOP to be deadstarted. The MIOP initializes the contents of Buffer Memory and deadstarts the other processors in the configuration. The MIOP, with the BIOP and the disk handling capabilities of the DIOP, deadstarts the Cray mainframe.

#### BUFFER I/O PROCESSOR RESPONSIBILITIES

The BIOP transfers data between Central Memory and Buffer Memory across a Memory (100 Mbyte) Channel. The BIOP also performs disk I/O to and from disk units attached to the BIOP's channels. I/O is driven by messages from the mainframe. (IOS software supports DD-29, DD-39 and DD-49 Disk Storage Units.) The BIOP performs error recovery when errors are detected on data transfers.

#### DISK I/O PROCESSOR RESPONSIBILITIES

The DIOP performs disk I/O to and from disk units attached to the DIOP's channels. I/O is driven by messages from the mainframe. The DIOP performs error recovery when errors are detected on data transfers. If equipped with a Memory (100 Mbyte) Channel, a DIOP transfers data between Central Memory and Buffer Memory.

#### AUXILIARY I/O PROCESSOR RESPONSIBILITIES

The XIOP's main function is to handle data from IBM-compatible tape drives and buffer the data to Buffer Memory. The XIOP can also be used to drive other peripherals. I/O is driven by messages from the mainframe. The XIOP performs error recovery procedures when errors are detected while transferring data to or from tape.

#### I/O PROCESSOR ORGANIZATION

Each IOP has a memory section, a control section, a computation section, and an input/output section (figure 1-3). A brief description of each section follows.

HR-0030 1-4 B

#### LOCAL MEMORY SECTION

IOP memory is called Local Memory. It consists of four sections of 4 banks each of random access, solid-state memory. All memory sections function independently of each other.

# MEMORY SECTION • 65,536 parcels of 16-bits each • Bipolar random access memory CONTROL SECTION • Instruction stack Program exit stack COMPUTATION SECTION • 512 16-bit operand registers • Functional units • Accumulator INPUT/OUTPUT SECTION • 6 direct memory access (DMA) ports • 16-bit port width • Approximately 2.56 gigabits/s peak rate Other I/O Functionally Buffer Dependent **Processors** Memory Interfaces

Figure 1-3. Basic Organization of an I/O Processor

Memory cycle time is 4 clock periods (CPs), which means a section is usable again 4 CPs after the preceding memory reference. An exception is the I/O write operation which requires 6 CPs. Access time (the time required to bring an operand from memory to the accumulator) is 7 CPs. Memory capacity is fixed at 65,536 units (called parcels) of 16 bits each plus 2 odd parity bits for each parcel.

See section 2 for additional information on Local Memory.

#### CONTROL SECTION

An IOP control section has an instruction stack, program exit stack, and control logic. An IOP has a 12.5 ns clock period and executes 128 instruction codes as 16-bit (1-parcel) or 32-bit (2-parcel) instructions. Branching and I/O instructions are included in the set. Instructions are stored in memory, and transferred into the instruction stack under the control of a program address counter. Instructions issue from the instruction stack and are decoded into the control signals enabling the functions of the instruction.

The instruction stack is a 32-parcel circular buffer that provides fast access to a moving window of program instructions. The longest held parcels are overwritten by newly transferred instructions. The program is free to branch quickly about inside the stack, only slowing when more instructions must be read from memory.

The program exit stack is a last-in-first-out set of 16 registers that stores return addresses for program subroutine calls. The 16 registers provide for 14 nested levels of subroutines in the program. A pointer keeps track of the levels involved. An interrupt is generated when the stack is emptied or filled. Since the stack may be loaded or unloaded by the program, an unlimited number of subroutines can be nested by means of the software.

See section 3 for additional information on IOP control.

#### COMPUTATION SECTION

The IOP computation section contains operand registers, functional units, and an accumulator operating together to execute a program of instructions stored in memory.

All arithmetic (addition and subtraction) is in twos complement mode in one Adder functional unit. Floating-point arithmetic is not incorporated. A Shifter functional unit provides left or right shifts of up to 31 bit positions, either circular or end-off shifting. A logical product operation is provided.

Any of 512 operand registers are used for temporary data storage or for indirect memory addressing. All operand registers are 16 bits wide.

The accumulator is a 16-bit signed register that temporarily stores operands or results. All data movement within the single-address IOP uses the accumulator either as a source of data or as the destination for results. An instruction code specifies the memory address or register from which the accumulator accesses data or to which the accumulator sends data.

The accumulator is also used for all transfers between memory and operand registers. Accumulator data can be sent to or received from specialized I/O channels. An accumulator bit occupies the  $2^{16}$  bit position as the carry flag. When operations in the Adder yield a carry, the accumulator  $2^{16}$  bit is toggled. The accumulator bit is included in all shift operations. The carry flag is available for conditional testing and can be set to reflect I/O channel status.

See section 4 for additional information on the computation section of an I/O Processor.

#### INPUT/OUTPUT SECTION

Communication with an IOP is through six direct memory access (DMA) ports. Each port is bidirectional and can transfer four 16-bit parcels every 6 CPs. An I/O Processor has a maximum of 40 channels. Input and output channels can be active at the same time, as long as they use different ports and reference different memory sections. The ports are assigned to channels with the possibility of several channels sharing one port. The slower the required data rate on the channels, the more channels can be multiplexed into one DMA port.

Channels use Busy and Done flags to signal the IOP and communicate directly with the IOP accumulator for control information. Use of the flags and the accumulator varies with the specific design of the channel interface logic. All channels communicate status and functions through the accumulator. Some low-speed devices can transfer data directly to and from the accumulator using one of the channel registers.

Section 5 describes the input/output section of an I/O Processor.

В

#### REQUIRED INTERFACES

Interfaces adapt an IOP to peripheral devices. Section 7 describes the required interfaces for a Cray I/O Subsystem.

#### BUFFER MEMORY

Buffer Memory assists data transfer between peripheral devices and Central Memory in a Cray mainframe. Buffer Memory is housed in the IOS chassis and stores 1 million, 4 million, or 8 million 64-bit words. All I/O Processors share Buffer Memory, which uses single-error correction/double-error detection (SECDED) data protection.

Section 8 provides additional information on Buffer Memory.

#### I/O SUBSYSTEM CLOCK

The clock controlling the I/O Subsystem is a crystal-controlled oscillator that runs at 80 MHz and gives a clock period (CP) of 12.5 ns. The speed can be adjusted slightly higher or lower for maintenance purposes. When operations require exact timing information, such as interval timing with the real-time clock, maintenance personnel should be contacted to verify the clock period.

#### CONVENTIONS

In this manual, parentheses are used in instructions as a form of shorthand notation for the expression "the contents of operand register ---" or "the contents of memory location ---." For example, A = A - (B) means "Subtract the contents of the operand register addressed by the B register from the previous accumulator content." Special symbols used in instruction descriptions are given in section 6.

Register bit positions are numbered from right to left as powers of 2, starting with bit  $2^{0}$ .

Channel numbers are specified in octal. All other numbers, unless otherwise indicated, are decimal numbers. Octal numbers other than channel numbers are indicated with a subscript 8 (for example, 128).

В

I/O Processor (IOP) memory, called Local Memory, consists of 16 banks of random access, solid-state storage. The 16 banks of 4096 parcels each are divided into four sections of 4 banks each. Each 4-bank section is independent of the other sections. Local Memory has the following characteristics:

- 65,536 parcels of 16 bits

- 16 banks of 4,096 parcels each

- 4 clock-period (CP) bank cycle time on an I/O read operation or accumulator reference

- 6 CP bank cycle time on an I/O write operation

- Access time every 6 CPs

- Read operation to accumulator in 7 CPs

- One instruction fetched per CP

- 1 data parcel per CP on sequential addressing for fetch or I/O

- Dual odd parity protection

- Six full-duplex, direct memory access (DMA) ports

Local Memory speeds, organization, access, addressing, and data protection are described in this section.

#### LOCAL MEMORY SPEEDS

For an accumulator read or write reference, Local Memory has a cycle time of 4 CPs. For an I/O reference, Local Memory cycle time is 4 CPs on a read operation and 6 CPs on a write operation. Access time, the time required to fetch an operand from Local Memory to the accumulator, is 7 CPs. Instructions are fetched from Local Memory at the rate of 1 parcel per CP in 4-parcel bursts. I/O operations transfer data in bursts of 4 parcels, 1 parcel each CP. Local Memory organization (explained later in this section) allows sequential addresses to be referenced every CP, whether the operation is a read or a write. However, the same section can only be referenced once every 6 CPs by the same DMA port. Data transferred in the operation can be 1 parcel of operand data or 4 parcels of I/O data. The Peripheral Expander is an exception; it transfers 1 parcel of I/O data per reference.

#### LOCAL MEMORY ORGANIZATION

Each 4-bank section of Local Memory has separate access paths, sequence controls, write data registers, and read data registers. The 4 banks within a section share a common sequence control. Reference to any one bank of the section also references the other three banks in the section, but only the addressed bank transfers data.

A read reference to a section in Local Memory causes all 4 banks in that section to read out parcels to their read registers. The addressed parcel or parcels are then gated to their destination. In an operand reference, a single parcel goes to the accumulator. In an I/O reference, each of the 4 parcels is gated in sequence to the output channel. The read reference and transmission sequence are fixed with reference to timing of the initiation and moving of data. Once the reference has been started, it continues automatically. After 4 CPs, the section is free to begin another reference.

A write sequence from an IOP's input/output section can be assembling data for a section of Local Memory in the bank write data registers at the same time an I/O read reference is reading data from that same section of Local Memory. If an I/O write follows any other write to the same section, a write register conflict occurs. The first write must complete before data can be sent for the subsequent write. This causes the second I/O write to take 6 CP, but only for this conflict case. The actual data moved per reference can vary from 1 operand parcel to a 4-parcel burst for an I/O operation.

#### LOCAL MEMORY ACCESS

Each Local Memory section has three 16-bit data paths for reading and two 16-bit data paths for writing. One read path and one write path go to the accumulator, which is a 16-bit signed register for temporary storage of operands and results. One read path and one write path go to the IOP's input/output section as direct memory access (DMA) ports. The last read path goes to the instruction stack and carries instruction parcels. The DMA ports are explained in greater detail in section 5, IOP input/output; the instruction stack is described in section 3, IOP control.

#### LOCAL MEMORY ADDRESSING

A parcel in Local Memory is addressed in 16 bits as shown in figure 2-1. The low-order 4 bits specify the section and bank of the section to be addressed. The high-order 12 bits select the storage chip and specify an address within the storage chip.

| 215 |                                  | 24 | 23           | 22         | 21          | 20      |

|-----|----------------------------------|----|--------------|------------|-------------|---------|

|     | Chip Address<br>and Chip Selects |    | Sect<br>Sele | ion<br>ect | Ban<br>Sele | k<br>ct |

Figure 2-1. Local Memory Address Format

Three address paths go from each of the four Local Memory sections: one from the I/O section, one from the computation section, and one from the control section for instruction fetch references.

#### LOCAL MEMORY DATA PROTECTION

Data stored in Local Memory is protected by using a mechanism called voting memory. Each IOP has three separate copies of memory, and all three copies are referenced on each read and write. On reads, the copies are compared on a bit-by-bit basis. If the 3 bits do not agree, majority determines the value of the bit.

Each data word also has a parity bit. If a parity error exists after the majority vote operation, an error handling routine uses the Local Memory error channel to determine the location of the failing hardware and to issue this information for maintenance people. Normally, no further IOP operation is attempted until the Local Memory fault is corrected. The Local Memory error channel is described in section 5 of this publication.

|     |  | y v |

|-----|--|-----|

| • • |  |     |

The control section of an I/O Processor (IOP) consists of an instruction stack and a program exit stack. The control section has the following characteristics:

- 12.5 ns clock period (CP)

- Single addressing mode

- 128 operation codes

- Instruction stack

- Program exit stack, 16 primary levels

Instructions move data from a source to the accumulator and from the accumulator to a destination. Operand registers temporarily store operands and results. Functional units in the computation section of an IOP receive operand pairs and produce single results. One operand address is designated by the instruction, and the other operand is contained in the accumulator. Typically, data flows from Local Memory to the accumulator, from the accumulator (with an operand) to a functional unit, back to the accumulator, and from the accumulator to Local Memory.

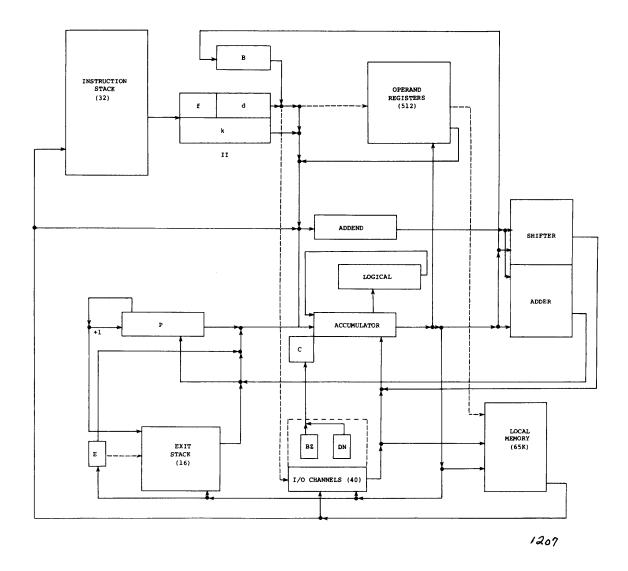

Figure 3-1 is a block diagram of an IOP. Important features of the control section for the IOP are the instruction stack, II register, B register, P register, and exit stack. These features are described later in this section.

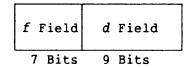

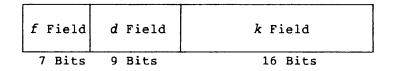

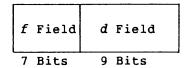

#### INSTRUCTION FORMATS

Instructions are 1 parcel (16 bits) or 2 parcels (32 bits) in size. A 1-parcel instruction consists of a function code (f) field and a designator (d) field. A 2-parcel instruction consists of the f and d fields and a constant (k) field. Figure 3-2 illustrates the formats of 1-parcel and 2-parcel instructions.

- - - Selection path

\_\_\_\_ Data path

Figure 3-1. I/O Processor Block Diagram

HR-0030 3-2 B

1-parcel instruction:

2-parcel instruction:

Figure 3-2. Instruction Formats

The 7-bit f field contains the instruction function code specifying the instruction to be executed and designating where and how the execution occurs. The 9-bit d field can contain data, address, or shift count and designates what machine resources the function of the f field is to use. The 16-bit k field is a constant field occupying the program parcel immediately following the d and f field parcel. A detailed explanation of the instruction formats is given in section 6.

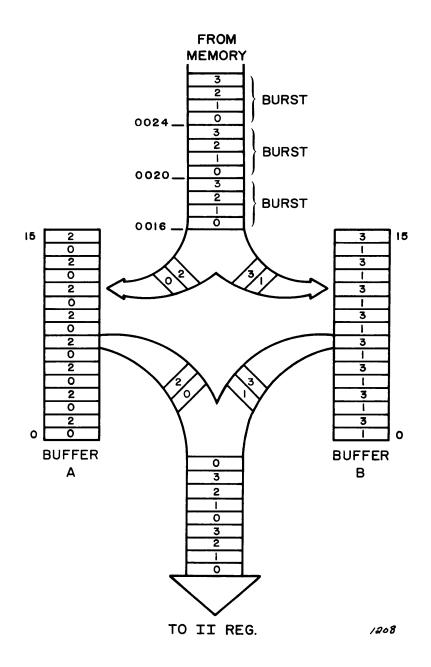

#### INSTRUCTION STACK

Program instructions are fetched from Local Memory and stored in a 32-position, 16-bit instruction stack. The stack capacity for 32 instruction parcels allows short program loops to execute in the stack without reference to Local Memory. The instruction stack is 2 banks of registers with 16 parcels of program code in each bank (figure 3-3). Addresses alternate between the two banks so that loading of data from storage can interleave with the readout of instructions for execution. Instructions are fetched from Local Memory in bursts of 4 parcels; each burst references a storage address that is a multiple of 4. Loading is sequential once issue control selects which of the 4 parcels fetched is received first. If no memory conflicts exist, 1 parcel each clock period issues from Local Memory.

An instruction passes directly into execution if the instruction sequence can issue in that CP. The instruction is stored in the instruction stack whether it issues immediately or waits for issue. When an issue delay occurs, arriving parcels are also stored in the instruction stack.

Figure 3-3. Instruction Stack Operation

The instruction stack is implemented as a circular buffer. When the stack is full and new program code is required, the new code is stored in the beginning address of the stack. Circular loading continues with the issue control circuits keeping a record of the current section of Local Memory represented in the instruction stack. To maintain a situation in which the next instructions to be executed are in the stack, internal (background) fetches are performed as instructions sequentially execute.

Out-of-stack branch conditions also cause a fetch, beginning at stack location 0. Once this fetch is accomplished, barring other branches, the internal fetch mechanism takes over. All absolute branches (instructions 074 through 077 and 120 through 137) are considered to be out of stack. Relative jumps (instructions 070 through 073 and 100 through 117) can be in-stack or out-of-stack, depending on the offset, the d field, and the locations of the stack and load pointers.

#### FORWARD RELATIVE BRANCH

Forward relative branches in the instruction stack that are less than or equal to an offset of  $11_8$  do not generate an out-of-stack condition. Forward branches with an offset greater than  $11_8$  may exceed the point that predetermined internal fetches have reached or will reach.

#### BACKWARD RELATIVE BRANCH

Backward relative branches in the instruction stack that are less than or equal to an offset of  $13_8$  do not generate an out-of-stack condition. Backward branches with an offset greater than  $13_8$  may exceed the point that predetermined internal fetches have reached or will reach. If the stack is being filled for the first time after an out-of-stack condition, a backward relative branch is only valid to location 0 of the stack.

#### INSTRUCTION ISSUE REGISTER

The Instruction Issue (II) register is a 16-bit register that receives the instruction parcel from the instruction stack. The instruction parcel can stay in the II register for more than 1 CP and leaves the II register when a new instruction is needed.

The operation code (f field) of the instruction parcel (bits  $2^9$  through  $2^{15}$ ) is translated by logic associated with the II register to determine the particular sequence of operations required. The d field of the instruction parcel (bits  $2^0$  through  $2^8$ ) is sent to the Register Pointer (RP) register, Destination Pointer (DP) register, Addend register, or accumulator. The d field also addresses an I/O channel and selects operand registers. If the f field translation shows the parcel to be the first of a 2-parcel instruction, the second parcel is sent from the instruction stack to the Addend register or accumulator and is not interpreted as an instruction.

#### B REGISTER

The B register is a 9-bit address register used to designate one of the 512 operand registers. The B register is loaded from the accumulator, taking the low-order ( $2^0$  through  $2^8$ ) bits. Accumulator bit  $2^0$  goes into B register  $2^0$  location. The B register may also address the I/O channel for an I/O instruction or may be used as an operand. For I/O instructions, the B register contains the alternate low-order bits (bits  $2^0$  through  $2^8$ ) of the instruction d field. When used in this manner, the B register can be altered by the program, in contrast to the d field which is part of the program.

#### REGISTER POINTER REGISTER

The 9-bit Register Pointer (RP) register directly addresses one of the 512 operand registers for reading or writing. The RP register receives the d field from the II register or bits  $2^0$  through  $2^8$  of the B register on issue of each instruction using operand registers. The RP register is not shown in figure 3-1.

The operand registers are built to automatically read out data as addressed by the RP register, unless an instruction specifically demands a write into an operand register. The automatic read occurs each clock period and is ignored if the read data is not needed.

#### DESTINATION POINTER REGISTER

The 9-bit Destination Pointer (DP) register selects one of the 512 operand registers to receive the contents of the accumulator. It is accessed by an instruction type using the same operand register for both operand and result. The DP register receives the pointer from the d field or bits  $2^0$  through  $2^8$  of the B register when the instruction issues. A write operation from the accumulator to an operand register usually involves a delay between the time the instruction issues and the time the register pointer is required. The DP register stores the pointer during the delay period. The DP register is not shown in figure 3-1.

Because the transfer of a pointer from the DP register to the RP register uses the same path into the RP register as the pointer coming from the II register, instruction issue can be blocked until the path into the RP register is free.

#### PROGRAM ADDRESS REGISTER

The 16-bit Program Address (P) register holds the memory address of the instruction currently awaiting issue. The P register contents are automatically incremented as each instruction is executed in program sequence. A delay between reading from the instruction stack and instruction issue keeps the address in the P register two program steps behind the instruction stack readout address. This delay is transparent to the programmer.

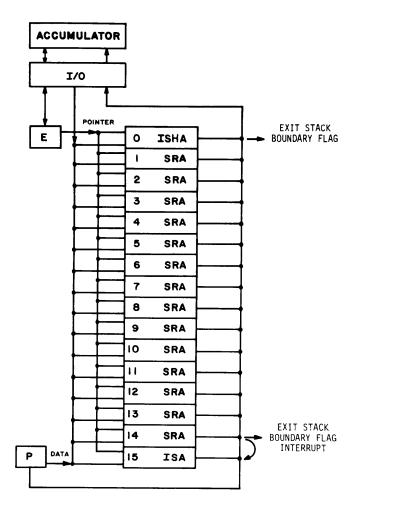

Branch instructions alter the P register contents by either adding a positive or negative displacement value or by entering a new value.

#### PROGRAM EXIT STACK

The program exit stack stores the following:

- A program return address when a subroutine is called

- A program return address when the program is suspended to handle interrupts

- The interrupt handler starting address

The program exit stack (figure 3-4) consists of sixteen 16-bit registers and is addressed by the E register, a 4-bit pointer. A program can access and modify the contents of the program exit stack and the E register through I/O channel functions.

Position 0 in the stack is reserved for the starting address of the interrupt handler. This address is entered in the stack by the deadstart program and remains unaltered during system execution. Interrupts cause the hardware to reference stack position 0 without reference to the E register.

#### SUBROUTINE CALLS

Positions 1 through 14 in the program exit stack are used for subroutine return addresses, referred to as SRA in figure 3-4. A subroutine call from a routine or an interrupt advances the E pointer by 1 and stores the routine's return address in the stack. On exit from the subroutine, the return address is read from the current location in the stack. Then the E pointer decrements by 1 to point to the next highest stack location. As a program goes into deeper levels of subroutines, the E count increases and more subroutine return addresses are stored. As the program exits from subroutines, the E count drops back toward 0.

ISHA Interrupt handler start address

SRA Subroutine return address or interrupted subroutine address

1210

ISA Interrupted subroutine address

Figure 3-4. Program Exit Stack

When the E pointer approaches the full limit of the stack, an exit stack interrupt is generated to allow the software to reconfigure the stack. The sequence is as follows:

- 1. E reaches 13 following the execution of a return jump.

- 2. The new subroutine begins execution.

- 3. The next subroutine is called.

- 4. E goes to 14 due to a subroutine call.

- 5. New return address loads to stack position 14.

- The program exit stack boundary flag is set, causing an interrupt.

- 7. Return jump to new subroutine enters a new value into the P register but does not jump.

- 8. Interrupt blocks instruction issue (if system and channel interrupts are enabled).

- 9. Stack loads the interrupted address (P) to position 15.

- 10. Interrupt handler begins executing.

When the E pointer reaches 0 and an exit instruction issues, an interrupt sets and the program jumps to the interrupt handler routine. The sequence is as follows:

- 1. E reaches 0.

- 2. Exit instruction occurs.

- 3. Interrupt sets.

- 4. Interrupt blocks further instruction issue (if system and channel interrupts are enabled).

- 5. Interrupt handler begins executing.

If return jumps are used in an interrupt handler, care must be taken that enough levels are available in the stack. An interrupt with the exit stack pointer at 13 moves the pointer to 14, leaving only one location open. A return jump causing a Program Fetch Request (PFR) interrupt may be issued with the stack pointer at 13. The return address goes into 14 and the interrupt address into 15, leaving two interrupts present—both the exit stack boundary and PFR, with the PFR being the higher priority and no stack locations available. If the E pointer is at 15 and an interrupt or subroutine call is generated, the pointer wraps around and returns to 0.

The program exit stack can be reconfigured by keeping the stack half full, allowing calls to deeper levels or exits to higher levels. The deepest level interrupt is characterized by E equal to 15. For this level of interrupt, the interrupt handler routine saves the higher half of the stack in memory (positions 1 through 7) and moves the lower half of the stack (positions 8 through 15) to the higher part of the stack (positions 1 through 8). Old position 15 holds the interrupted subroutine return address. When the reconfiguration is complete, the interrupt handler routine exits to the interrupted subroutine, and operation continues.

A reconfigured stack at the E equals 0 level exits directly to the interrupt handler routine. This highest level interrupt is characterized by E equal to 0 with the exit stack interrupt present. The interrupt handler routine can then rebuild the original higher half of the stack (reading it from memory), set E to 7, and exit to that subroutine return address.

#### NOTE

If E equals 13 and an interrupt occurs, E goes to position 14, but the Exit Stack Boundary flag does not set.

#### PROGRAM EXIT STACK AND I/O INTERRUPTS

An I/O interrupt is treated much like a subroutine call. The interrupted program address is stored in the program exit stack at the next stack position and the entrance address for the interrupt routine is read from position 0 of the stack. On servicing the interrupt, the hardware clears the System Interrupt Enable flag to prevent other interrupts from interrupting the handling routine.

If return jumps are used in the interrupt handling routine, enough locations must be left in the exit stack to handle the maximum number of levels encountered in the interrupt handling routine. When I/O is finished, the interrupt handler routine sets the System Interrupt Enable flag. The exit at the end of the interrupt handling routine reads the return address for the interrupted program from the exit stack and returns control to that point.

\*\*\*\*\*\*\*\*\*\*\*\*\*\*

#### CAUTION

After any modification to the stack locations or the E pointer, at least 5 CPs must elapse before performing a program exit or a return jump or before enabling system interrupts. The same delay is necessary before using data read from the exit stack or E pointer. To achieve the required delay, perform three circular shifts of 17 positions on the accumulator before exiting the routine. Modifying stack locations or the E pointer should only be done when system interrupts are disabled.

\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*

HR-0030 3-10 B

#### PROGRAM FETCH REQUEST FLAG

The Program Fetch Request (PFR) flag is set during execution of jump instructions 074 through 077 and 120 through 137 when the instruction sequence finds a zero value in operand register d. This condition requests the monitor program to perform a function for this routine.

Setting the PFR flag suspends execution of the current program sequence with an interrupt request at the completion of the interrupted instruction. The monitor program then reads the value of the Channel 1 Interface Input register (which contains d) and interprets that number as identifying a particular request.

An I/O Processor (IOP) adds, subtracts, left shifts, and right shifts by using the Adder and Shifter functional units. Temporary data storage is provided by a block of operand registers. All transfers to operand registers and all results from the functional units pass through the accumulator. The IOP computation section has the following characteristics:

- 16-bit architecture

- Twos complement arithmetic

- Integer addition/subtraction unit

- Shift unit

- Logical product

- 512 operand registers, each 16 bits wide

This section describes the computation section of an IOP. Refer to the I/O Processor block diagram (figure 3-1) showing the organization of the computation section of the IOP.

# OPERAND REGISTERS

Computation in the IOP is supported by 512 operand registers. The operand registers act as temporary locations for data, as index registers, and as indirect memory address registers. Each operand register contains 16 bits of data and has a 1 clock period (CP) access time. The registers are addressed by the Register Pointer (RP) register (see section 3).

The only data path into operand registers is from the accumulator. Data leaving an operand register goes either to the accumulator or the Addend register as operand data, or it can go to the Memory Address (MA) register as memory address data.

#### NOTE

The operand registers are the only mechanism through which the computation section can reference memory.

## MEMORY ADDRESS REGISTER

The 16-bit Memory Address (MA) register holds the address for a Local Memory reference. The MA register receives address information from an operand register and holds it for Local Memory use. This register is used for read and write memory references.

#### FUNCTIONAL UNITS

The IOP computation section has an Adder functional unit and a Shifter functional unit that perform all the arithmetic required by the instruction set.

#### ADDER FUNCTIONAL UNIT

IOP arithmetic is performed in the twos complement Adder functional unit. Adder operands come from the accumulator, instruction fields, B register, Program Address (P) register, operand registers, and Local Memory. Except for accumulator contents, operands come to the Adder through the Addend register. Adder results go to the accumulator for distribution as needed and to the P register. The 17-bit operands are received from the accumulator and returned to the accumulator; the seventeenth bit corresponds to the carry bit of the accumulator. Operands from the Addend register have 16 bits. Branch instructions use the Adder for P address calculations.

The Adder is also used for subtraction. In twos complement arithmetic, subtraction takes place by adding the ones complement of the subtrahend (the number subtracted from the minuend) to the minuend and then adding 1. When subtracting, the contents of the Addend register are inverted and passed to the Adder. The subtraction control signal is a 1, which is added to the intermediate result to give the final difference.

Both add and subtract computations take 1 CP; another CP is required to put the results into the accumulator and the Carry Bit register (described later in this section).

NOTE

For unsigned 16-bit arithmetic, the carry bit is toggled on x - y if x > y or x = y.

#### SHIFTER FUNCTIONAL UNIT

The Shifter functional unit implements IOP shifting instructions of up to 31 places left either circularly or end-off with zero fill. The Shifter receives the 17-bit accumulator data (including carry bit) to be shifted and the 5-bit (20 through 24) Addend register shift count. The Shifter accomplishes right shifting by using the inverted shift count. The shifted results (17 bits) are returned to the accumulator and the Carry Bit register (described later in this section). The 1 CP required for the shift is independent of the shift count and type of shift. Shift instructions require 2 CPs.

The maximum number of places an operand can be shifted is 31. If the shift count is 0, no shift occurs. If the count is greater than 16 for an end-off shift, the zero-filling clears the result. In all shifts, the carry bit is treated as the high-order bit  $(2^{16})$  of the operand and the result.

## ACCUMULATOR

The 16-bit accumulator register temporarily stores operands and results. Data from several sources can be routed to the accumulator; many destinations for accumulator contents are available. Sources and destinations are listed below.

| Sources               | Destinations      |

|-----------------------|-------------------|

| B register            | B register        |

| Operand registers     | Operand registers |

| Adder/Shifter         | Adder/Shifter     |

| Memory                | Memory            |

| I/O channels          | I/O channels      |

| II register $d$ field |                   |

| II register k field   |                   |

Logic at the input of the accumulator is enabled by the logical product instructions and creates the logical product of two operands: the accumulator and the input operand. The result goes directly to the accumulator with no extra time taken for the logical product function.

Program branch instructions require arithmetic to form the destination address from two operands. These instructions (070 through 137) do not alter the contents of the accumulator. Execution of these sequences is performed with a separate background accumulator not visible to the programmer.

## CARRY BIT REGISTER

The 1-bit Carry Bit register holds the carry generated in the Adder or Shifter functional units. The carry bit is treated as if it were bit  $2^{16}$  of the accumulator operand and is included in all add, subtract, and shift operations.

The carry bit is set by several conditional instructions that test I/O channel flags. The carry bit is also used as a criterion for many conditional jump and return jump instructions.

#### ADDEND REGISTER

The 16-bit Addend register supplies operands to the Adder and Shifter functional units. Whenever two operands are required, the accumulator supplies one operand and the Addend register supplies the other. The Addend register receives data from the B register, the instruction stack, the operand registers, or Local Memory. The Addend register sends data to the Adder and the Shifter functional units.

HR-0030 4-4 B

An I/O Processor (IOP) supports up to 40 channels for input or output (I/O) use. These 40 channels use six direct memory access (DMA) ports to Local Memory. Twelve channels and one port are assigned standard functions for the system, but the remainder are free for peripheral device or Cray mainframe support.

An IOP input/output section has the following characteristics:

- Supported by six full-duplex, direct memory access (DMA) ports

- Approximately 100 Mbytes/s per DMA port (maximum speed)

- 16 data bits, 2 status bits (Busy and Done)

- Channel number selected by instruction or B register contents

- Simultaneous input and output through separate ports

This section describes I/O configuration, I/O speeds, channel characteristics, standard channels, and the interrupt sequence.

## I/O CONFIGURATION

The I/O channels are numbered in octal. I/O channels 0 through  $13_8$  are standard for all IOPs. Channels  $14_8$  through  $47_8$  are variable. For control purposes, functions can be sent to and statuses can be received from each IOP channel.

The interfaces associated with channels  $14_8$  through  $47_8$  have five DMA ports to Local Memory. (The sixth DMA port connects to Buffer Memory.) Faster devices connect to an IOP through the DMA ports, allowing block transfers. Slower devices can be supported by accumulator channels. Several devices can be interfaced to share a single DMA port, with each device assigned a unique channel number. This method supports groups of four disk storage units and Block Multiplexer Channels.

For interrupts, channels are assigned priorities that cause them to be serviced in the following order: Channel 0, Channel 1, and Channels 2 through  $47_8$  in descending priority.

## I/O SPEEDS

Each DMA port can transfer a block of data at the approximate rate of 100 Mbytes/s. DMA ports can transfer data into Local Memory while other DMA ports simultaneously transfer data from Local Memory. One DMA port can transfer data into Local Memory and one DMA port can transfer data from Local Memory at a sustained rate of 100 Mbytes/s, barring Local Memory conflicts. If more than one port is transferring data either into or from Local Memory, speed degradation occurs.

The maximum speed of accumulator channels depends on the speed of the interrupt service routine.

## CHANNEL CHARACTERISTICS

Operating characteristics for the accumulator channels and the channels using DMA ports are similar in many respects. The following descriptions outline the control and data signals used and give the requirements for each signal. The channels are described independently of the interfaces that can be connected to them. (Channel interfaces are described in section 7.)

#### ACCUMULATOR CHANNELS

The accumulator channels permit communication among the IOPs. Each accumulator channel uses the following signals:

Function Designators

Function Strobe

Accumulator Data

Read Done

Read Busy

Busy/done

Master Clear

Clock

Interrupt

Each interface has two 1-bit registers comprising the Done and Busy flags for the channel. The interface can set or clear these flags, and the IOP can sample them through the use of the Read Done and Read Busy control signals.

## Function Designators signal

Bits  $2^0$  through  $2^3$  of the f field of an I/O instruction are used as a function code (0 through  $17_8$ ) to an interface (see section 6). This function is interpreted by the interface and can specify different operations to different interfaces. The function code consists of 4 bits sent on lines from the IOP instruction logic to the interface. It precedes any other channel action. The function code is stable on the lines for only 1 CP.

### Function Strobe signal

The Function Strobe signal accompanies the function code bits. It alerts the interface to the presence of the function code.

## Accumulator Data signal

The use of the Accumulator Data signal depends on the function code and the particular interface. For example, the signal can be treated as a parameter for a Buffer Memory transfer or as a character for a display. Data leaving the accumulator is reliable only for the clock period (CP) containing the Function Strobe signal. The meaning of data coming from the interface to the accumulator also depends on the function code and interface.

## Read Done signal