2/91 **PRELIMINARY INFORMATION**

Cray Research Proprietary

Cray Research, Inc.

Any shipment to a country outside of the United States requires a letter of assurance from Cray Research, Inc.

This document is the property of Cray Research, Inc. The use of this document is subject to specific license rights extended by Cray Research, Inc. to the owner or lessee of a Cray Research, Inc. computer system or other licensed party according to the terms and conditions of the license and for no other purpose.

Cray Research, Inc. Unpublished Proprietary Information — All Rights Reserved.

CRAY<sup>®</sup>, CRAY-1<sup>®</sup>, Cray Ada<sup>®</sup>, CRAY Y-MP<sup>®</sup>, HSX<sup>®</sup>, SSD<sup>®</sup>, UNICOS<sup>®</sup>, and X-MP EA<sup>®</sup> are federally registered trademarks and Autotasking<sup>TM</sup>, CCI<sup>TM</sup>, CF7<sup>TM</sup>, CFT<sup>TM</sup>, CFT7<sup>TM</sup>, COS<sup>TM</sup>, CRAY X-MP<sup>TM</sup>, CRAY XMS<sup>TM</sup>, CRAY Y-MP2E<sup>TM</sup>, CRAY-2<sup>TM</sup>, CSIM<sup>TM</sup>, CVT<sup>TM</sup>, Delivering the power ...<sup>TM</sup>, IOS<sup>TM</sup>, MPGS<sup>TM</sup>, OLNET<sup>TM</sup>, RQS<sup>TM</sup>, SEGLDR<sup>TM</sup>, SMARTE<sup>TM</sup>, SUPERLINK<sup>TM</sup>, and UNICHEM<sup>TM</sup> are trademarks of Cray Research, Inc.

Requests for copies of Cray Research, Inc. publications should be directed to:

1:05

CRAY RESEARCH, INC. Logistics 6251 South Prairie View Road Chippewa Falls, WI 54729

Comments about this publication should be directed to:

CRAY RESEARCH, INC. Hardware Publications and Training 770 Industrial Blvd. Chippewa Falls, WI 54729

### Title: IOS<sup>TM</sup> Model E Hardware Maintenance Manual Number: CMM-xxxx-PR2

Your feedback on this publication will help us provide better documentation in the future. Please take a moment to answer the few questions below.

For what purpose did you primarily use this manual?

- \_\_\_\_\_Troubleshooting

- \_\_\_\_\_Tutorial or introduction

- \_\_\_\_\_Reference information

- \_\_\_\_Classroom use

- Other please explain \_\_\_\_\_

Using a scale from 1 (poor) to 10 (excellent), please rate this manual on the following criteria and explain your ratings:

\_\_\_\_\_Accuracy \_\_\_\_\_\_ Organization \_\_\_\_\_\_ Readability \_\_\_\_\_\_ Physical qualities (binding, printing, page layout) \_\_\_\_\_\_ Amount of diagrams and photos \_\_\_\_\_\_ Quality of diagrams and photos \_\_\_\_\_\_ Completeness (Check one) \_\_\_\_\_Too much information \_\_\_\_\_\_ Too little information \_\_\_\_\_\_

\_\_\_\_\_Just the right amount of information

Your comments help Hardware Publications and Training improve the quality and usefulness of your publications. Please use the space provided below to share your comments with us. When possible, please give specific page and paragraph references. We will respond to your comments in writing within 48 hours.

ARCH.

INC

|           | n an San San San San San San San San San                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|           | $(1-\lambda) = \frac{1}{2} \left[ \frac$ |      |

| NAME      | and the second                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | _    |

| JOB TITLE | ter and the second s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | _    |

| FIRM      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |

| ADDRESS   | s second s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | - RE |

| CITY      | STATEZIP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | _    |

| DATE      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |

<sup>[</sup>or attach your business card]

# **Record of Revision**

Each time this manual is revised and reprinted, all changes issued against the previous version are incorporated into the new version, and the new version is assigned an alphabetic level which is indicated in the publication number on each page of the manual.

Changes to part of a page are indicated by a change bar in the margin directly opposite the change. A change bar in the footer indicates that most, if not all, of the page is new. If the manual is rewritten, the revision level changes but the manual does not contain change bars.

REVISION

### DESCRIPTION

November 1990 - Preliminary Information.

February 1991 - Preliminary version for classroom use only. Sections 1 and 9 have been updated.

.

.

# CONTENTS

## 1 INTRODUCTION

| IOS-E Modules           | 1-5  |

|-------------------------|------|

| J/O Processor           | 1-7  |

| Channels                | 1-9  |

| Appannels 10 through 17 | 1-10 |

| Chapters 20 and 21      | 1-10 |

| Channels 27/hrough 25   | 1-11 |

| Channels 26 and 27      | 1-11 |

| Channels 30 through 31  | 1-11 |

| Channel Adapters        | 1-11 |

## 2 I/O PROCESSOR

| CPU Control Signals                          | 2-4  |

|----------------------------------------------|------|

| 3AT Control Signals                          | 2-4  |

| 3AJ Control Signals                          | 2-6  |

| 3AK Control Signals                          | 2-8  |

| 3AR Control Signals                          | 2-8  |

| CPU Local Memory References                  | 2-10 |

| CPU Local Memory Write Reference Sequence    | 2-10 |

| CPU Local Memory Read Reference Sequence     | 2-11 |

| CPU Local Memory Fetch Reference Sequence    | 2-13 |

| Direct Memory Access Local Memory References | 2-15 |

| Local Memory Write Reference                 | 2-15 |

| Local Memory Read Reference                  | 2-16 |

| Direct Memory Access I/O Function Sequence   | 2-21 |

| Accumulator Fanin/Fanout and Busy/Done Fanin | 2-23 |

Cray Research Proprietary Preliminary Information

۷

# **3 CLUSTER INTERFACE AND WORKSTATION INTERFACE**

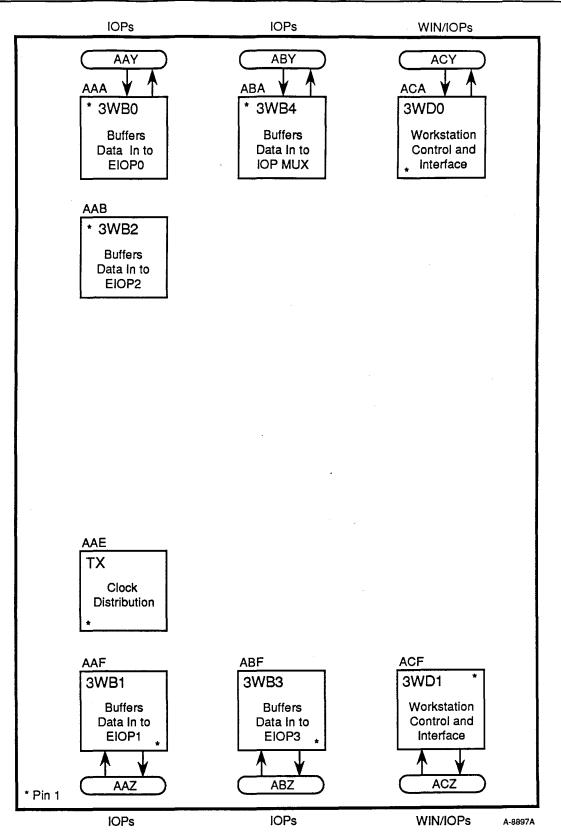

| Cluster Interface/Workstation Interface Quarter Boards  | 3-3  |

|---------------------------------------------------------|------|

| Cluster Interface/Workstation Interface Data Flow       | 3-3  |

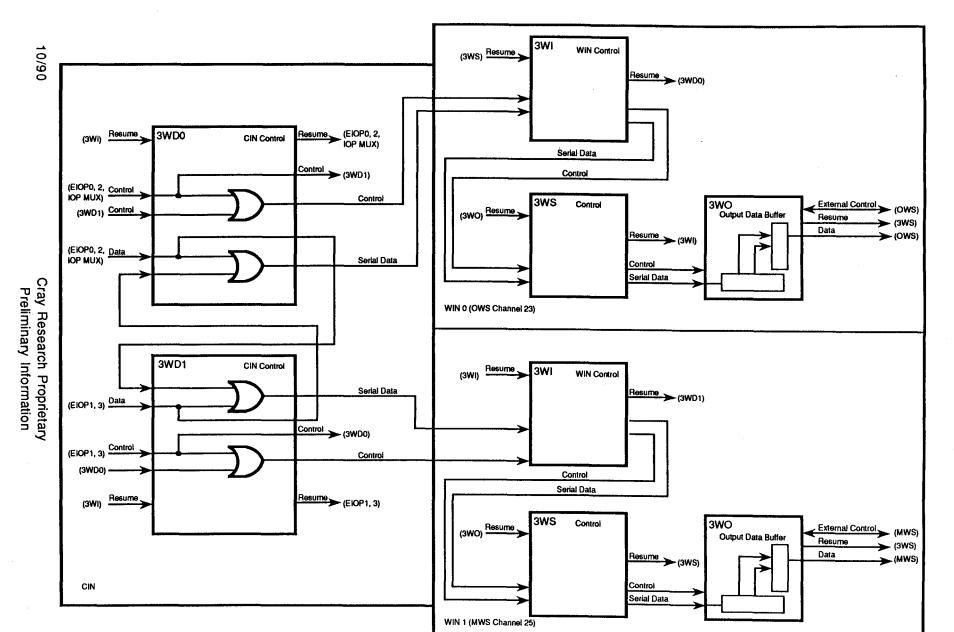

| Six Mbyte Low-speed Protocol                            | 3-6  |

| Cluster Interface/Workstation Interface Input Sequence  | 3-6  |

| Cluster Interface/Workstation Interface Output Sequence | 3-16 |

| WIN 2 Return I/O Status Request Sequence                | 3-24 |

| WIN 3 Select Clock Margins Sequence                     | 3-24 |

| WIN 4 Workstation Interface Loopback Sequence           | 3-25 |

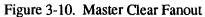

| Master Clear Fanout                                     | 3-27 |

| I/O Master Clear                                        | 3-27 |

| WIN 5 System Master Clear                               | 3-27 |

| WIN 0 Function 11 Cluster Master Clear and              |      |

| Function 10 IOP Master Clear                            | 3-27 |

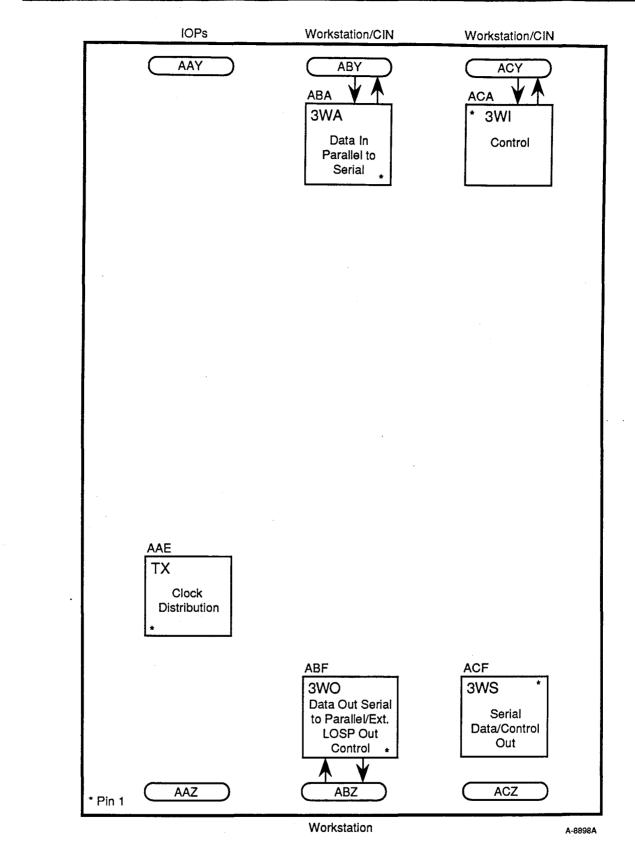

### 4 BUFFER BOARD

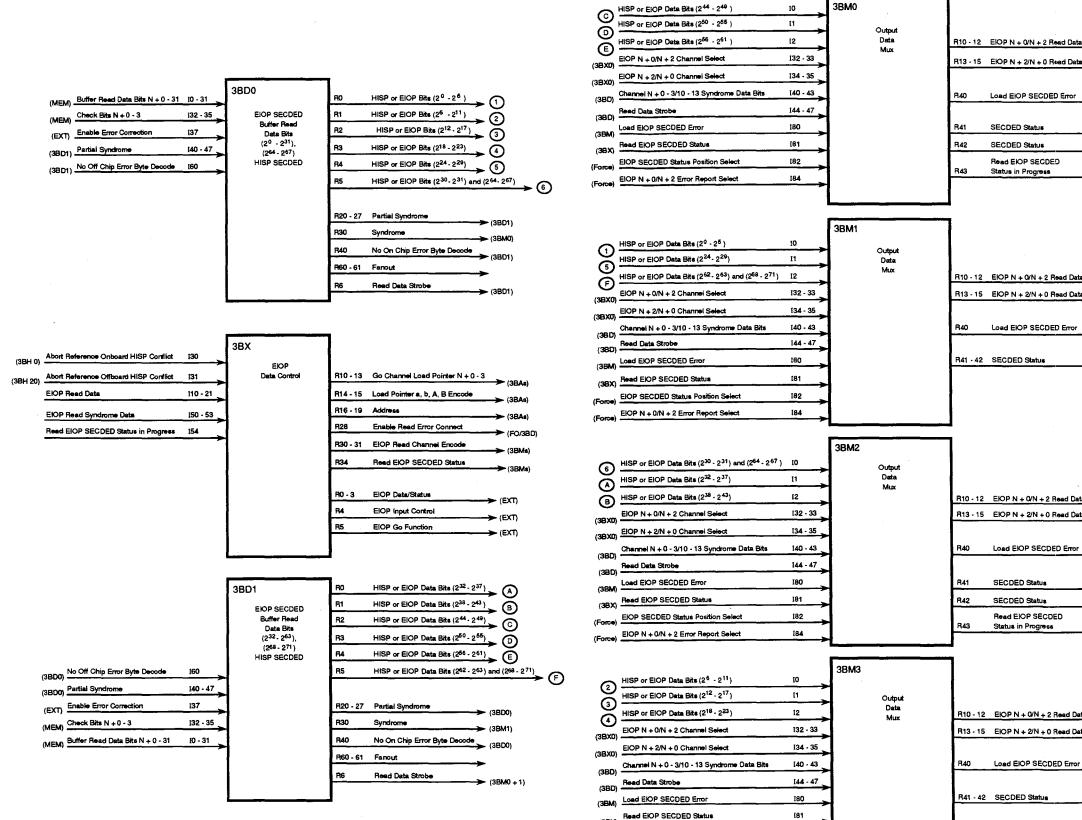

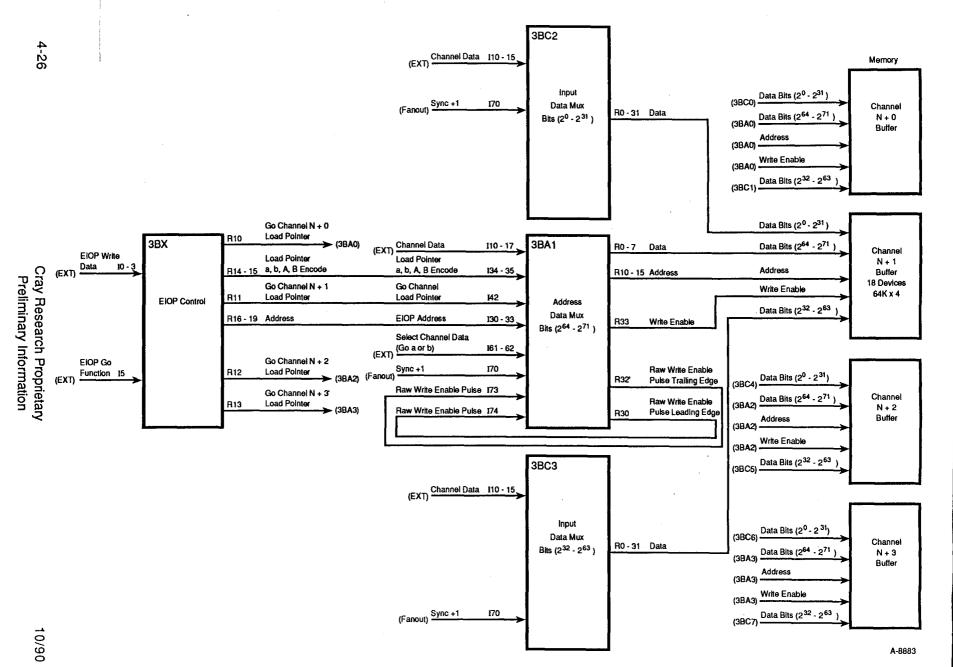

| EIOP Write Data Sequence                  | 4-6  |

|-------------------------------------------|------|

| EIOP Read Data Sequence                   | 4-13 |

| EIOP Read Data Fanout                     | 4-21 |

| Channel Adapter Write Sequence            | 4-22 |

| Channel Adapter Read Sequence             | 4-27 |

| High-speed Write Data Sequence            | 4-31 |

| High-speed Data Fanin into Channel Memory | 4-39 |

| High-speed Read Data Fanout               | 4-45 |

## 5 HCM HIGH-SPEED/LOW-SPEED QUARTER BOARD

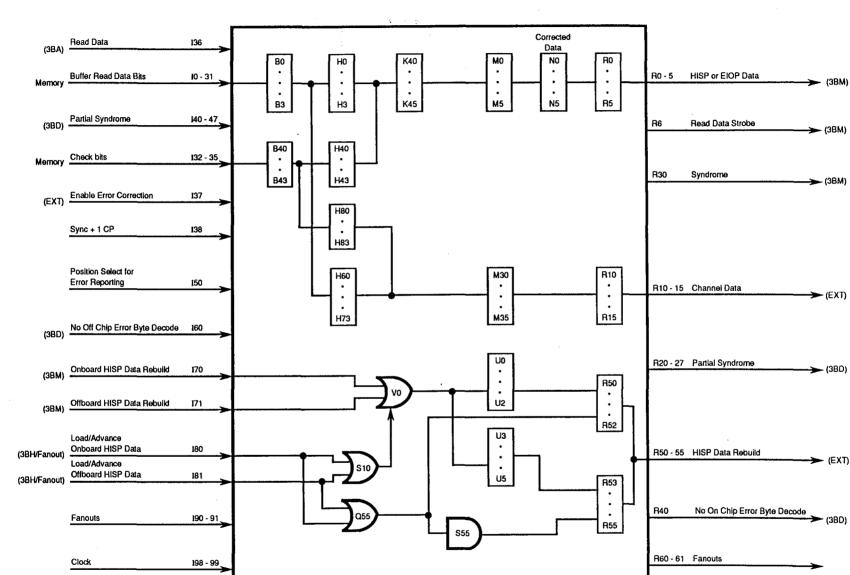

| High-speed Data Flow        | 5-1  |

|-----------------------------|------|

| Low-speed Data              | 5-3  |

| High-speed Protocol         | 5-3  |

| High-speed Data In Sequence | 5-4  |

| High-speed Data Out         | 5-7  |

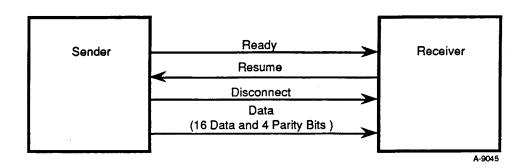

| Low-speed Protocol          | 5-12 |

| 6-Mbyte Low-speed Protocol  | 5-12 |

| 50-Mbyte MISP Protocol      | 5-13 |

| Low-speed Data In Sequence  | 5-14 |

| Low-speed Data Out Sequence | 5-16 |

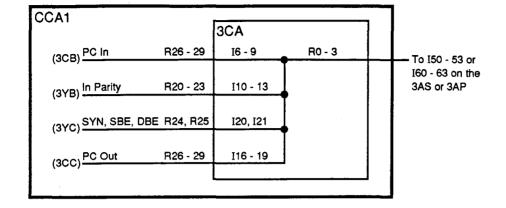

## 6 CCA1 LOW-SPEED QUARTER BOARD

| CCA1 Data Flow                                       | 6-1 |

|------------------------------------------------------|-----|

| Low-speed Channel Protocol                           | 6-3 |

| 6-Mbyte Low-speed Channel Protocol                   | 6-3 |

| 12-Mbyte Networks System Corporation Input Protocol  | 6-3 |

| 12-Mbyte Networks System Corporation Output Protocol | 6-4 |

| CCA1 Low-speed Channel Data In Sequence              | 6-4 |

| CCA1 Low-speed Channel Data Out Sequence             | 6-7 |

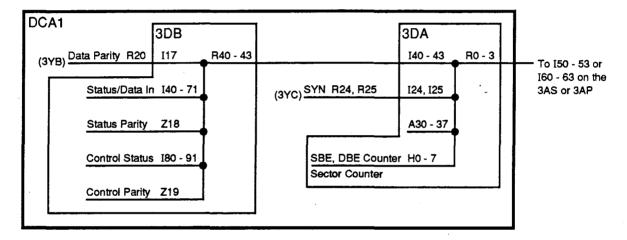

## 7 DCA1 DISK DRIVE QUARTER BOARD

| DCA1 Data Flow                            | 7-1 |

|-------------------------------------------|-----|

| DCA1 Data In Sequence (Disk Drive Read)   | 7-3 |

| DCA1 Data Out Sequence (Disk Drive Write) | 7-6 |

## 8 DCA2 IPI DISK DRIVE CONTROLLER QUARTER BOARD

| DCA2 Data Flow                 | 8-2  |  |

|--------------------------------|------|--|

| IPI Protocol                   | 8-5  |  |

| DCA2 Autoload Sequence         | 8-6  |  |

| DCA2 Autodump Sequence         | 8-8  |  |

| DCA2 Disk Drive Read Sequence  | 8-10 |  |

| DCA2 Disk Drive Write Sequence | 8-16 |  |

## 9 TCA1 TAPE CONTROLLER QUARTER BOARD

| TCA1 Data Flow                           | 9-2  |

|------------------------------------------|------|

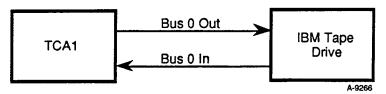

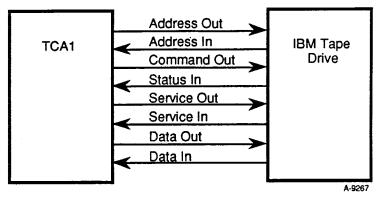

| IBM Protocol                             | 9-2  |

| Data Bus                                 | 9-4  |

| Tag Lines                                | 9-4  |

| Select Lines                             | 9-5  |

| TCA1 Autoload Sequence                   | 9-6  |

| TCA1 Autodump Sequence                   | 9-6  |

| TCA1 Tape Drive Select and Read Sequence | 9-6  |

| TCA1 Tape Drive Write Sequence           | 9-13 |

## 10 HCA3/HCA4 HIPPI QUARTER BOARDS

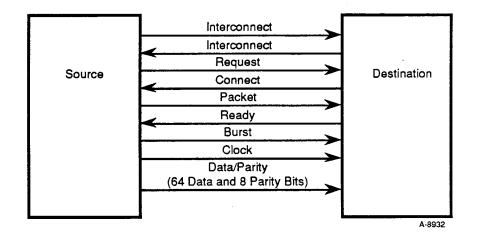

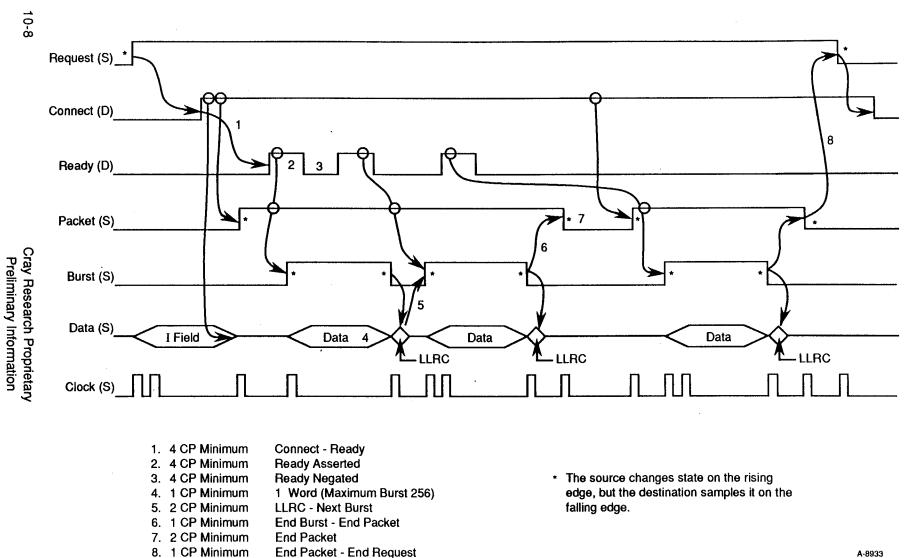

| HIPPI Channel Data Flow      | 10-2  |

|------------------------------|-------|

| HIPPI Channel Protocol       | 10-6  |

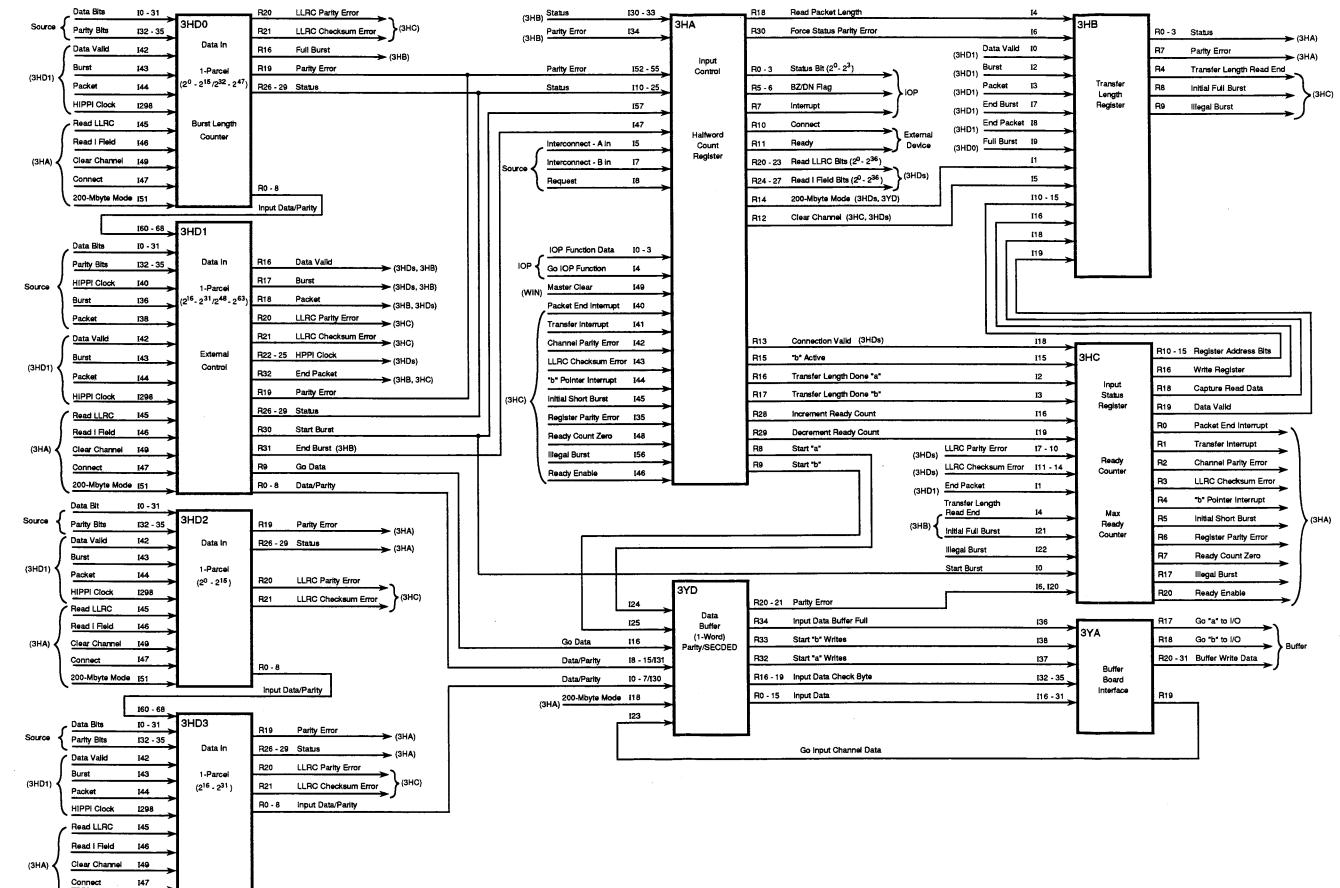

| HCA3 HIPPI Data In Sequence  | 10-9  |

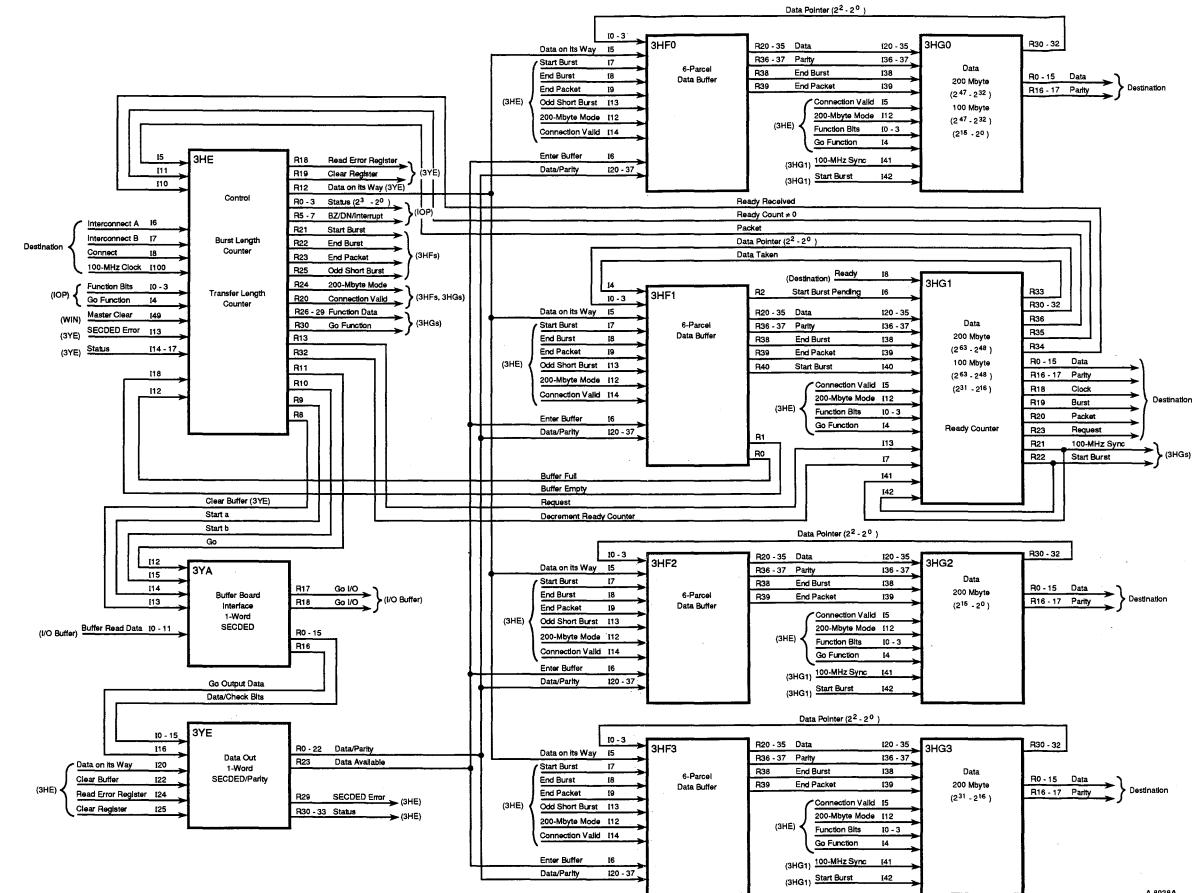

| HCA4 HIPPI Data Out Sequence | 10-17 |

| Figure 1-1. Cluster Module Layout                                | 1-3     |

|------------------------------------------------------------------|---------|

| Figure 1-2. Cluster Module Layout                                | 1-6     |

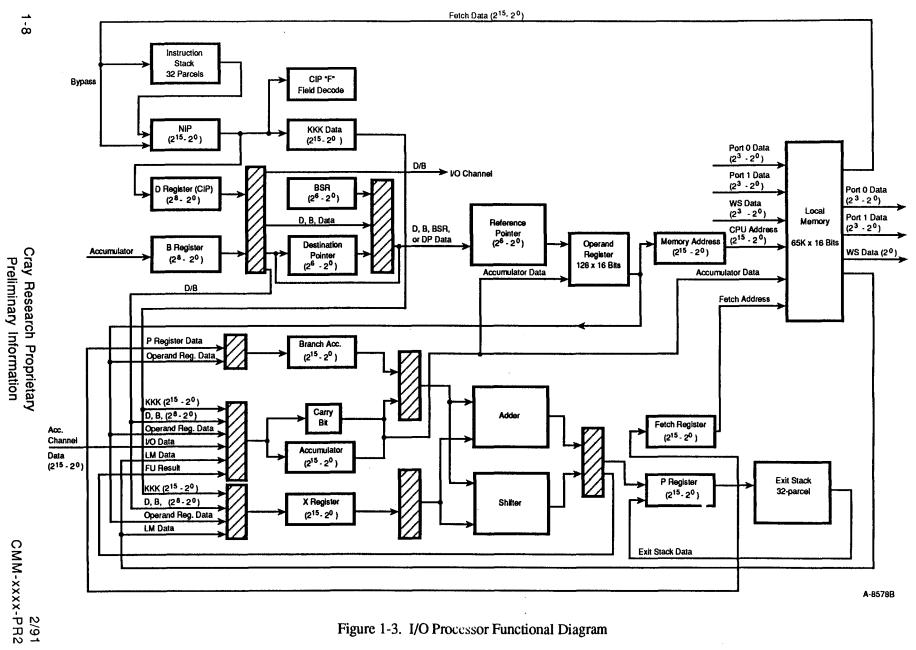

| Figure 1-3. I/O Processor Functional Diagram                     | 1-8     |

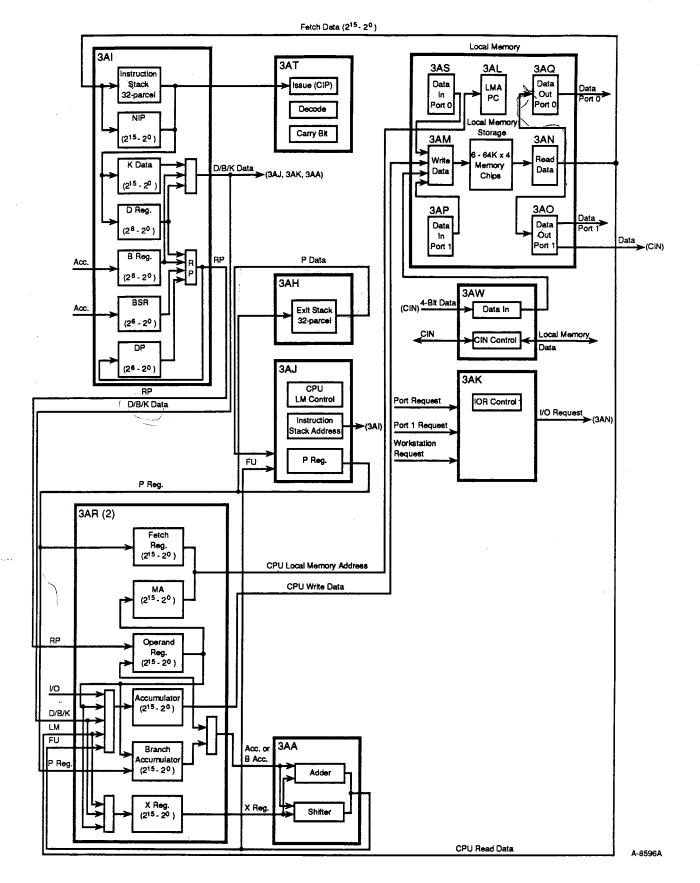

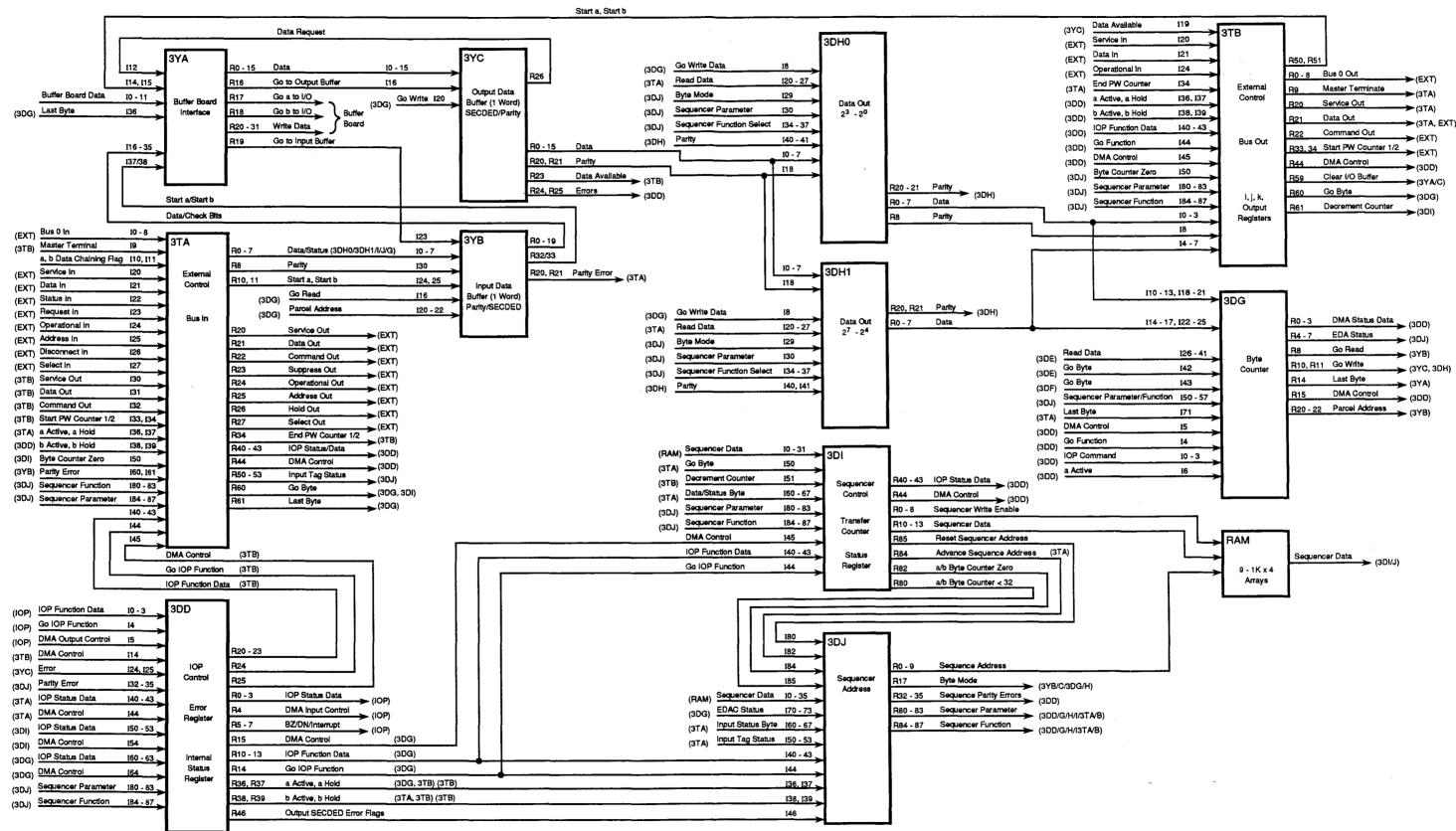

| Figure 2-1. IOP Complete Block Diagram                           | 2-3     |

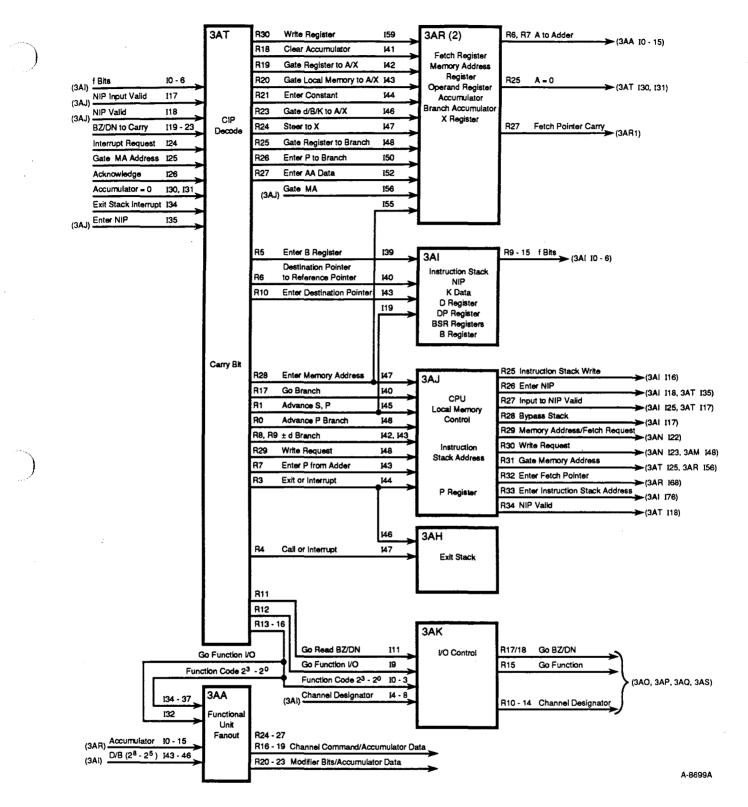

| Figure 2-2. Issue and Control                                    | 2-9     |

| Figure 2-3. CPU Local Memory Write, Read, and Fetch Refere       | nce2-14 |

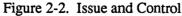

| Figure 2-4. Local Memory Block Diagram and Control               | 2-19    |

| Figure 2-5. Go Function Channel and Parameter Fanout             | 2-22    |

| Figure 2-6. Accumulator Fanin                                    | 2-24    |

| Figure 2-7. CCA1, DCA1, and TCA1 Fanin                           | 2-25    |

| Figure 2-8. HISP/LOSP Fanin                                      | 2-26    |

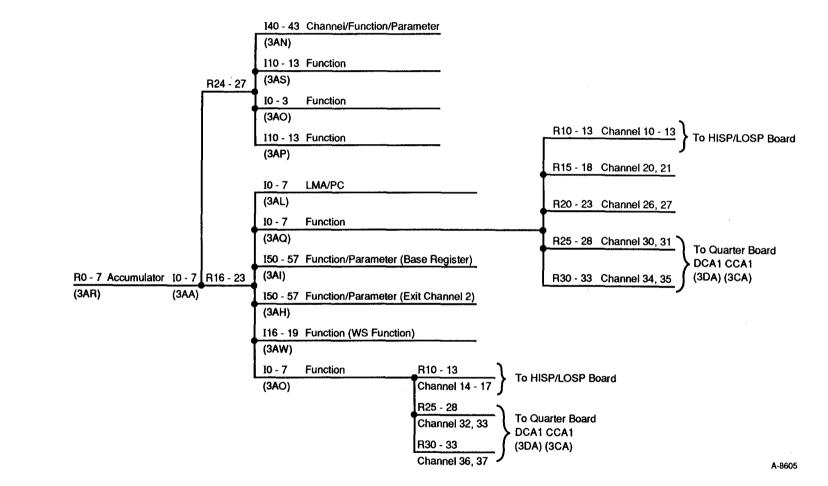

| Figure 2-9. Accumulator Fanout                                   | 2-27    |

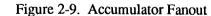

| Figure 2-10. Quarter Board Fanout                                | 2-28    |

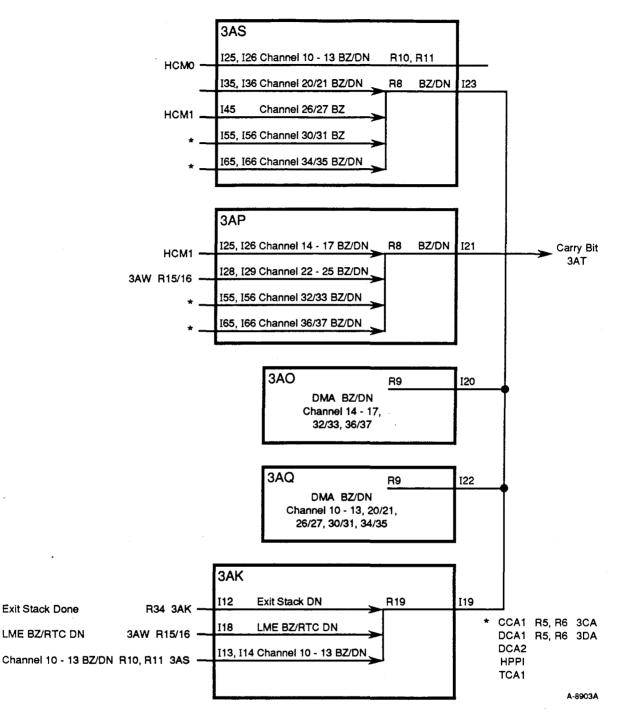

| Figure 2-11. Busy/Done Fanin                                     | 2-29    |

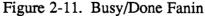

| Figure 2-12. IOP Quarter Board IC Layout                         | 2-30    |

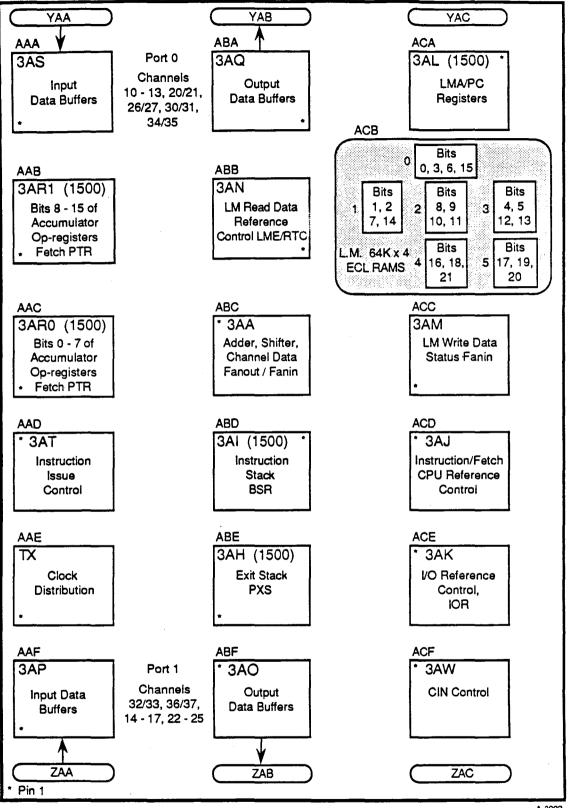

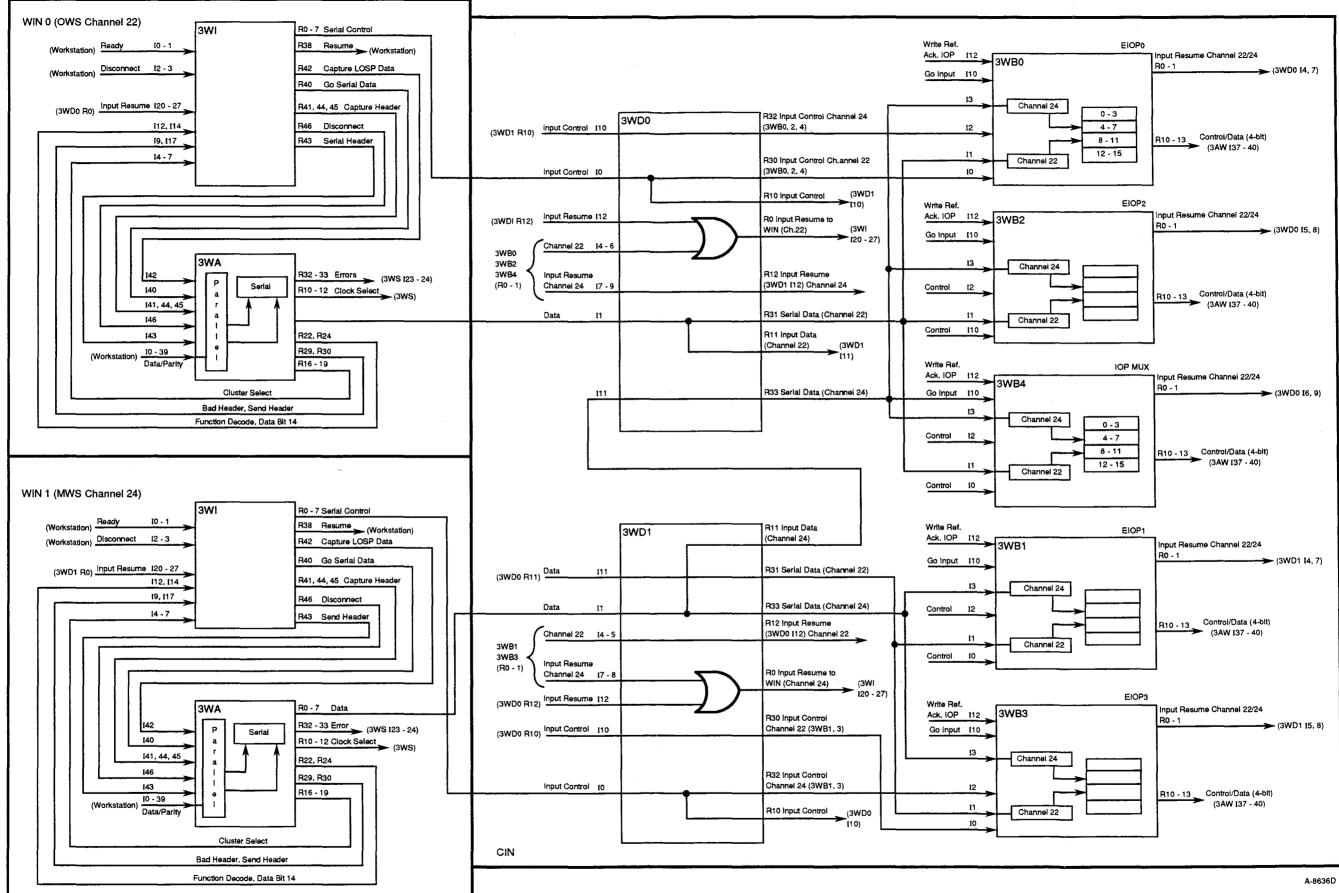

| Figure 3-1. CIN/WIN Block Diagram                                | 3-2     |

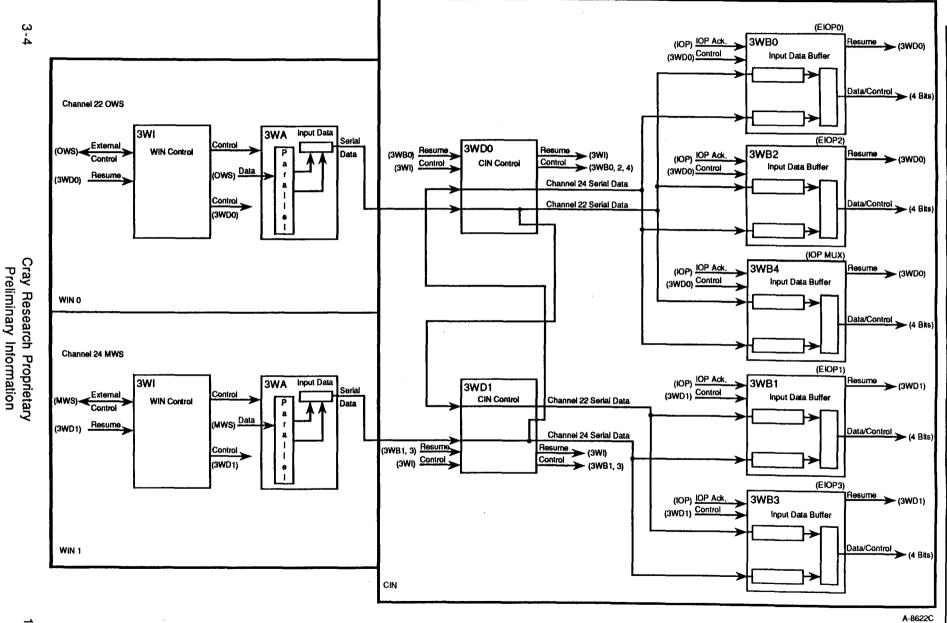

| Figure 3-2. CIN/WIN Input Block Diagram                          | 3-4     |

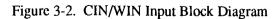

| Figure 3-3. CIN/WIN Output Block Diagram                         | 3-5     |

| Figure 3-4. 6-Mbyte LOSP Protocol                                | 3-6     |

| Figure 3-5. CIN/WIN Input Block Diagram and Control              | 3-13    |

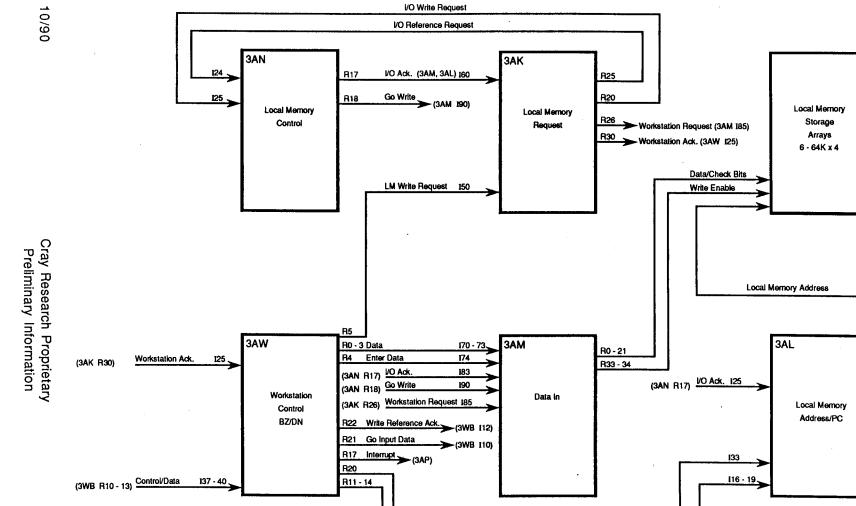

| Figure 3-6. Workstation Local Memory Write Block Diagram         | 3-15    |

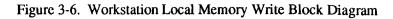

| Figure 3-7. CIN/WIN Output Block Diagram and Control             | 3-21    |

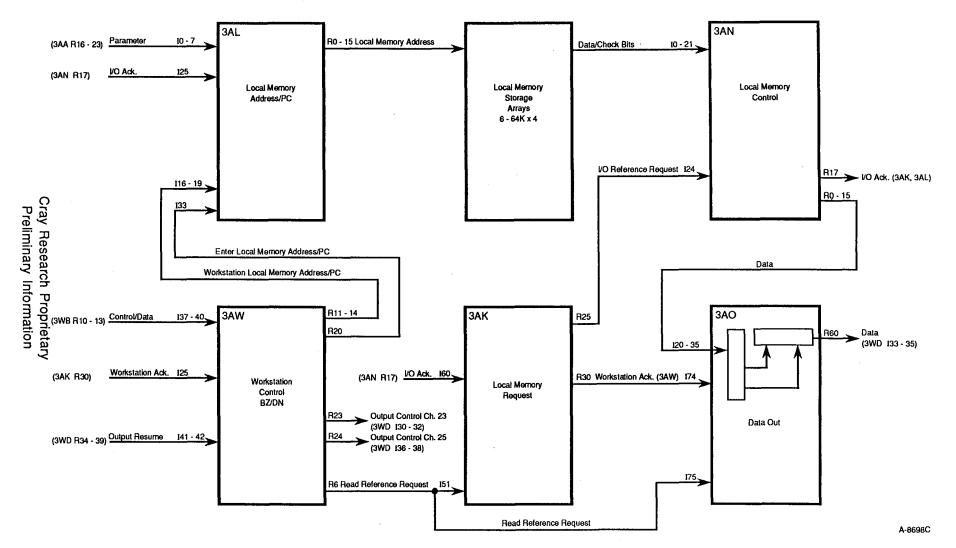

| Figure 3-8. Workstation Local Memory Write Block Diagram         | 3-23    |

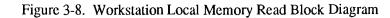

| Figure 3-9. WIN Status, Clock Select, and Loopback Block Diagram | 3-26    |

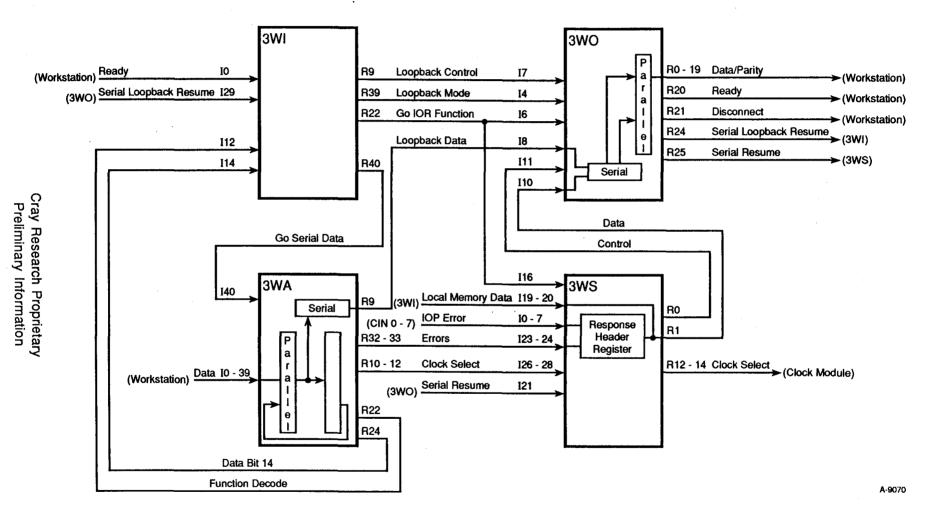

| Figure 3-10. Master Clear Fanout                                 | 3-28    |

| Figure 3-11. CIN Quarter Board Integrated Circuit Layout         | 3-30    |

| Figure 3-12. WIN Quarter Board Integrated Circuit Layout         | 3-31    |

| Figure 4-1. I/O Buffer Module (A Board)                          | 4-3     |

| Figure 4-2. I/O Buffer                                           | 4-5     |

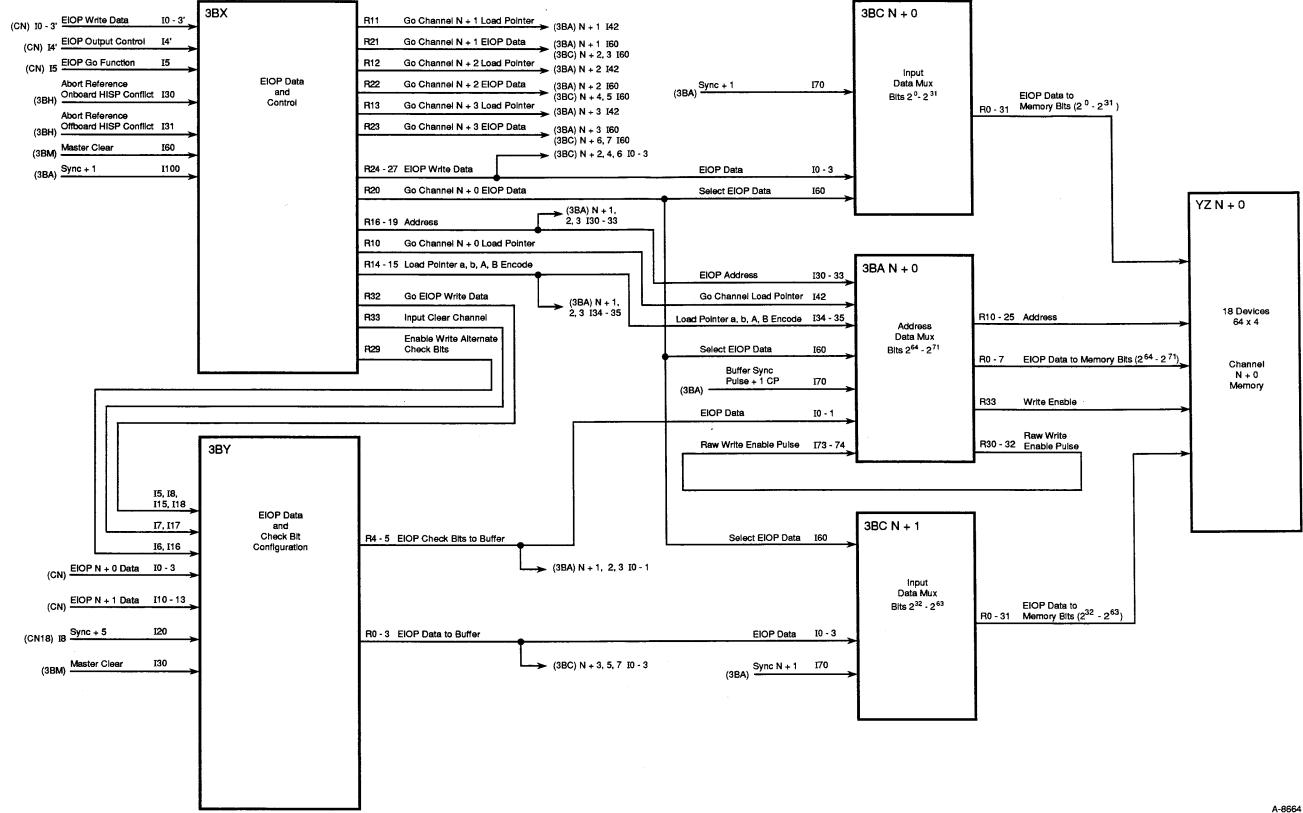

| Figure 4-3. IOS Model E EIOP Write to Memory                     | 4-9     |

.

10/90

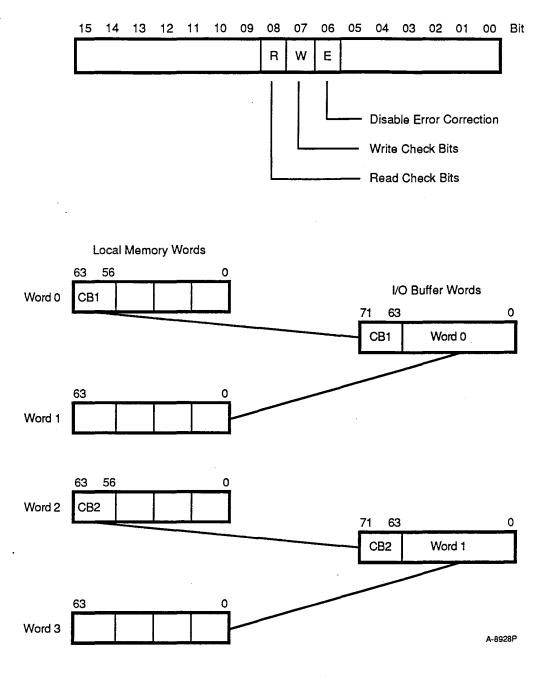

| Figure 4-4. I/O Buffer Write Check Bits Diagnostic Mode  | 4-11 |

|----------------------------------------------------------|------|

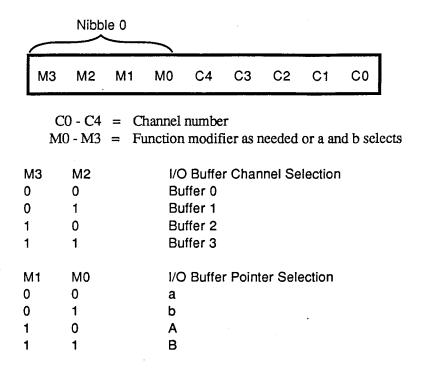

| Figure 4-5. Accumulator and Modifier Bits                | 4-12 |

| Figure 4-6. EIOP Output from Channel 0                   | 4-19 |

| Figure 4-7. Channel Data Input                           | 4-26 |

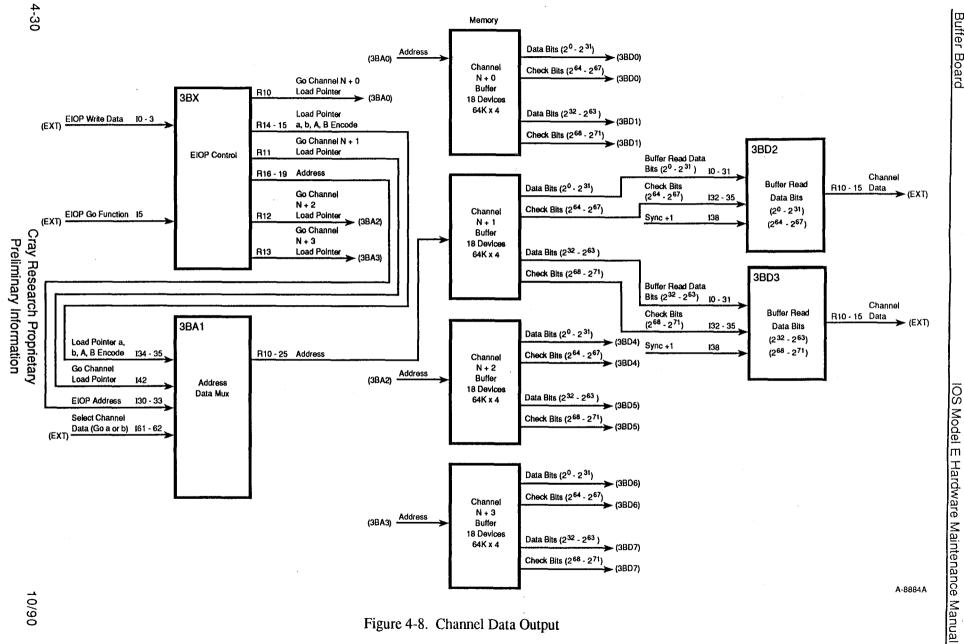

| Figure 4-8. Channel Data Output                          | 4-30 |

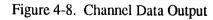

| Figure 4-9. HISP Input                                   | 4-37 |

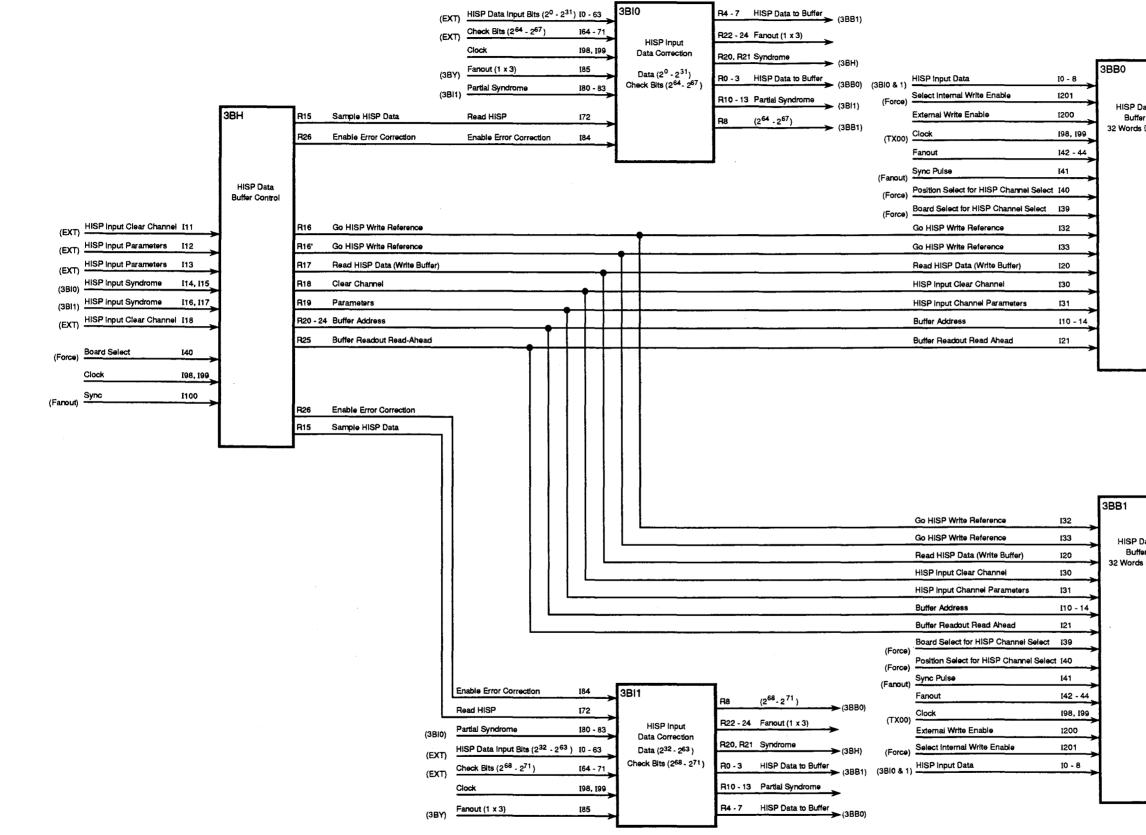

| Figure 4-10. HISP Output from Channel 0                  | 4-43 |

| Figure 4-11. I/O Buffer Chip Map (A Board)               | 4-49 |

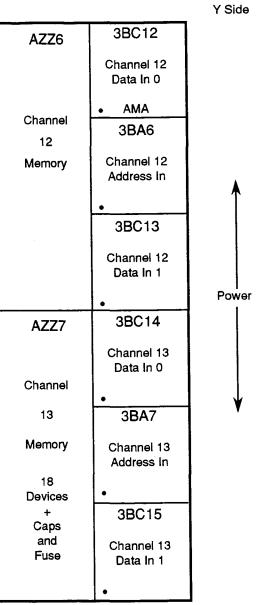

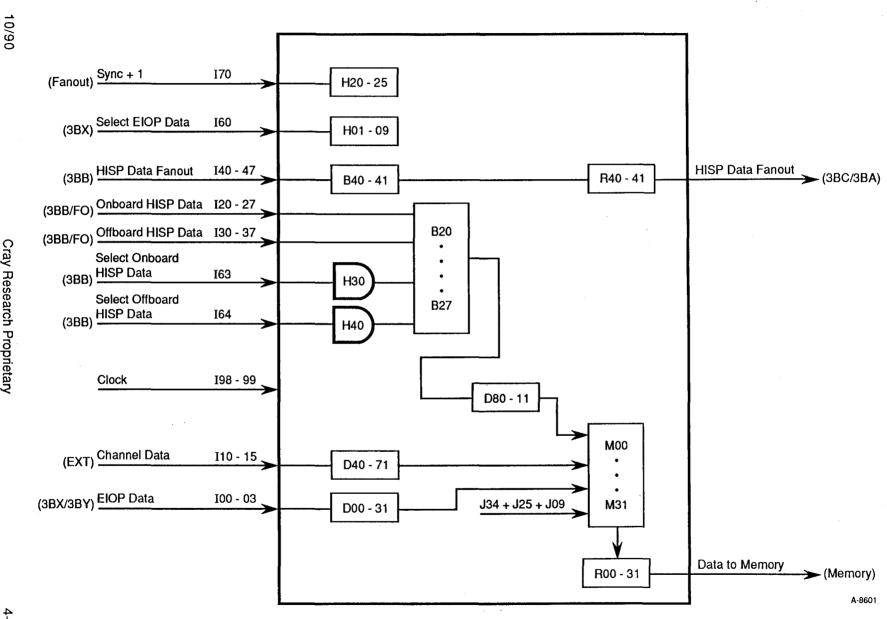

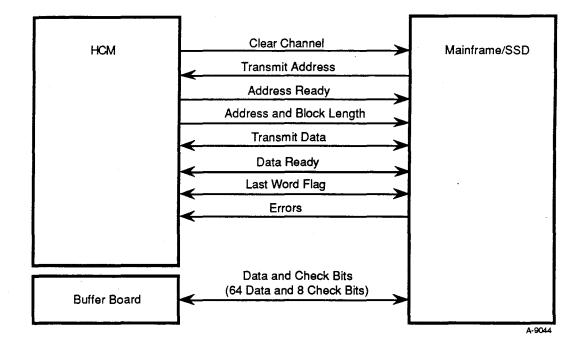

| Figure 4-12. IOS Model E 3BC                             | 4-51 |

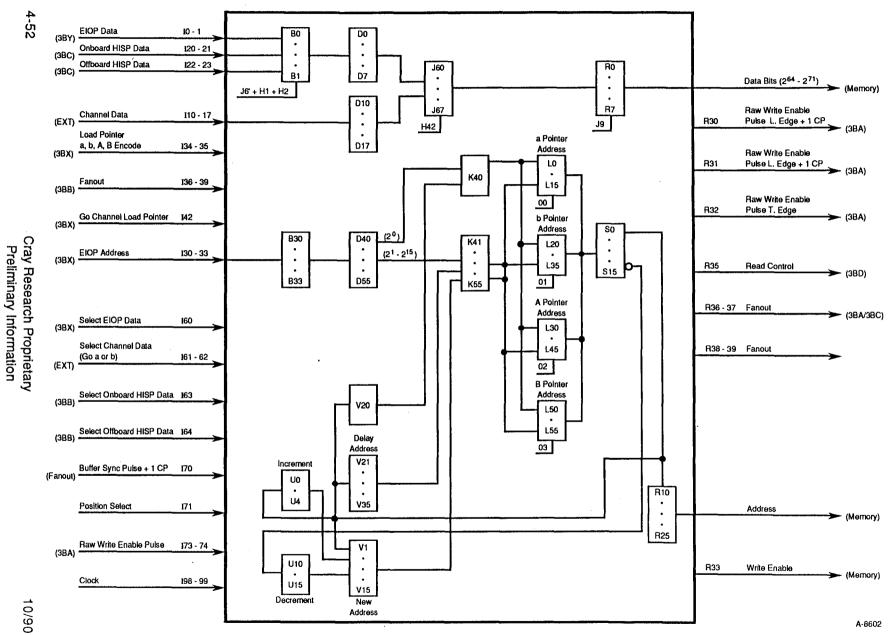

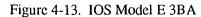

| Figure 4-13. IOS Model E 3BA                             | 4-52 |

| Figure 4-14. IOS Model E 3BD                             | 4-53 |

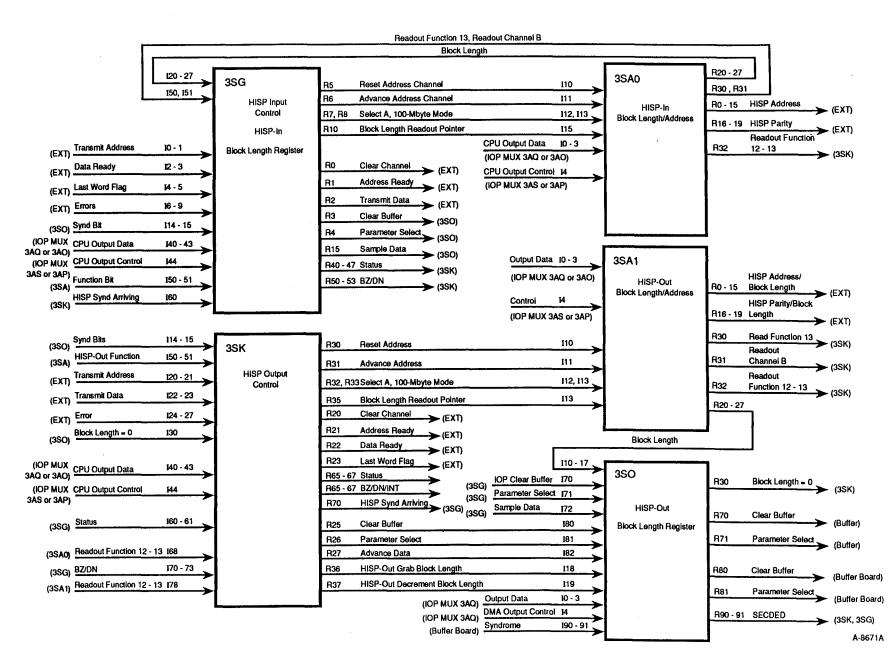

| Figure 5-1. HISP/LOSP MUX Block Diagram                  | 5-2  |

| Figure 5-2. High-speed Protocol Block Diagram            | 5-4  |

| Figure 5-3. HISP MUX In/Out Block Diagram and Control    | 5-10 |

| Figure 5-4. 6-Mbyte LOSP Protocol                        | 5-13 |

| Figure 5-5. 50-Mbyte MISP Protocol                       | 5-13 |

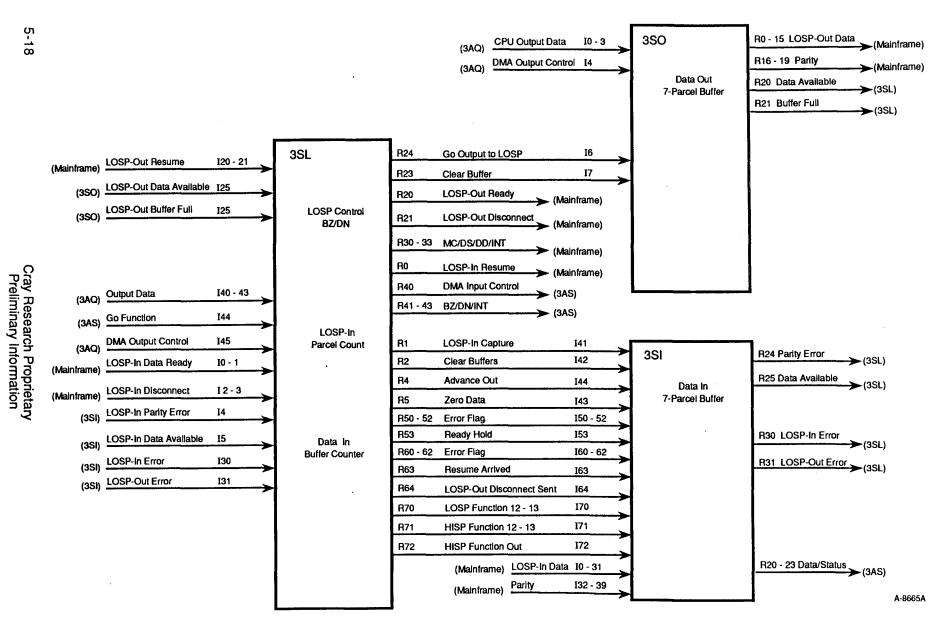

| Figure 5-6. LOSP MUX In/Out Block Diagram and Control    | 5-18 |

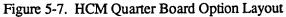

| Figure 5-7. HCM Quarter Board Option Layout              | 5-19 |

| Figure 6-1. CCA1 Block Diagram                           | 6-2  |

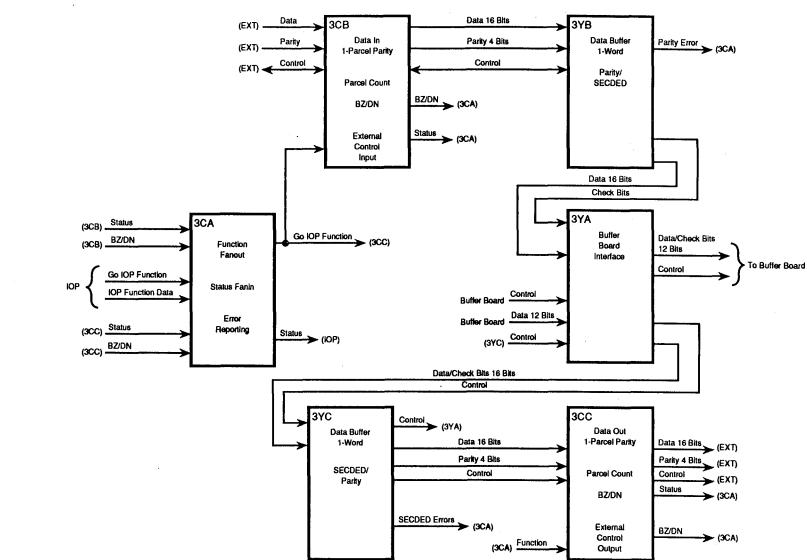

| Figure 6-2. 6-Mbyte LOSP Channel Protocol                | 6-3  |

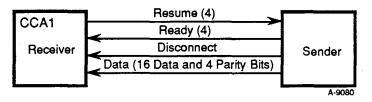

| Figure 6-3. 12-Mbyte NSC Input Protocol                  | 6-4  |

| Figure 6-4. 12-Mbyte NSC Output Protocol                 | 6-4  |

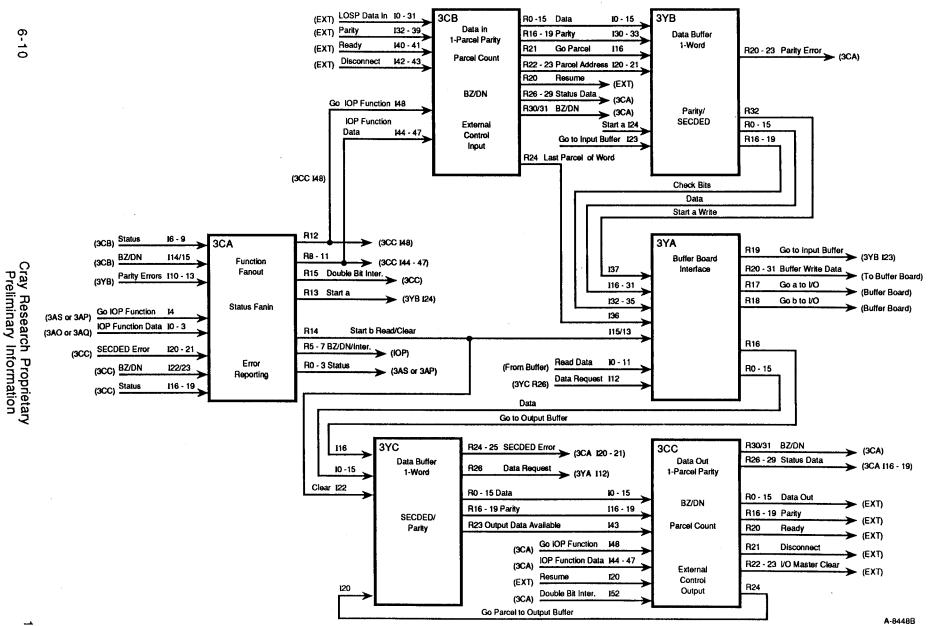

| Figure 6-5. CCA1 Block Diagram and Control               | 6-10 |

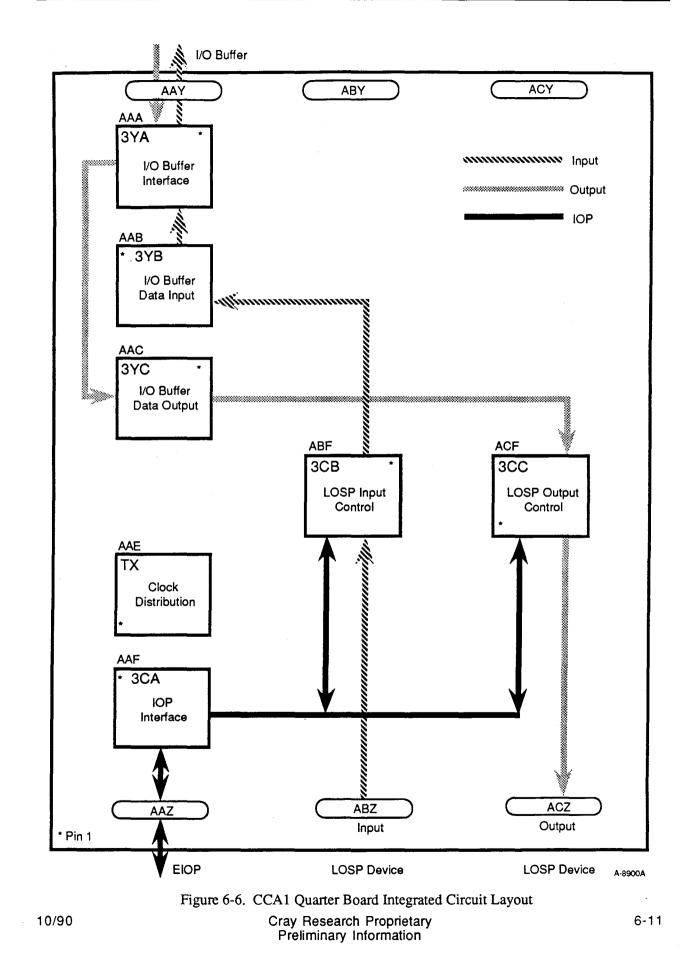

| Figure 6-6. CCA1 Quarter Board Integrated Circuit Layout | 6-11 |

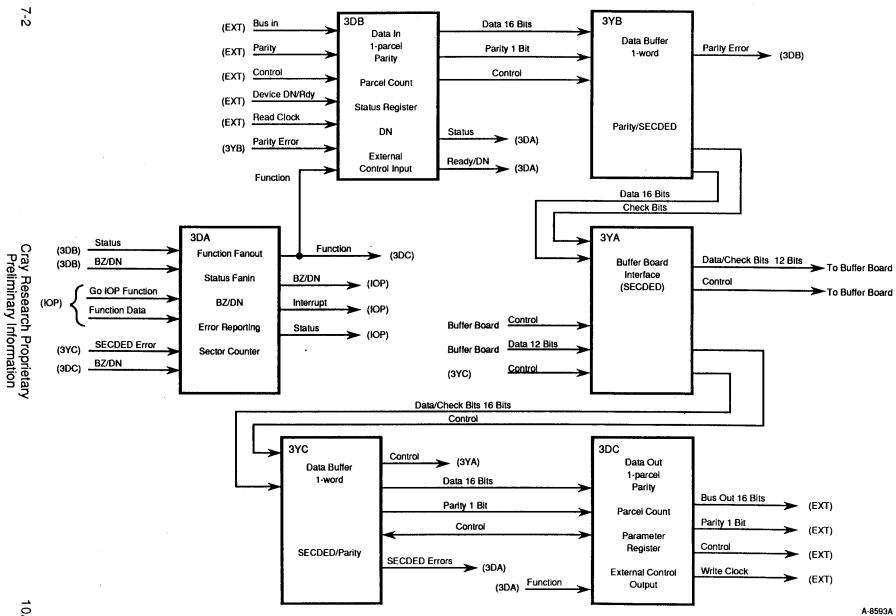

| Figure 7-1. DCA1 Block Diagram                           | 7-2  |

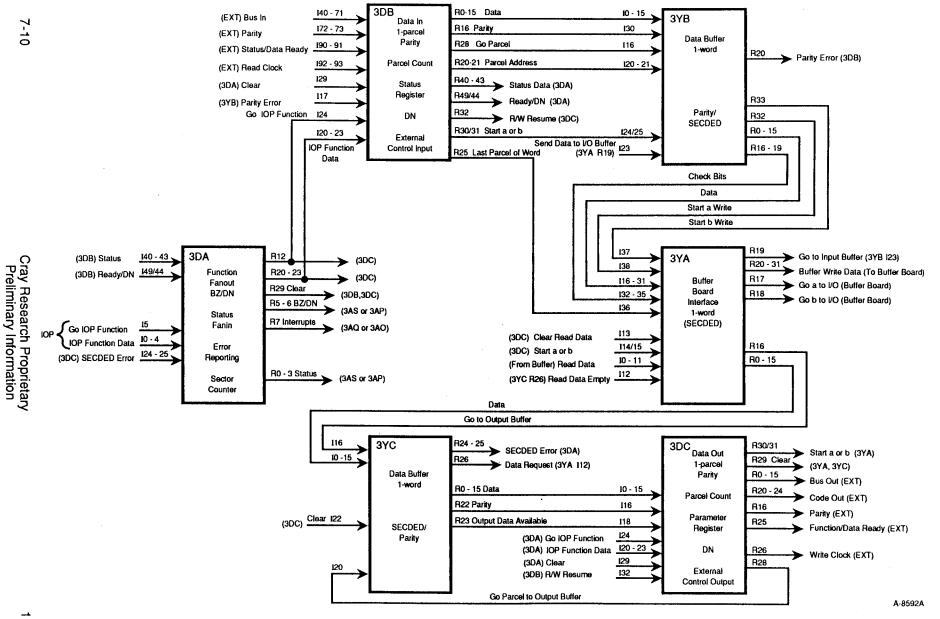

| Figure 7-2. DCA1 Block Diagram and Control               | 7-10 |

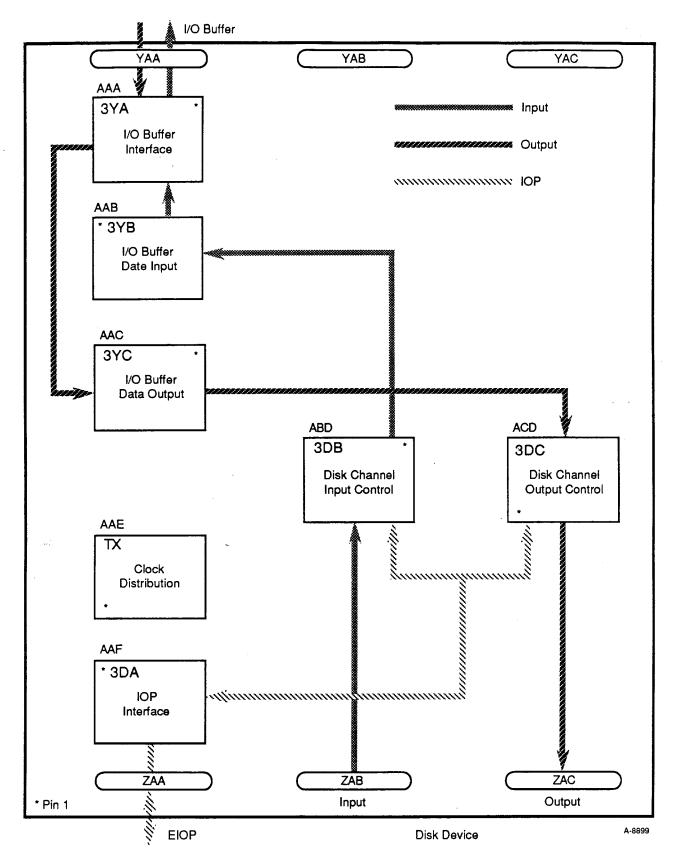

| Figure 7-3. DCA1 Quarter Board IC Layout                 | 7-11 |

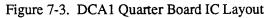

| Figure 8-1. DCA2 Block Diagram                           | 8-4  |

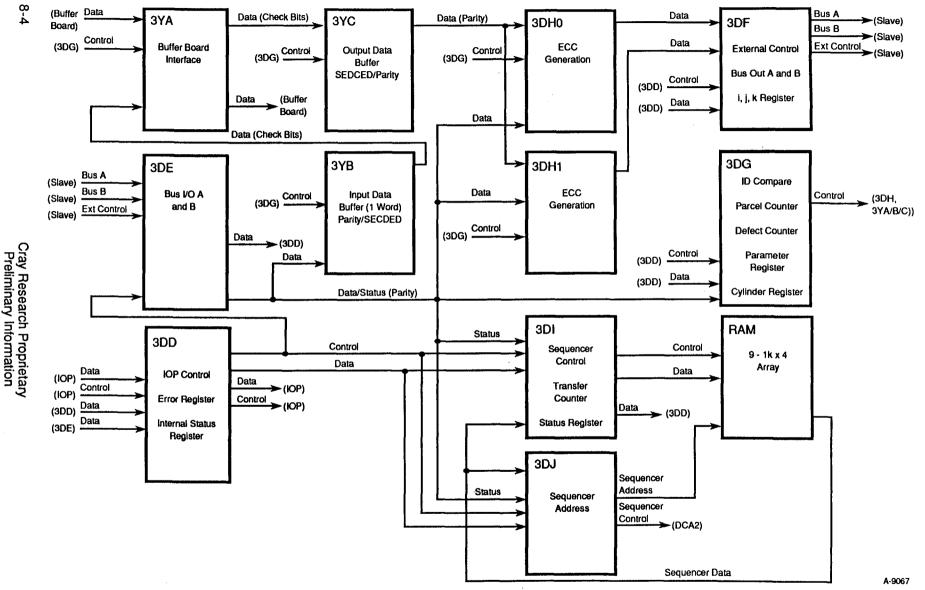

| Figure 8-2. IPI Block Diagram                            | 8-5  |

| Figure 8-3. DCA2 Block Diagram and Control Signals       | 8-21 |

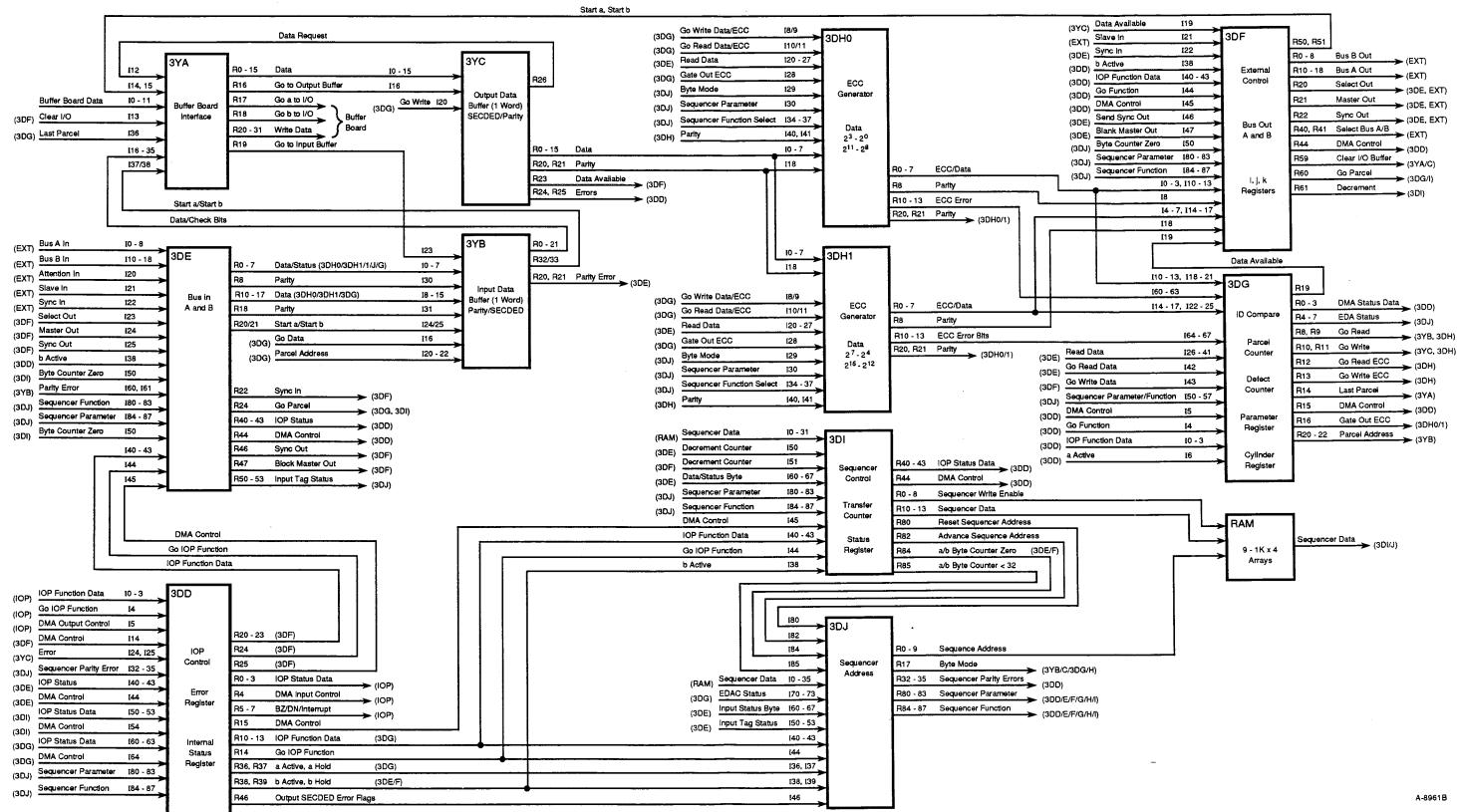

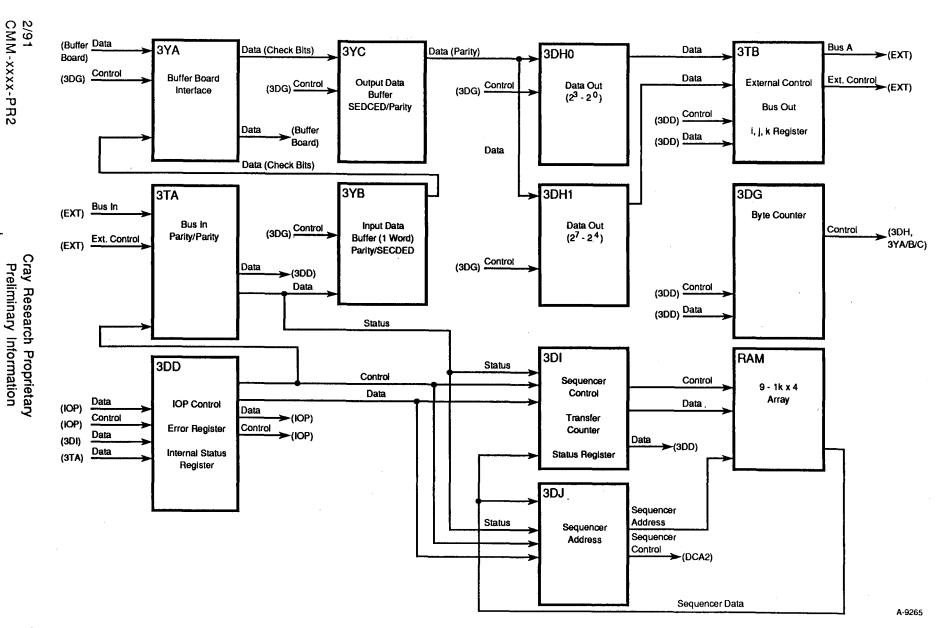

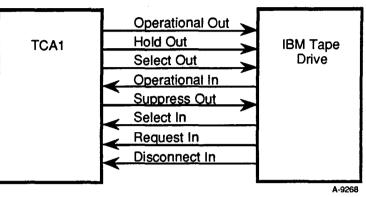

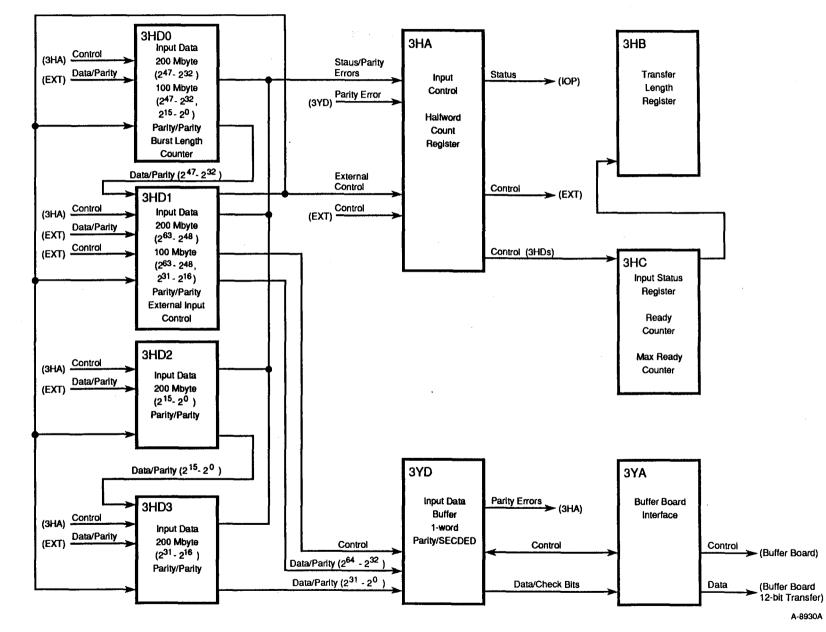

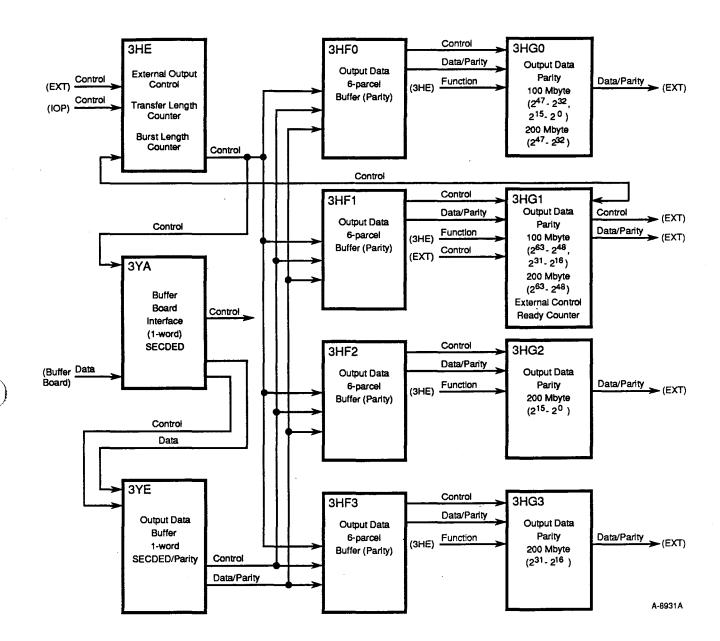

| Figure 9-1. TCA1 Block Diagram                           | 9-3  |

FIGURES (continued)

| Figure 9-2. D  | ata Bus Block Diagram                              | 9-4   |

|----------------|----------------------------------------------------|-------|

| Figure 9-3. T  | CA1 Tag Lines                                      | 9-5   |

| Figure 9-4. Se | elect Line Block Diagram                           | 9-6   |

| Figure 10-1. H | HCA3 Block Diagram                                 | 10-3  |

| Figure 10-2. H | HCA4 Block Diagram                                 | 10-5  |

| Figure 10-3. H | HIPPI Protocol                                     | 10-7  |

| Figure 10-4. I | HIPPI Control and Data Sequence                    | 10-8  |

| •              | ICA3 HIPPI Input Channel Block Diagram and Control | 10-15 |

| 0              | HCA4 Block Diagram (HIPPI Output Channel Adapter)  | 10-23 |

| Figure 10-7. H | HCA4 Quarter Board Option Layout                   | 10-25 |

| Figure 10-8. H | HCA3 Quarter Board Option Layout                   | 10-26 |

## TABLES

| Table 1-1. IOS-E Channels                                    | 1-9   |

|--------------------------------------------------------------|-------|

| Table 1-2. EIOP Channel 20, 21                               | 1-10  |

| Table 1-3. Channel Adapters                                  | 1-12  |

| Table 2-1. CPU Options and Descriptions                      | 2-1   |

| Table 2-2. Local Memory and Channel Options and Descriptions | s 2-2 |

| Table 2-3. I/O Control Options and Descriptions              | 2-2   |

| Table 2-4. Exit, Interrupt, and Return Jump                  | 2-4   |

| Table 2-5. Input and Output Control Timing                   | 2-15  |

| Table 3-1. CIN/WIN Options and Functional Descriptions       | 3-3   |

| Table 3-2. Control Signals to the IOP                        | 3-9   |

| Table 3-3. Control and Data Sync Time to the IOP for         |       |

| Channels 22 and 24                                           | 3-10  |

| Table 3-4. Output Resume                                     | 3-18  |

| Table 3-5. System, Cluster, and IOP Master Clear Fanout      | 3-29  |

| Table 4-1. Buffer Board Option Descriptions                  | 4-2   |

| Table 4-2. EIOP Read Data from the 3BD Options               | 4-15  |

Cray Research Proprietary Preliminary Information

xi

| Table 4-3. EIOP Data A and B Board Fanout from 3BM Option  | 4-21         |

|------------------------------------------------------------|--------------|

| Table 4-4. Channel Adapter Data                            | 4-25         |

| Table 4-5. Channel Adapter Data Leaving the 3BD Option     | 4-29         |

| Table 4-6. HISP Data A and B Board Fanout from 3BM Options | 4-45         |

| Table 4-7. A Side Buffer Board Chip Locator                | 4-46         |

| Table 4-8. B Side Buffer Board Chip Locator                | 4-47         |

| Table 5-1. HCM Options and Descriptions                    | 5-1          |

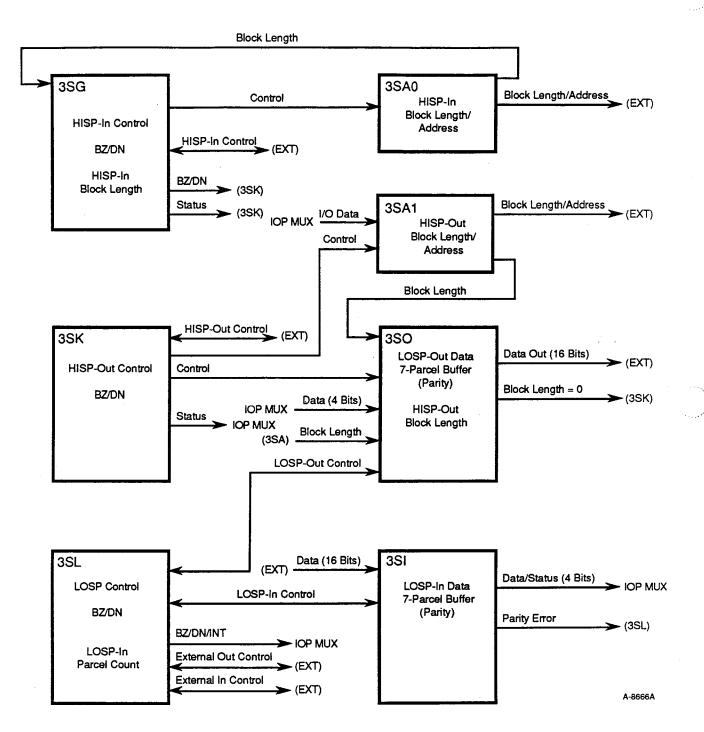

| Table 5-2. CRAY Y-MP Address/Block Length                  | <b>5</b> -11 |

| Table 5-3. Future Address/Block Length                     | 5-12         |

| Table 6-1. CCA1 Options and Functional Descriptions        | 6-1          |

| Table 7-1. DCA1 Options and Functional Descriptions        | 7-1          |

| Table 8-1. DCA2 Options and Functional Description         | 8-2          |

| Table 8-2. DCA2 Autoload Instruction                       | 8-6          |

| Table 8-3. Sequencer Data                                  | 8-7          |

| Table 8-4. DCA2 Autodump Instruction                       | 8-9          |

| Table 8-5. Go a to I/O and Go b to I/O Sync Time           | 8-15         |

| Table 9-1. TCA1 Options and Functional Description         | 9-1          |

| Table 9-2. Go a to I/O and Go b to I/O Sync Time           | 9-12         |

| Table 10-1. HCA3 Options and Functional Description        | 10-1         |

| Table 10-2. HCA4 Options and Functional Description        | 10-2         |

| Table 10-3. IOS-E and HIPPI Data Bits                      | 10-7         |

| Table 10-4.   Data and I Field Bits                        | 0-10         |

| Table 10-5. Go a To I/O and Go b To I/O Sync Time          | 0-13         |

| Table 10-6. 3HG Options Data and I Field Bits              | 0-20         |

# INTRODUCTION

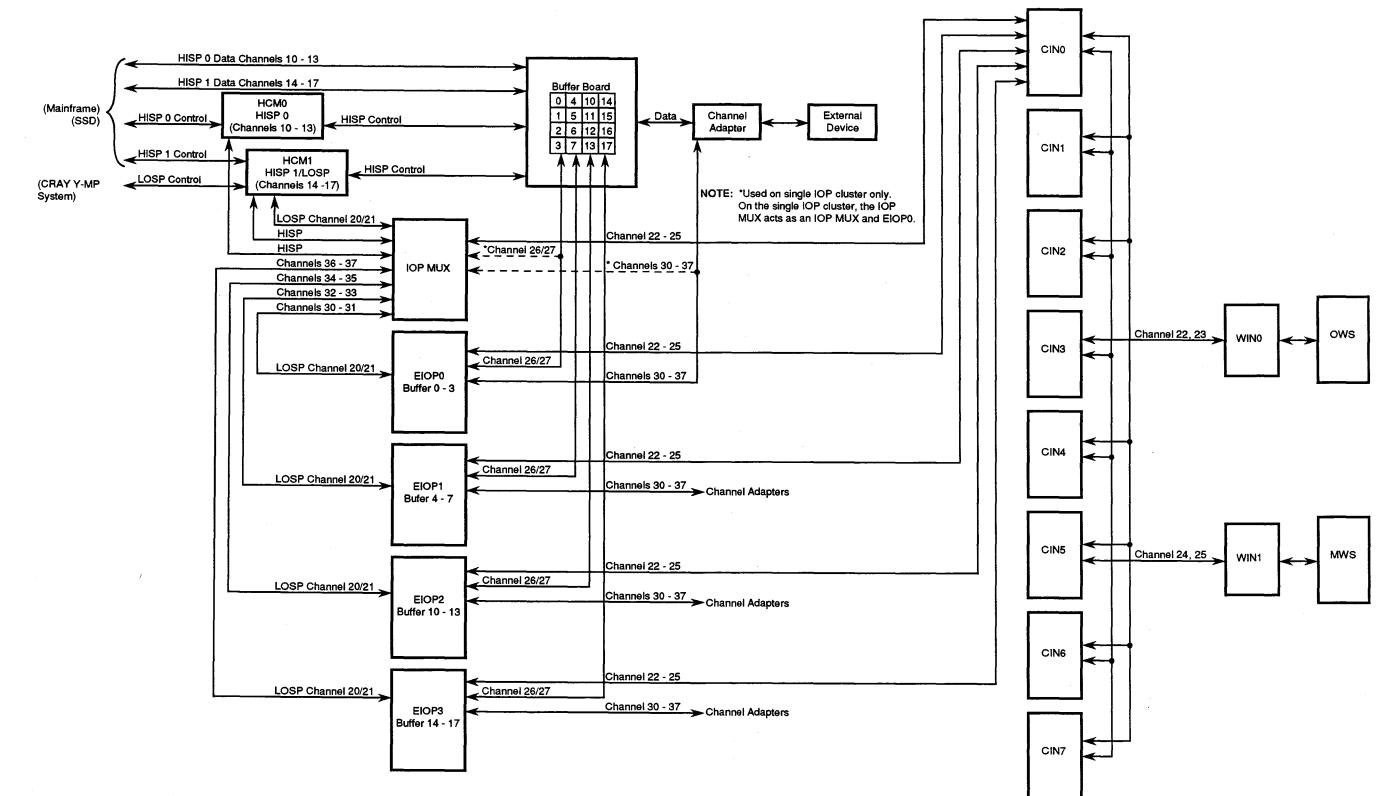

The IOS Model E is divided into clusters and operates with a 6.25 ns clock. There are a maximum of eight clusters in an IOS-E chassis or four in a CRAY Y-MP4E chassis or two in a CRAY Y-MP2E chassis. Each cluster has from one to five I/O processors (IOPs). All five IQPs are identical; they contain the same components and execute the same instruction set. However, there are two types of IOPs in each cluster, IOP MUX and the EIOPs. The only difference between the IOP MUX and the EIOPs are the devices they control. There is one IOP MUX and the EIOPs are the devices they control. There is one IOP MUX and the mainframe. There are from one to four EIOPs and they control the channel adapters that connect the I/O subsystem (IOS) to peripheral devices such as disk drives, tape drives, and communication channels. Refer to Figure 1-1 for a functional IOS-E cluster block diagram.

The IOS-E has another configuration called, a single IOP cluster. In this configuration there is only one IOP. This IOP acts as the IOP MUX and EIOPO. The single IOP controls the HISPs to the mainframe and SSD, the LOSP to the mainframe, and the peripheral devices.

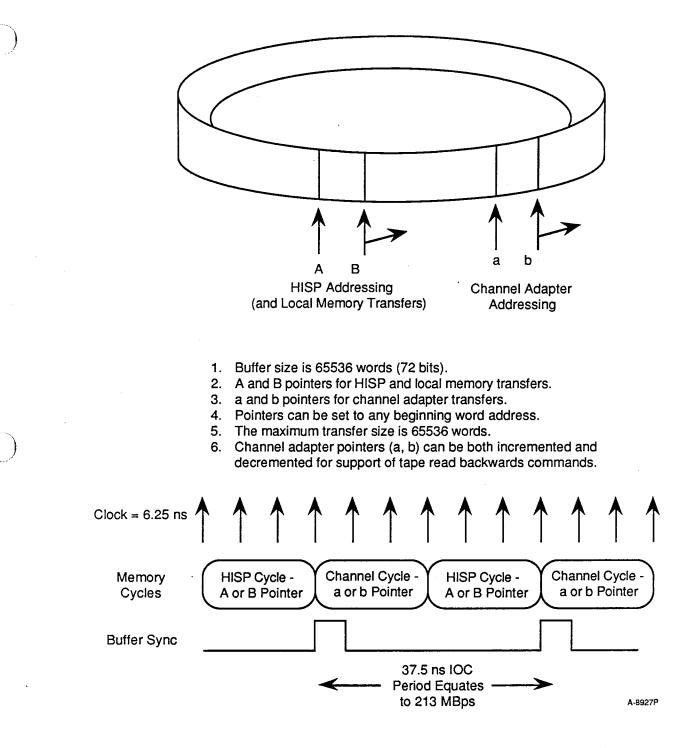

The IOS-E keeps the IOPs, channel adapters, HISPs, and LOSPs operating on the same time with the use of a sync pulse. The sync pulse is sent to all the hardware from the buffer board every 37.5 ns, which is equal to once every 6 clock periods (CPs).

The buffer board has  $20_8$  circular buffers to buffer the data between the central processing unit (CPU) and the peripheral devices. Each buffer holds 64K words. Each word is 64 bits of data and 8 check bits. The memory chips are 64K x 4 with a 18.75 ns access time. Each EIOP controls four of the buffers. The HISPs can write to and read from all buffers. Each channel adapter can write to and read from one buffer only. Each buffer has four pointers that are used to read and write the buffer: a, b, A, and B. The channel adapters use the a and b pointers. The HISP and channels 26 and 27 use the A and B pointers. The a and b pointers read and write the buffer board from sync 0 to 2. The A and B pointers read and write the buffer board from sync 3 to 5.

$\overline{)}$

Figure 1-1. Cluster Block Diagram

1-3

| АЗ<br>С    | HCM1<br>hannel 14 - 17, LOSP 20/         | (F) A2<br>21 | CIN                                  | (N)      | A1        | IOP MUX                                | (F) | <b>A</b> 0 | HCM0<br>Channel 10 - 13                | (N) |

|------------|------------------------------------------|--------------|--------------------------------------|----------|-----------|----------------------------------------|-----|------------|----------------------------------------|-----|

| B3         | EIOP3                                    | (F) B2       | EIOP2                                | (N)      | B1        | EIOP1                                  | (F) | BO         | EIOP0                                  | (N) |

|            |                                          |              |                                      | Buffer   | Мо        | dule                                   |     |            |                                        |     |

|            | BUF 12 EIOP2 34/35<br>BUF 13 EIOP2 36/37 |              | BUF 10 EIOP2 30/<br>BUF 11 EIOP2 32/ |          |           | BUF 2 EIOP0 34/35<br>BUF 3 EIOP0 36/37 |     |            | BUF 0 EIOP0 30/31<br>BUF 1 EIOP0 32/33 |     |

|            | BUF 16 EIOP3 34/35<br>BUF 17 EIOP3 36/37 |              | BUF 14 EIOP3 30/<br>BUF 15 EIOP3 32/ |          |           | BUF 6 EIOP1 34/35<br>BUF 7 EIOP1 36/37 |     |            | BUF 4 EIOP1 30/31<br>BUF 5 EIOP1 32/33 |     |

|            |                                          |              | Char                                 | nnel Ada | apte      | er Module                              |     |            |                                        |     |

| A3         | CA - 12<br>EIOP2 34/35                   | (N) A2       | 2 CA - 10<br>EIOP2 30/31             | (N)      | A1        | CA - 2<br>EIOP0 34/35                  | (N) | <b>A</b> 0 | CA - 0<br>EIOP0 30/31                  | (N) |

| B3         | CA - 13<br>EIOP2 36/37                   | (N) B2       | 2 CA - 11<br>EIOP2 32/33             | (N)      | B1        | CA - 3<br>EIOP0 36/37                  | (N) | BO         | CA - 1<br>EIOP0 32/33                  | (N) |

|            |                                          |              | Char                                 | nnel Ada | apte      | er Module                              | -   |            |                                        |     |

| A3         | CA - 17<br>EIOP3 36/37                   | (N) A2       | 2 CA - 15<br>EIOP3 32/33             | (N)      | <b>A1</b> | CA - 7<br>EIOP1 36/37                  | (N) | A0         | CA - 5<br>EIOP1 32/33                  | (N) |

| <b>B</b> 3 | CA - 16<br>EIOP3 34/35                   | (N) B2       | 2 CA - 14<br>EIOP3 30/31             | (N)      | B1        | CA - 6<br>EIOP1 34/35                  | (N) | BO         | CA - 4<br>EIOP1 30/31                  | (N) |

|            |                                          |              |                                      | Clock I  | Moo       | dule                                   |     |            |                                        |     |

| A3         | Not Used                                 | (F) A2       | 2 WIN1 (MWS)                         | (N)      | A1        | WINO (OWS)                             | (F) | A0         | Not Used                               | (N) |

|            | Clock                                    |              | Clock                                |          |           | Clock                                  |     |            | Clock                                  |     |

Cray Research Proprietary Preliminary Information

1-6

Introduction

IOS Model E Hardware Maintenance Manual

$\frown$

The operator's workstation (OWS) and the maintenance workstation (MWS) have the ability to communicate directly with all IOPs through the cluster interfaces (CIN) and workstation interfaces (WIN). There are two WINs; one is connected to the OWS and the other is connected to the MWS. Both WINs are connected to all the CINs. There are from one to eight CINs. Each cluster has its own CIN and each IOP of that cluster is connected to the CIN.

### **IOS-E Modules**

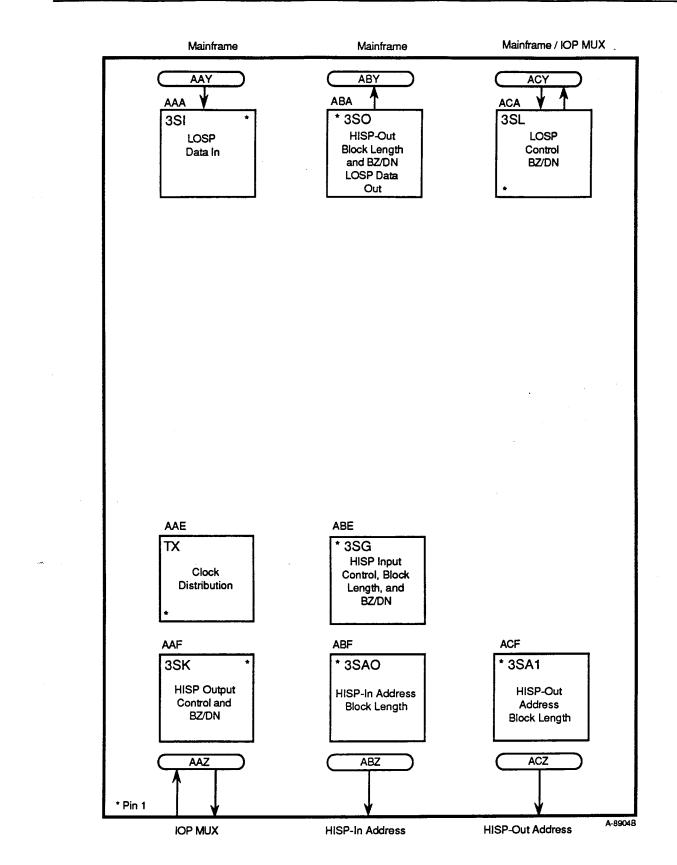

There are four modules for each cluster, plus a clock module that is shared by all clusters. The IOS-E modules can be comprised of full boards, half boards, or quarter boards. Each module has only one cold plate, so there is only an A and a B side. Refer to Figure 1-2 for a module block diagram.

The first module consists of the five IOP quarter boards, two HCM quarter boards, and one CIN quarter board. The second module is the buffer module. The buffer module has a full board on each side and is the only module that uses jumper pins to connect the A and B boards. The third module is for the channel adapters belonging to EIOP0 and 2. The fourth module is for the channel adapters belonging to EIOP1 and 3. The channel adapters can be full, half, or quarter boards. The clock module has two WIN quarter boards on the A side and a full clock board on the B side. A dummy quarter board is used when there is no quarter board needed. The dummy board has a burn foil on it.

### I/O Processor

Each IOP is a 16-bit (1-parcel) computer designed to control data transfers in and out of the IOS. Each IOP executes a set of 128 instructions. Refer to Section 7, "I/O Processor Instruction Set," of the IOS Model E System Programmer Reference Manual (CSM-xxxx-PR1) for detailed information about each instruction.

Each IOP contains four major sections: control section, computation section, local memory section, and the I/O section. Refer to Section 2, "I/O Processor," of the IOS Model E System Programmer Reference Manual (CSM-xxxx-PR1) for detailed information about the IOP.

The control section fetches and decodes instructions, and controls branches, interrupts, and subroutine calls and returns. Its major components are the instruction stack, program address (P) register, next instruction parcel (NIP) register, current instruction parcel (CIP) register, exit stack, and real-time clock (RTC).

The computation section provides temporary data storage and performs logical, arithmetic, and shift operations. Its major components are the accumulator, add and shift functional units, operand registers, B register, and base register.

The local memory section contains 64K parcels of random access memory (RAM) which is protected with single-error correction/double-error detection (SECDED) logic on each parcel of data. Local memory has two direct memory access (DMA) ports. These DMA ports are shared by the channel adapters, HISP channels, LOSP channels, and the buffer board channel to read and write local memory.

The I/O section controls the 29 I/O channels.

IOS Model E Hardware Maintenance Manual

Introduction

# I/O Channels

The I/O has 29 I/O channels: 5 internal channels and 24 external channels. Refer to Table 1-1 for the I/O channel assignments and Figure 1-1 for a channel block diagram.

| Channel<br>Number | IOP MUX<br>Type    | DMA<br>Port | EIOPs<br>Type      | DMA<br>Port | Single IOP Clus<br>Type | ster<br>DMA<br>Port |

|-------------------|--------------------|-------------|--------------------|-------------|-------------------------|---------------------|

| 0                 | I/O request        | N/A         | I/O request        | N/A         | I/O request             | N/A                 |

| .2                | Program exit stack | N/A         | Program exit stack | N/A         | Program exit stack      | N/A                 |

| 3                 | Local memory error | N/A         | Local memory error | N/A         | Local memory error      | N/A                 |

| 4                 | RTC                | N/A         | RTC                | N/A         | RTC                     | N/A                 |

| 7                 | Base register      | N/A         | Base register      | N/A         | Base register           | N/A                 |

| 10 and 12         | HISP 0 input       | 0           | Not used           |             | HISP 0 input            | 0                   |

| 11 and 13         | HISP 0 output      | 0           | Not used           | •           | HISP 0 output           | 0                   |

| 14 and 16         | HISP 1 input       | 1           | Not used           |             | HISP 1 input            | 1                   |

| 15 and 17         | HISP 1 output      | 1           | Not used           |             | HISP 1 output           | 1                   |

| 20 and 21         | LOSP CPU           | 0           | MIOP               | 0           | LOSP CPU                | 0                   |

| 22 and 23         | ows                | 1           | ows                | 1           | ows                     | 1                   |

| 24 and 25         | MWS                | 1           | MWS                | 1           | MWS                     | 1                   |

| 26 and 27         | Not used           |             | Buffer board       | 0           | Buffer board            | 0                   |

| 30 and 31         | EIOP0 20, 21       | 0           | Channel adapter 0  | 0           | Channel adapter 0       | 0                   |

| 32 and 33         | EIOP1 20, 21       | 1           | Channel adapter 1  | 1           | Channel adapter 1       | 1                   |

| 34 and 35         | EIOP2 20, 21       | 0           | Channel adapter 2  | 0           | Channel adapter 2       | 0                   |

| 36 and 37         | EIOP3 20, 21       | 1           | Channel adapter 3  | 1           | Channel adapter 3       | 1                   |

| Table 1-1. IOS-E Channels | Table | 1-1. | IOS-E | Channels |

|---------------------------|-------|------|-------|----------|

|---------------------------|-------|------|-------|----------|

2/91 CMM-xxxx-PR2 Cray Research Proprietary Preliminary Information 1-9

## Channels 10 through 17

Channels 10 through 17 are HISP channels and are used by the IOP MUX. There are two sets of HISP channels: 10 through 13 and 14 through 17. There are two logical channels used for the input 10 and 12, but there is only one physical channel. There are two logical channels used for the output 11 and 13, but there is only one physical channel. The logical channels share hardware and drop cables. The logical channels stack transfers. One of the logical channels is activated and then the other channel is allowed to be programmed and activated, but if the first channel is busy the second channel must wait. The second channel is allowed to go busy when the first logical channel's done flag sets. This is true for channels 14 through 17 also. Refer to Section 4, "Low-speed and High-speed Channels," of the IOS Model E System Programmer Reference Guide (CSM-xxxx-PR1) for more information on HISP data transfers.

### Channels 20 and 21

Channels 20 and 21 perform different functions in the IOP MUX and EIOPs. In the IOP MUX channels 20 and 21 are connected to the CPUs LOSP channels. They are used to deadstart the CPU and to exchange packets of information. In the EIOPs, channels 20 and 21 are connected to 30 through 37 of the IOP MUX. The EIOPs and the IOP MUX exchange information packets on these channels. Refer to Table 1-2 for channel configuration. Refer to Section 4, "Low-speed and High-speed Channels," of the IOS Model E System Programmer Reference Guide (CSM-xxxx-PR1) for more information on LOSP data transfers.

| EIOP | EIOP Channel | IOP MUX Channel |

|------|--------------|-----------------|

| 0    | 20, 21       | 30, 31          |

| 1    | 20, 21       | 32, 33          |

| 2    | 20, 21       | 34, 35          |

| 3    | 20, 21       | 36, 37          |

| Table 1-2. EIOP Channel 20, 2 | 21 |  |

|-------------------------------|----|--|

|-------------------------------|----|--|

#### Channels 22 through 25

Channels 22 through 25 in each IOP transfer data between the IOP and the workstations. Channels 22 and 23 are connected to the OWS and channels 24 and 25 are connected to the MWS. Data can be transferred across these channels under control of either the IOP or the workstation. Refer to Section 6, "Cluster Interface/Workstation Interface," of the IOS Model E System Programmer Reference Guide (CSM-xxxx-PR1) for more information on workstation data transfers.

### Channels 26 and 27

Channels 26 and 27 are used only by the EIOPs. These channels transfer data between local memory and the I/O buffer and program the transfers between the I/O buffer and the channel adapters. Refer to Section 3, "I/O Buffer," of the IOS Model E System Programmer Reference Guide (CSM-xxxx-PR1) for more information on I/O buffer data transfers.

#### Channels 30 through 37

Channels 30 through 37 perform different functions in the IOP MUX than they do in the EIOPs. In the EIOPs, these channels transfer data between local memory and the channel adapters, and they program transfers between the channel adapters and the I/O buffer. Refer to Section 5, "Channel Adapters," of the IOS Model E System Programmer Reference Guide (CSM-xxxx-PR1) for more information on channel adapter data transfers.

Channels 30 through 37 in the IOP MUX transfer data between IOP MUX and EIOP local memory. Channels 30 through 37 are connected to channels 20 and 21 of each EIOP. Refer to Table 1-2 for a channel configuration.

## **Channel Adapters**

Each EIOP can be connected to four channel adapters. They are channels 30 through 37. The channels work in pairs to communicate with the peripheral devices: 30/31, 32/33, 34/35, and 36/37. The channel adapters control the transfer of data between the peripheral device and the buffer board. Refer to Table 1-3 and to the individual sections in this manual for more information on the channel adapters.

2/91 CMM-xxxx-PR2

| Name | Туре        | Channel      | Comment                                                                                                           |

|------|-------------|--------------|-------------------------------------------------------------------------------------------------------------------|

| CCA1 | LOSP        | 30 - 37      | Even channel is input<br>Odd channel is output<br>FEls, NSC, and Front ends<br>Quarter board                      |

| DCA1 | Disk drives | 30 - 37      | Both channels are input and output<br>DD-39s, DD-49s, DD-40s, DD-41s,<br>and DD-50s<br>Quarter board              |

| DCA2 | Disk drives | 30 - 37      | Both channels are input and output<br>IPI 9 head (DD-60s) or single head<br>(DD-61s) disk drives<br>Quarter board |

| DCA3 | Disk drives | 30 - 37      | Both channels are input and output<br>9 IPI in drive in parallel<br>Full board                                    |

| TCA1 | Tape drives | 30 - 37      | Both channels are input and output<br>IBM type tape drives<br>Quarter board                                       |

| TCA2 | Tape drives | 30 - 37      | Both channels are input and output<br>IPI type tape drives<br>Quarter board                                       |

| НСАЗ | HIPPI in    | 30/31, 34/35 | All channels are input<br>Quarter board                                                                           |

| HCA4 | HIPPI out   | 32/33, 36/37 | All channels are output<br>Quarter board                                                                          |

| HCA5 | IPI bus     | 30 - 37      | Both channels are input and output<br>IPI protocol<br>Half board                                                  |

Table 1-3. Channel Adapters

Pag.

I

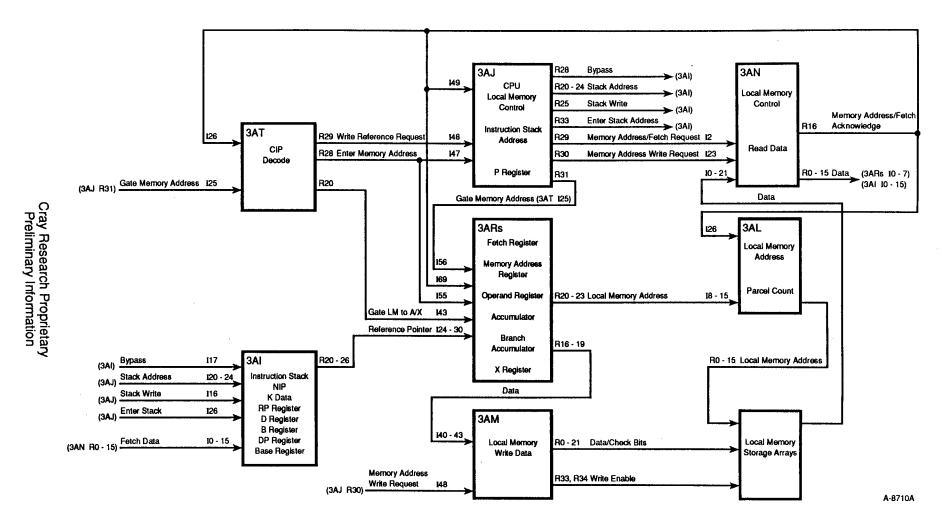

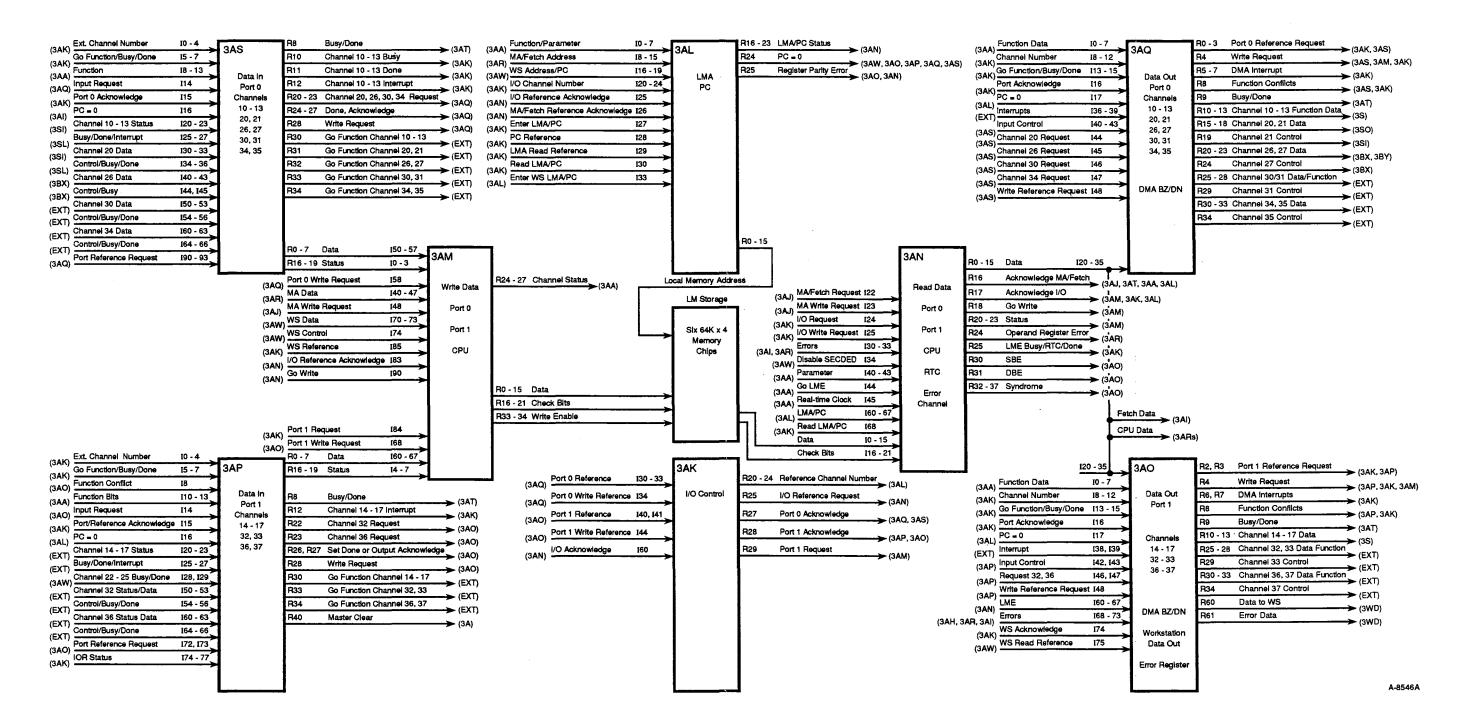

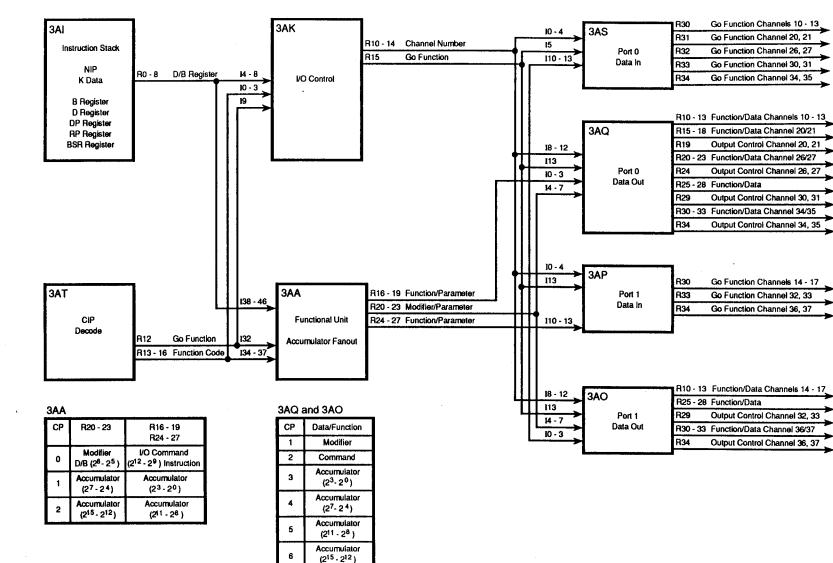

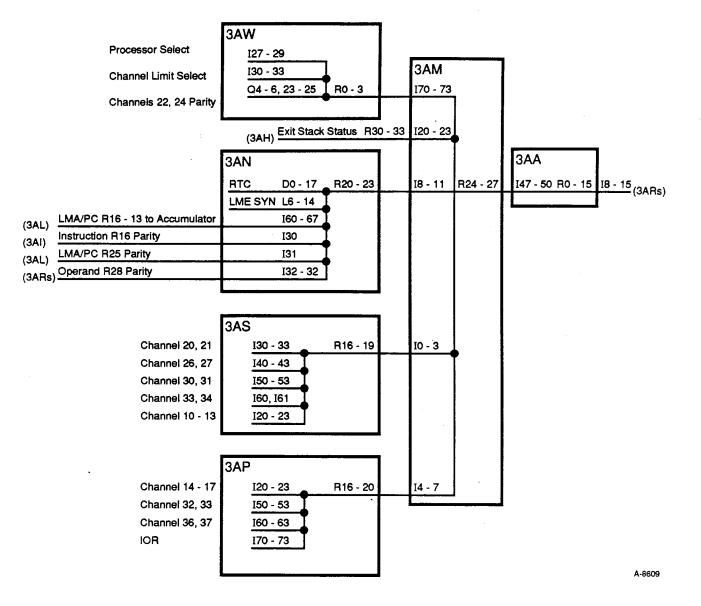

The CPU options consist of the 3AA, 3AH, 3AI, 3AJ, 3ARs, and 3AT, which are described in Table 2-1. The local memory and channel options are 3AL, 3AM, 3AN, 3AO, 3AP, 3AQ, and 3AS, and six 64K x 4-bit memory arrays which are described in Table 2-2. The 3AK and 3AW options provide I/O control for the channels and workstation and are described in Table 2-3. Refer to Figure 2-1 for functional block diagram of CPU. Refer to Figure 2-12 for IOP quarter board option layout.

Table 2-1. CPU Options and Descriptions

| Option       | Functional Description                                                                                                                                                             |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ЗАА          | Functional units, accumulator fanin/fanout                                                                                                                                         |

| ЗАН          | 32-parcel exit stack                                                                                                                                                               |

| ЗАІ          | Instruction stack, next instruction parcel (NIP), k data,<br>D/B/RP/DP register, base register (BSR)                                                                               |

| ЗАJ          | CPU local memory control, P register, branch control, and the instruction stack address                                                                                            |

| 3AR<br>(two) | 128-operand register, MA/fetch registers, accumulator,<br>branch accumulator, X register<br>3AR0 bits 2 <sup>7</sup> - 2 <sup>0</sup> , 3AR1 bits 2 <sup>15</sup> - 2 <sup>8</sup> |

| ЗАТ          | Current instruction parcel (CIP), decode, and the carry bit                                                                                                                        |

| Option | Functional Description                                                                                                                             |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| 3AL    | Local memory address and parcel counter registers                                                                                                  |

| ЗАМ    | Write data in – port 0, port 1, workstation, and CPU<br>I/O fanin                                                                                  |

| 3AN    | Read data out – port 0, port 1, workstation, and CPU real-time clock (RTC)                                                                         |

| ЗАО    | Data out port 1 – channels 14 - 17, 32 - 33 and 36 - 37<br>Workstation data out<br>Error logger<br>Direct memory access busy and done flags port 1 |

| ЗАР    | Data in port 1 – channels 14 - 17, 32 - 33 and 36 - 37                                                                                             |

| ЗAQ    | Data out port 0 – channels 10 - 13, 20 - 21, 26 - 27,<br>30 - 31, and 34 - 35<br>Direct memory access (DMA) busy and done flags<br>port 0          |

| 3AS    | Data in port 0 – channels 10 - 13, 20 - 21, 26 - 27,<br>30 - 31, and 34 - 35                                                                       |

| Table 2-2. Local Memory and Channel Options and Descriptions |

|--------------------------------------------------------------|

|--------------------------------------------------------------|

Table 2-3. I/O Control Options and Descriptions

| Option | Functional Description              |  |  |

|--------|-------------------------------------|--|--|

| ЗАК    | I/O control                         |  |  |

| ЗАW    | Workstation control channel 22 - 25 |  |  |

à

10/90

Cray Research Proprietary Preliminary Information 2-3

## **CPU** Control Signals

The CPU control is provided by the 3AT, 3AJ, 3AK, and 3AR options. An explanation of each control signal is provided. For a functional block diagram of the CPU control signals, refer to Figure 2-2.

### **3AT Control Signals**

The 3AT decodes the instruction and then outputs the appropriate control signals. The following is an explanation of the 3AT options control signals. For a functional block diagram of the 3AT options control signals, refer to Figure 2-2.

- Advance P Branch (R0) is sent to the 3AJ to advance (+1) the P register after a branch is decoded. It is sent twice for a 2-parcel branch.

- Advance S, P (R1) increments the instruction stack read address and the P register on the 3AJ after an instruction issue. On the 3AI, it advances the next instruction into the next instruction parcel (NIP). It is not sent if a branch is issued.

- Exit or Interrupt or Call (R3 4) work together to read or write the exit stack and load the P register. After an exit instruction (001) has been decoded, the 3AH reads out the exit stack to the P register and then decrements the exit stack pointer (EP). The P register then sends the address to the fetch registers. After a return jump issues, the 3AH increments the EP and then writes the P register into the exit stack. After an interrupt is received, the 3AH increments the EP and writes the P register into the exit stack location 0 to the P and fetch registers. Refer to Table 2-4 for the proper levels of R3 and R4 during an exit, return jump, and interrupt.

| Table 2-4. | Exit, | Interrupt, | and | Return | Jump |

|------------|-------|------------|-----|--------|------|

|------------|-------|------------|-----|--------|------|

| R4 | R3 | Comment     |

|----|----|-------------|

| 0  | 1  | Exit (001)  |

| 1  | 0  | Return jump |

| 1  | 1  | Interrupts  |

- Enter B Register (R5) loads the accumulator into the B register.

- DP to RP (R6) loads the destination pointer (DP) into the reference pointer (RP). The DP to RP signal is sent for instructions that read and write operand registers. It is sent prior to the writing of the operand registers.

- Enter P from Adder (R7) loads the P register with the functional unit value (branch address) after a branch instruction.

- d Branch or +d Branch (R8 or R9) if set, informs the 3AJ that a relative branch has issued and is sent with Go Branch (R17). If R8 is set, it is a backward jump and if R9 is set, it is a forward jump. The 3AJ determines if it is an in-stack branch by comparing the offset (D field). If it is an in-stack branch, the instruction stack read address is offset by the value of the D field. If it is an out of stack branch, the instruction stack read and write addresses are cleared. Whether it is an in-stack or out-of-stack branch, the P register is loaded with the functional unit value.

- Enter DP Register (R10) loads the reference pointer into the DP register on the 3AI. The Enter DP signal is sent for instructions that read and write the operand registers. It is sent prior to the reading of the operand registers.

- Go Read Busy/Done (R11) is sent to the 3AK after a 040 043 instruction has issued. It informs the 3AK to read the busy or done flag of the requested channel (I4 8) to the carry bit (3AT).

- Go Function I/O (R12) signals the 3AA and 3AK that a 140 177 instruction has issued.

- Function Code 2<sup>0</sup> 2<sup>3</sup> (R13 16) are bits 2<sup>12</sup> 2<sup>9</sup> of the instruction if sent with Go Function I/O (R12). If sent with Go Read Busy/Done (R11), bit 2<sup>0</sup> differentiates between the busy and the done flag. The Function Code is also used to inform the 3AA of a functional unit operation.

- Go Branch (R17) is sent to the 3AJ when a branch is decoded. If R8 or R9 is set, it is a relative branch. If neither R8 or R9 is set, it is an absolute branch.

- Clear Accumulator (R18) clears the accumulator prior to the loading of the accumulator.

- Gate Local Memory to A/X (R20) is sent to the 3ARs to load the local memory data into the accumulator or the X register. If R24 is set, the data is loaded into the X register.

- Enter Constant (R21) sets bit 2<sup>0</sup> of the X register on 3AR0 after an increment or decrement instruction has been decoded.

- Gate d/b/k to a/x (R23) loads the D, B, or K register into the accumulator or X register. If R24 is set, the data is loaded into the X register.

- Steer to X (R24) is sent with R19, R20, and R23 if the X register is to be loaded instead of the accumulator.

- Gate Register to Branch (R25) loads the operand register value into the branch accumulator on the 3AR options. The Gate Register to Branch signal is sent for branch instructions that use an operand register value for the displacement value.

- Enter P to Branch A (R26) loads the P register (I60 67) into the branch accumulator on the 3AR after the 3AT decodes a branch instruction.

- Enter AA Data (R27) loads the functional unit value into the accumulator.

- Enter Memory Address (MA) (R28) is sent to the 3AJ requesting a local memory reference. It latches the operand register value into the memory address register on the 3ARs.

- Local Memory Write Reference (R29) is sent to the 3AJ when the 3AT decodes a CPU write (034). It is sent with Enter MA (R28).

- Write Register (R30) enables a write to the operand registers on the 3ARs.

### **3AJ Control Signals**

The 3AJ controls the CPU local memory references, the instruction stack read and write addresses, and the P register. The following is an explanation of the 3AJ options control signals. For a functional block diagram of the 3AJ options control signals, refer to Figure 2-2.

• Instruction Stack Write (R25) is sent to the 3AI after the 3AJ has completed the fetch sequence. It writes the fetched parcel into the instruction stack.

Cray Research Proprietary Preliminary Information 10/90

- Instruction Stack Write (R25) is sent to the 3AI after the 3AJ has completed the fetch sequence. It writes the fetched parcel into the instruction stack.

- Enter NIP (R26) is sent after Input to NIP Valid sets and NIP is not valid. It allows the 3AI to load the NIP without an Advance S. The 3AT receives Enter NIP and sets NIP Valid on the 3AT.

- Input to NIP Valid (R27) means the instruction stack address is a valid read address or the bypass is valid. If the instruction stack is being written to and the load pointer is equal to the stack pointer, the input to NIP valid is cleared. The 3AI loads the NIP when it receives an Advance S or Enter NIP, and the input to NIP valid is set. The 3AT uses Input to NIP Valid and Advance S to keep NIP Valid on the 3AT.

- Bypass Stack (R28) is sent to the 3AI when the load pointer is equal to the stack pointer and NIP is not valid. The instruction is loaded directly into the NIP and written into the instruction stack.

- MA/Fetch Request (R29) is sent to the 3AN if there is a CPU read, write, or fetch request for local memory.

- Write Request (R30) is sent with MA/Fetch Request (R29) if the reference is a CPU write (034).

- Gate MA (R31) gates the accumulator data to the 3AM, selects the MA register on the 3ARs, and informs the 3AT that the operand registers and accumulator are free on CPU write and that the operand registers are free on CPU read.

- Enter Fetch Pointer (R32) loads the P register address into the fetch register on the 3ARs after an out-of-stack branch has issued or an interrupt has been received. The exit stack value or functional unit value is loaded into P register. The P register then loads the fetch register.

- Enter Instruction Stack Address (R33) latches the instruction stack address onto the 3AI.

- NIP Valid (R34) is sent to the 3AT when the NIP has valid data. If NIP Valid is set and an Advance S is received, the 3AT sets or holds CIP valid on the 3AT.

# **3AK Control Signals**

The 3AK provides I/O control. The following is an explanation of the 3AK options control signals. For a functional block diagram of the 3AK options control signals, refer to Figure 2-2.

- Go Function (R15) is sent from the 3AK to the I/O channel options after a channel function is decoded.

- Channel Designator (R10 14) are bits 2<sup>4</sup> 2<sup>0</sup> of the B or D registers and are only used on the IOP board. The channel designators are sent with Go Function (R15) or Go Busy/Done(R17/18).

- Go Busy/Done (R17/18) fans in the busy or done flag of the requested channel.

- Enter LMA/PC(R31/32) enters the local memory address (LMA) and parcel on the 3AL.

### **3AR Control Signals**

The following is an explanation of the 3ARs options control signals. For a functional block diagram of the 3AR options control signals, refer to Figure 2-2.

- A = 0 (R25) is sent from 3ARs to the 3AT and is used for conditional jumps.

- Fetch Pointer Carry (R27) is sent from 3AR0 to 3AR1 when the fetch address bits 2<sup>7</sup> 2<sup>0</sup> has a carry for bits 2<sup>15</sup> 2<sup>8</sup>. The 3AR0 has bits 2<sup>7</sup> 2<sup>0</sup> and 3AR1 has bits 2<sup>15</sup> 2<sup>8</sup>.

Cray Research Proprietary Preliminary Information

10/90

# **CPU Local Memory References**

There are three types of CPU local memory references: write, read, and fetch. The following is a sequential explanation of each reference. For a functional block diagram of the CPU references, refer to Figure 2-3.

## **CPU Local Memory Write Reference Sequence**

The following is a sequential explanation of a CPU write reference. For a functional block diagram of the CPU write reference, refer to Figure 2-3.

- 1. Enter MA and Write Reference Request. When the 3AT decodes a central processing unit (CPU) Write (034), it sends an Enter MA to the 3AJ and 3ARs and a Write Reference Request to the 3AJ.

- 3AJ The Enter MA (I47) informs the 3AJ that the CPU is requesting a local memory reference and if Write Reference Request (I48) is set, it is a write request.

- 3AI The 3AI pre-decodes the NIP (2<sup>15</sup> 2<sup>9</sup>) to see if the B or D register is loaded into RP (R20 26).