#### Title: 60 Series Disk Systems Guide

#### Number: COM-1124-0B0

Your feedback on this publication will help us provide better documentation in the future. Please take a moment to answer the few questions below.

For what purpose did you primarily use this manual?

| <u></u> | _Troubleshooting          |

|---------|---------------------------|

|         | _Tutorial or introduction |

|         | _Reference information    |

|         | _Classroom use            |

|         | Other - please explain    |

Using a scale from 1 (poor) to 10 (excellent), please rate this manual on the following criteria and explain your ratings:

| Accuracy                                            |  |

|-----------------------------------------------------|--|

| Organization                                        |  |

| Readability                                         |  |

| Physical qualities (binding, printing, page layout) |  |

| Amount of diagrams and photos                       |  |

| Quality of diagrams and photos                      |  |

| Completeness (Check one)                            |  |

| Too much information                                |  |

| Too little information                              |  |

| Just the right amount of information                |  |

Your comments help Hardware Publications and Training improve the quality and usefulness of your publications. Please use the space provided below to share your comments with us. When possible, please give specific page and paragraph references. We will respond to your comments in writing within 48 hours.

| NAME    |   |         | ···· | · |   |

|---------|---|---------|------|---|---|

|         |   |         |      |   |   |

|         |   |         |      |   | C |

| ADDRESS |   | <u></u> |      |   |   |

| CITY    | s | TATE    | ZIP  |   |   |

| DATE    |   |         |      |   |   |

|         | F |         | 1    |   |   |

[or attach your business card]

CUT ALONG THIS LINE

STAPLE

# **Record of Revision**

Each time this manual is updated with a change packet, a change to part of a text page is indicated by a change bar in the margin directly opposite the change. A change bar in the footer of a text page indicates that most, if not all, of the text is new. A change bar in the footer of a page composed primarily of a table and/or figure may indicate that a change was made to that table/figure or, it could indicate that the entire table/figure is new. Change packets are assigned a numerical designator, which is indicated in the publication number on each page of the change packet.

Each time this manual is fully revised and reprinted, all change packets to the previous version are incorporated into the new version, and the new version is assigned an alphabetical revision level, which is indicated in the publication number on each page of the manual. A revised manual does not usually contain change bars.

## REVISION DESCRIPTION

Α

В

\_\_\_\_

July 1991. Original Printing.

- November 1992. The manual was reorganized with information on the DD-62, RD-62, and RDE-6 added. Miscellaneous editorial and technical changes were made.

- February 1993. Information about the disk array product and DCA-3 channel adapter was added. Miscellaneous editorial and technical changes were made.

## PREFACE

The 60 Series Disk Systems Guide is designed as a reference manual for Cray Research, Inc. (CRI) field engineers who have had I/O subsystem model E (IOS-E) and 60 series disk systems training. This manual incorporates diagnostic and hardware information relative to disk drive operations.

The following conventions are used throughout this manual:

- Courier font indicates directory pathnames, filenames, commands, utilities, and screen output.

- **Courier bold** font indicates commands and options that the user should enter.

- Italic font indicates a variable or user-supplied entry.

- Commands must be entered as shown in the command syntax. Spaces must be included or left out as shown; do not use tabs.

- The  $\leftarrow$  symbol indicates pressing the return key.

- Control signals for the IPI-2 interface are in capital letters. For example, BUS CONTROL.

If you have any criticisms, comments, or suggestions related to this manual, please fill out a reader comment form and send it back to Hardware Publications and Training. Reader comment forms are located in the front and back of this manual.

# CONTENTS

)

#### **1 DISK SYSTEM OVERVIEW**

| Disk Drives                               | 1-2  |

|-------------------------------------------|------|

| DD-60 Disk Drive                          | 1-2  |

| DD-61 Disk Drive                          | 1-2  |

| DD-62 Disk Drive                          | 1-3  |

| RD-62 Disk Drive                          | 1-3  |

| DD-60, DD-61, DD-62, and RD-62 Comparison | 1-4  |

| DE-60 Disk Enclosure                      | 1-5  |

| RDE-6 Disk Enclosure                      | 1-7  |

| Spare Disk Drive                          | 1-8  |

| DCA-2 Disk Channel Adapter                | 1-9  |

| DCA-3 Disk Channel Adapter                | 1-10 |

| DCA-2 and DCA-3 Comparison                | 1-11 |

|                                           |      |

#### 2 DCA-2 TO DISK DRIVE CABLING

| Cabling Hardware             | 2-1  |

|------------------------------|------|

| Daisy Chain Cables           | 2-2  |

| Initial Daisy Chain Cable    | 2-2  |

| 2X Daisy Chain Cable         | 2-2  |

| IOS-E Bulkhead Connectors    | 2-3  |

| DCA-2 to Disk Drive Cables   | 2-5  |

| Daisy Chain Cable            | 2-7  |

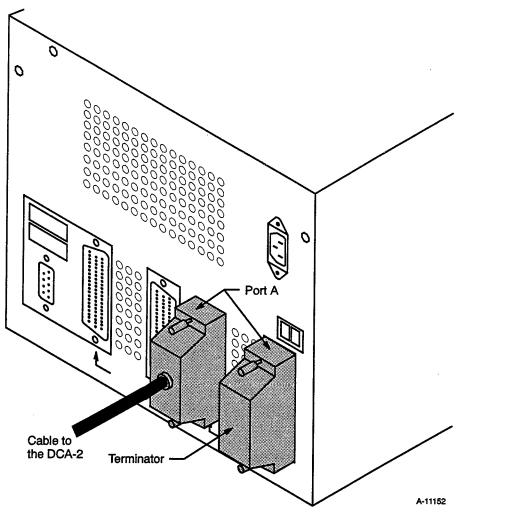

| Terminator                   | 2-9  |

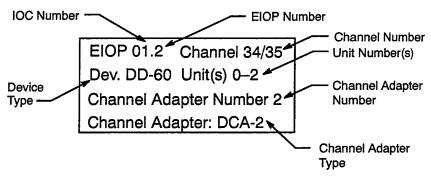

| Cable Labels                 | 2-10 |

| Configurations               | 2-10 |

| Single-port Configuration    | 2-11 |

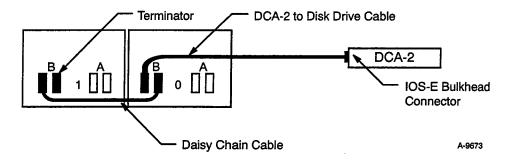

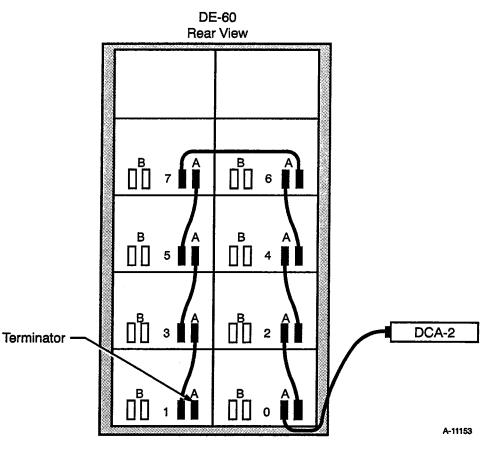

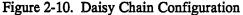

| Daisy Chain Configuration    | 2-13 |

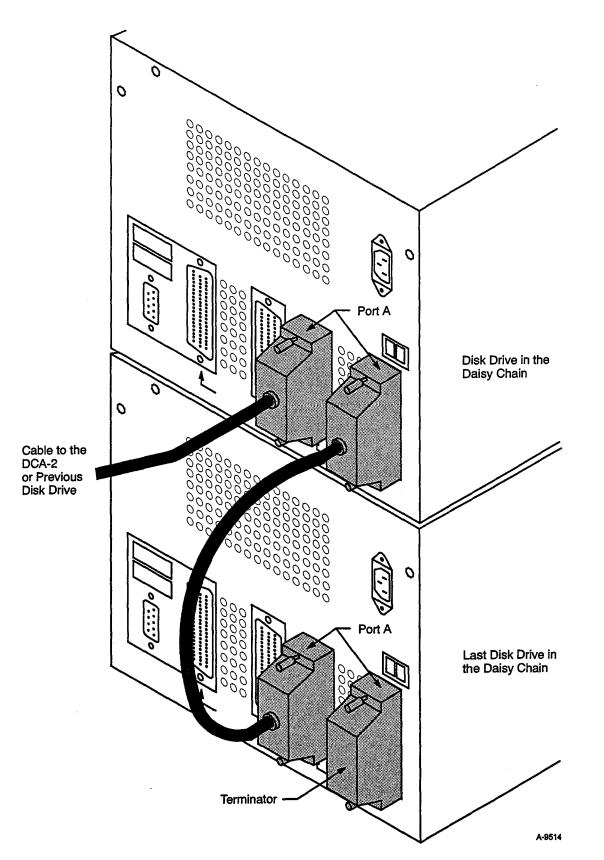

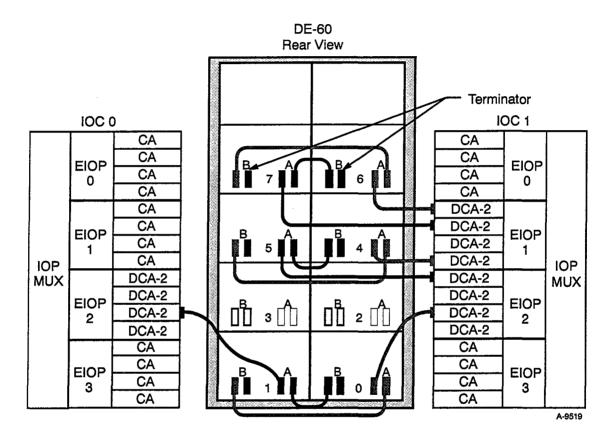

| Alternate-path Configuration | 2-15 |

## 3 DCA-2 BASIC THEORY OF OPERATIONS

| DCA-2 Options                         | 3-1  |

|---------------------------------------|------|

| 3YA Option                            | 3-1  |

| 3YC Option                            | 3-1  |

| 3DH0 Option                           | 3-2  |

| 3DH1 Option                           | 3-2  |

| 3DF Option                            | 3-5  |

| 3DE Option                            | 3-5  |

| 3YB Option                            | 3-6  |

| 3DG Option                            | 3-6  |

| 3DD Option                            | 3-6  |

| 3DI Option                            | 3-7  |

| 3DJ Option                            | 3-7  |

| RAM                                   | 3-7  |

| IPI-2 Interface Signals               | 3-8  |

| Control Signals                       | 3-8  |

| Select Out                            | 3-8  |

| Slave In                              | 3-8  |

| Master Out                            | 3-9  |

| Sync In                               | 3-9  |

| Sync Out                              | 3-9  |

| Attention In Signal                   | 3-9  |

| Data Signals                          | 3-9  |

| Bus A                                 | 3-10 |

| Bus B                                 | 3-10 |

| Bus A and Bus B                       | 3-10 |

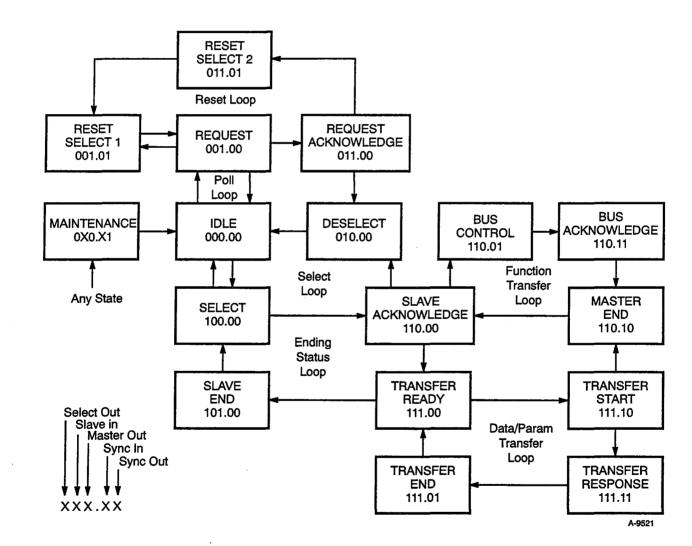

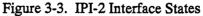

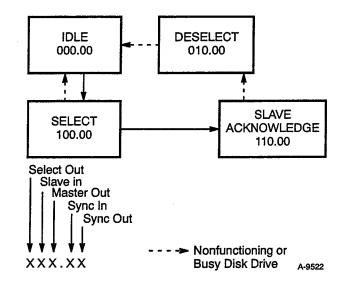

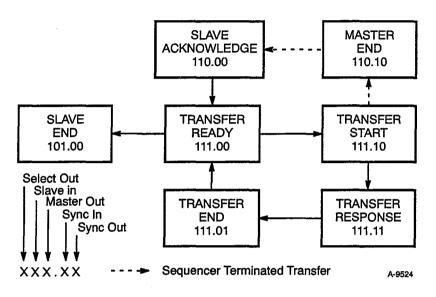

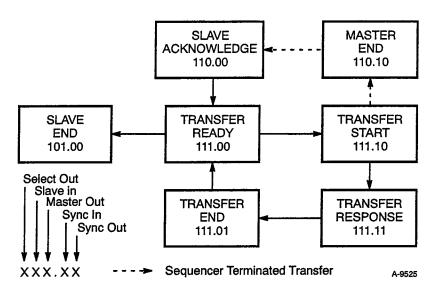

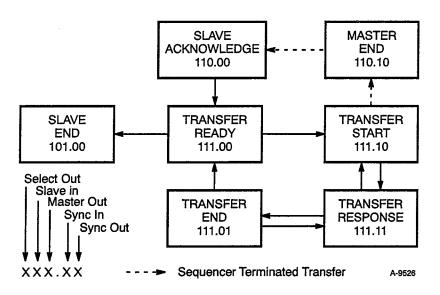

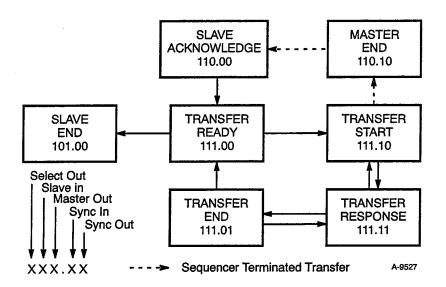

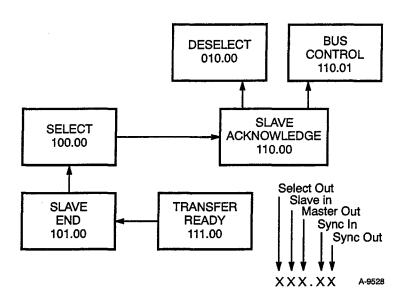

| IPI-2 Interface States                | 3-11 |

| IPI-2 Interface State Sequences       | 3-12 |

| Select Disk Drive Sequence            | 3-14 |

| Normal Selection                      | 3-14 |

| Busy Drive Selection                  | 3-15 |

| Nonfunctioning Drive Selection        | 3-15 |

| Bus Control Sequence                  | 3-16 |

| Interlocked Transfer-to-disk Sequence | 3-18 |

| Drive-terminated Transfer             | 3-18 |

## 3 DCA-2 BASIC THEORY OF OPERATIONS (continued)

| Sequencer-terminated Transfer              | 3-19 |  |

|--------------------------------------------|------|--|

| Interlocked Transfer-from-disk Sequence    |      |  |

| Drive-terminated Transfer                  | 3-20 |  |

| Sequencer-terminated Transfer              | 3-21 |  |

| Noninterlocked Transfer-to-disk Sequence   | 3-22 |  |

| Drive-terminated Transfer                  | 3-22 |  |

| Sequencer-terminated Transfer              | 3-23 |  |

| Noninterlocked Transfer-from-disk Sequence | 3-24 |  |

| Drive-terminated Transfer                  | 3-24 |  |

| Sequencer-terminated Transfer              | 3-25 |  |

| Ending Status Sequence                     | 3-26 |  |

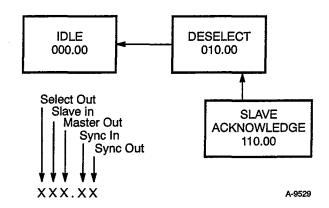

| Deselect Sequence                          | 3-28 |  |

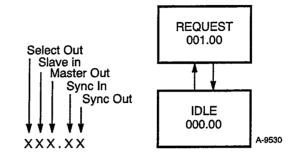

| Interrupt Request (Poll) Sequence          | 3-29 |  |

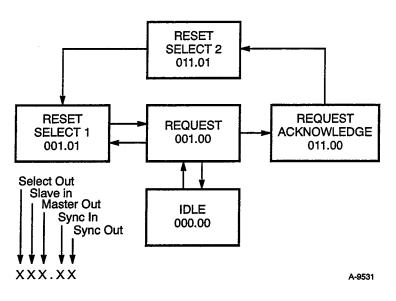

| Reset Disk Drive Sequence                  | 3-30 |  |

| Master Reset Sequence                      | 3-31 |  |

| Transfer Settings Request Sequence         | 3-32 |  |

| Drive Interrupt Request Sequence           | 3-33 |  |

#### **4 DCA-2 CHANNEL FUNCTIONS**

| Channel Function Descriptions                                   | 4-1 |

|-----------------------------------------------------------------|-----|

| DCA2:0 – Clear Channel Busy and Channel Done Flags              | 4-2 |

| DCA2:1 – Local Memory Input and Output Transfer                 | 4-2 |

| IPI-2 Protocol Transfers                                        | 4-3 |

| Sequencer Microcode Transfers                                   | 4-3 |

| Error-correction Code Register Transfer                         | 4-3 |

| DCA2:2 – Set ID Parameter 0                                     | 4-4 |

| DCA2:3 – Set ID Parameter 1                                     | 4-4 |

| DCA2:4 – Set Transfer Count                                     | 4-4 |

| DCA2:5 – Starting Sequencer Address and <i>i</i> Register Value | 4-5 |

| DCA2:6 – Disable Interrupt Enable                               | 4-5 |

| DCA2:7 – Enable Interrupt Enable                                | 4-6 |

| DCA2:10 – Read Local Memory Address                             | 4-6 |

| DCA2:11 – Read Local Memory Parcel Count              | 4-6  |

|-------------------------------------------------------|------|

| DCA2:12 – Status Function 0                           | 4-7  |

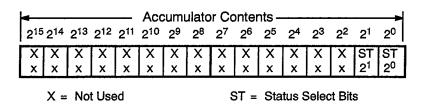

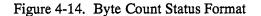

| Adapter Status                                        | 4-7  |

| 6X Condition Bits                                     | 4-7  |

| 7X Condition Bits                                     | 4-8  |

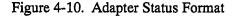

| Syndrome Status                                       | 4-8  |

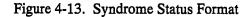

| Transfer Count Status                                 | 4-9  |

| Tag Status                                            | 4-9  |

| DCA2:13 – Status Function 1                           | 4-10 |

| Drive Ending Status                                   | 4-10 |

| ID Parameter 0 Status                                 | 4-10 |

| ID Parameter 1 Status                                 | 4-10 |

| DCA2:14 – Enter Local Memory Starting Address         | 4-11 |

| DCA2:15 – Enter Local Memory Parcel Count             | 4-11 |

| DCA2:16 – Enter $j$ and $k$ Control Register Contents | 4-12 |

| DCA2:17 – Enter Mode Select                           | 4-12 |

| Even Channel                                          | 4-12 |

| Odd Channel                                           | 4-14 |

| Sample Disk Drive Function Routines                   | 4-14 |

| Select Unit Routine                                   | 4-15 |

| Seek Routine                                          | 4-17 |

| Load Position Routine                                 | 4-19 |

| Poll Routine                                          | 4-21 |

| Write Sector Data Routine                             | 4-22 |

| Read Sector Data Routine                              | 4-25 |

## 5 DD-60 HARDWARE DESCRIPTION

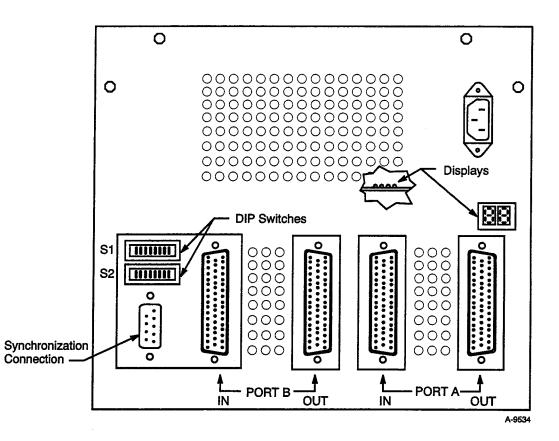

| Rear Panel               | 5-1 |

|--------------------------|-----|

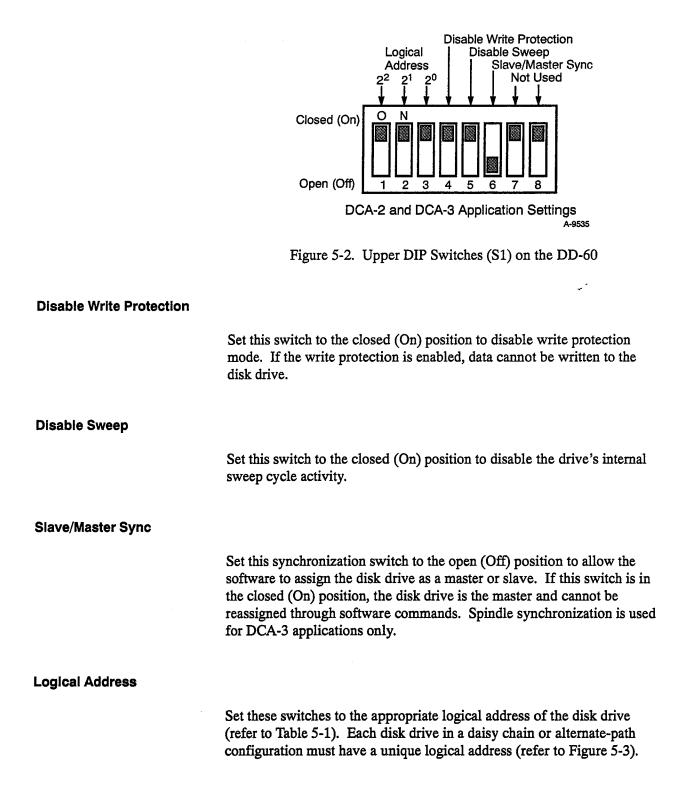

| Upper DIP Switches (S1)  | 5-2 |

| Disable Write Protection | 5-2 |

| Disable Sweep            | 5-2 |

| Slave/Master Sync        | 5-2 |

| Logical Address          | 5-2 |

| Lower DIP Switches (S2)  | 5-4 |

Cray Research Proprietary

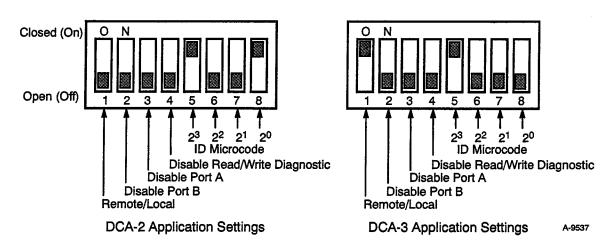

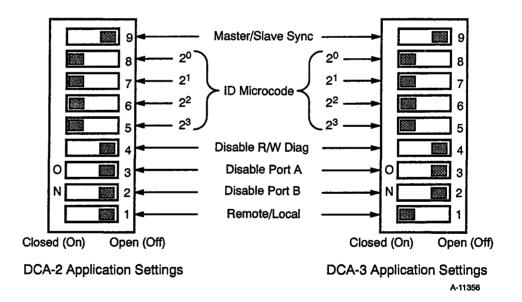

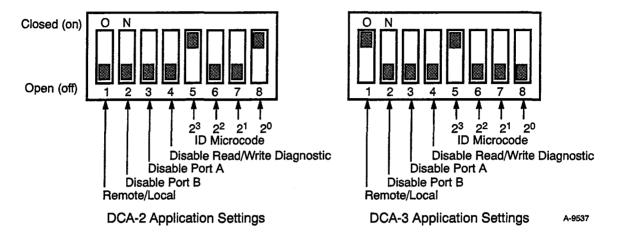

| Remote/Local                  | 5-4   |

|-------------------------------|-------|

| Disable Port B                | · 5-5 |

| Disable Port A                | 5-5   |

| Disable Read/Write Diagnostic | 5-5   |

| ID Microcode                  | 5-5   |

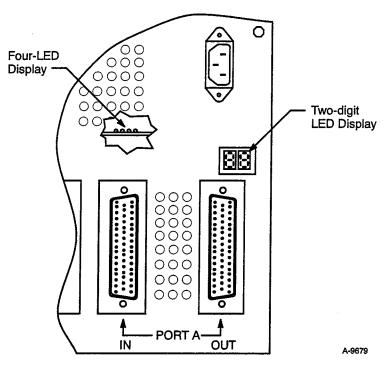

| Rear Panel Displays           | 5-6   |

| Two-digit LED Display         | 5-6   |

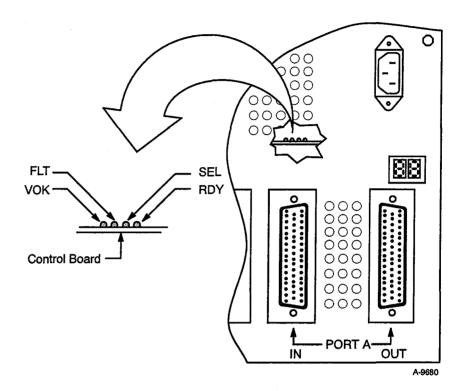

| Four-LED Display              | 5-7   |

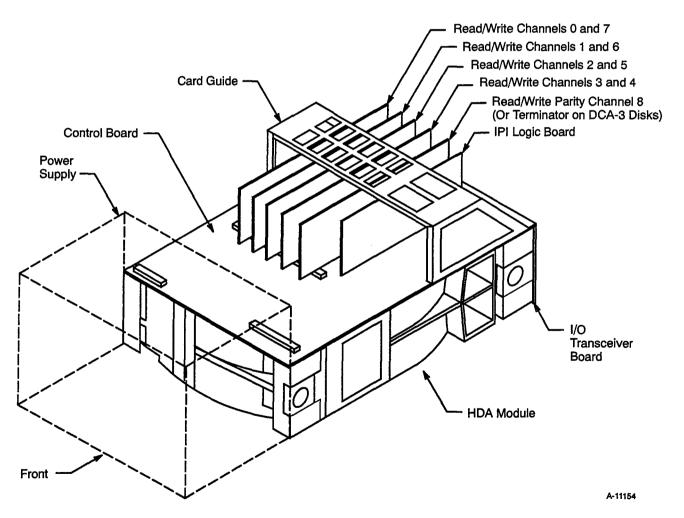

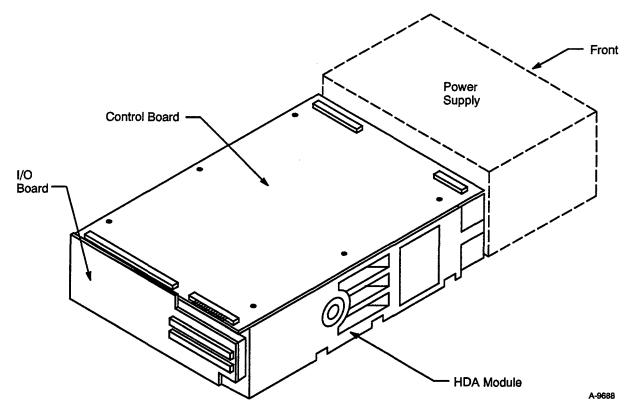

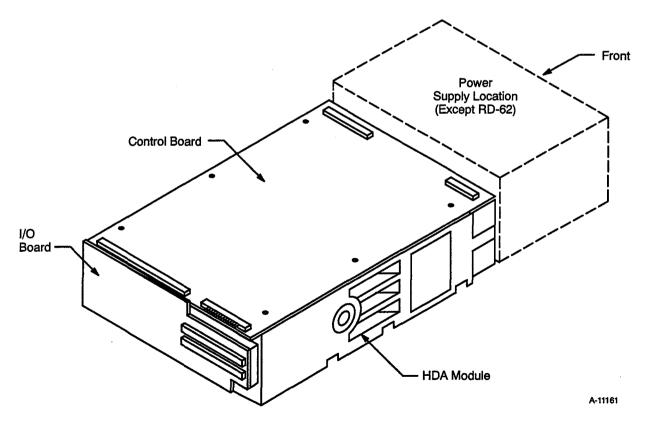

| Internal Components           | 5-8   |

| Circuit Boards                | 5-8   |

| Read/Write Boards             | 5-9   |

| IPI Logic Board               | 5-10  |

| Control Board                 | 5-10  |

| I/O Transceiver Board         | 5-10  |

| Power Supply                  | 5-10  |

| HDA Module                    | 5-10  |

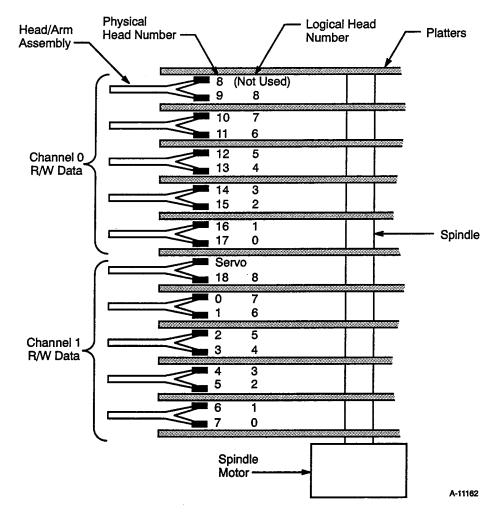

| Platters                      | 5-10  |

| Heads                         | 5-10  |

| Actuator                      | 5-11  |

| Spindle                       | 5-11  |

| Spindle Motor                 | 5-11  |

| Maintenance Panel             | 5-11  |

## 6 DD-60 FORMAT AND FLAW MANAGEMENT

| Cylinder Format                    | 6-1 |

|------------------------------------|-----|

| Sector Format                      | 6-2 |

| Timing Fields                      | 6-3 |

| Data Field                         | 6-3 |

| ECC Fields                         | 6-3 |

| Defect Swallow                     | 6-3 |

| ID Field                           | 6-4 |

| Media Flaws                        | 6-6 |

| Hideable Flaws                     | 6-6 |

| Hiding a Media Flaw                | 6-6 |

| Sector Format with a Hideable Flaw | 6-8 |

#### 6 DD-60 FORMAT AND FLAW MANAGEMENT (continued)

| Hiding Multiple Media Flaws in One Logical |      |

|--------------------------------------------|------|

| Sector                                     | 6-8  |

| Reading a Sector with a Hideable Flaw      | 6-9  |

| Unhideable Flaws                           | 6-10 |

| Flaw Maps and Tables                       | 6-10 |

| Factory Flaw Table                         | 6-10 |

| User Flaw Table                            | 6-10 |

| UNICOS Flaw Map                            | 6-11 |

|                                            |      |

#### 7 DD-61 HARDWARE DESCRIPTION

| Rear Panel                    | 7-1  |

|-------------------------------|------|

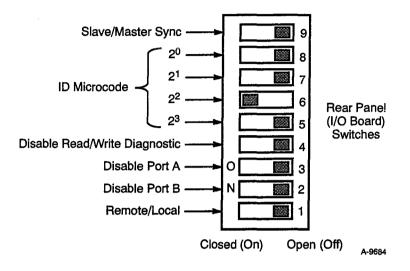

| Rear Panel DIP Switches       | 7-2  |

| Slave/Master Sync             | 7-2  |

| ID Microcode                  | 7-2  |

| Disable Read/Write Diagnostic | 7-3  |

| Disable Port A                | 7-3  |

| Disable Port B                | 7-3  |

| Remote/Local                  | 7-3  |

| Top Panel                     | 7-4  |

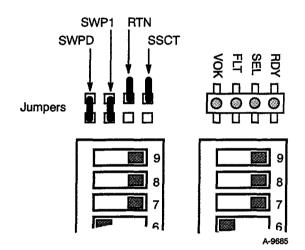

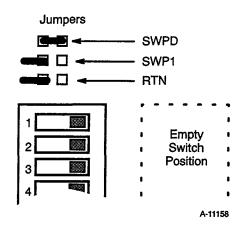

| Jumpers                       | 7-4  |

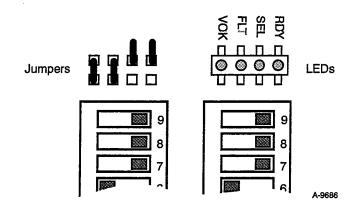

| LEDs                          | 7-5  |

| Top Panel DIP Switches        | 7-6  |

| Sector Switches               | 7-6  |

| Disable Write Protection      | 7-6  |

| Logical Address               | 7-6  |

| Internal Components           | 7-8  |

| Circuit Boards                | 7-8  |

| HDA Module                    | 7-9  |

| Platters                      | 7-9  |

| Heads                         | 7-10 |

| Actuator                      | 7-10 |

| Spindle                       | 7-10 |

| Spindle Motor                 | 7-10 |

| Power Supply                  | 7-10 |

| Maintenance Panel             | 7-10 |

#### 8 DD-61 FORMAT AND FLAW MANAGEMENT

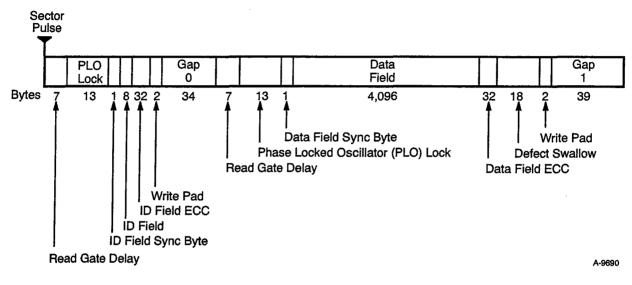

| Cylinder Format                       | 8-1 |

|---------------------------------------|-----|

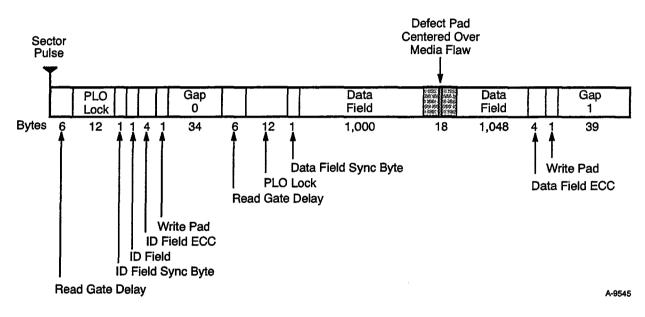

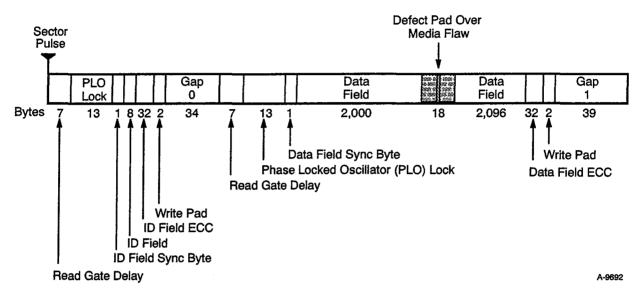

| Sector Format                         | 8-2 |

| Timing Fields                         | 8-2 |

| Data Field                            | 8-2 |

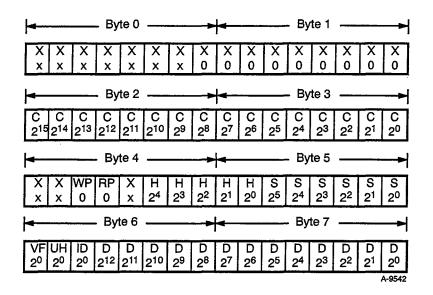

| ID Field                              | 8-2 |

| Error-correction Code Fields          | 8-3 |

| Defect Swallow                        | 8-4 |

| Media Flaws                           | 8-4 |

| Hideable Flaws                        | 8-4 |

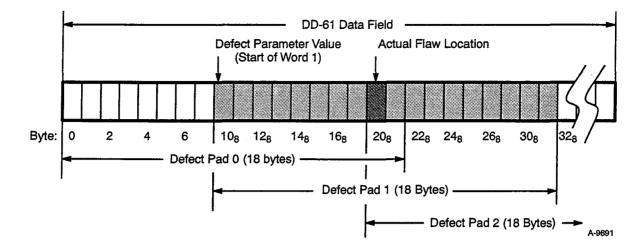

| Hiding a Media Flaw                   | 8-4 |

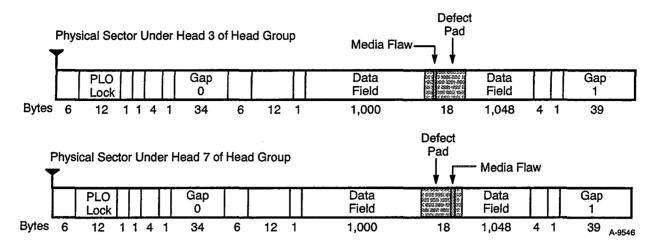

| Sector Format with a Hideable Flaw    | 8-6 |

| Reading a Sector with a Hideable Flaw | 8-6 |

| Unhideable Flaws                      | 8-7 |

| Flaw Maps and Tables                  | 8-7 |

| Factory Flaw Table                    | 8-7 |

| User Flaw Table                       | 8-7 |

| UNICOS Flaw Map                       | 8-8 |

#### 9 DD-62 AND RD-62 HARDWARE DESCRIPTION

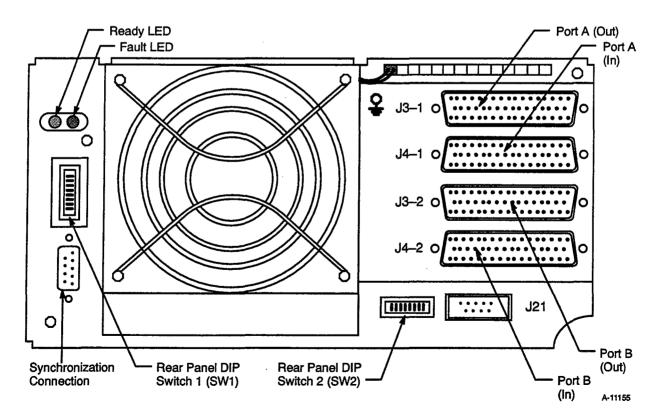

| Rear Panel               | 9-1  |

|--------------------------|------|

| Rear Panel DIP Switches  | 9-2  |

| Rear Panel DIP Switch 1  | 9-2  |

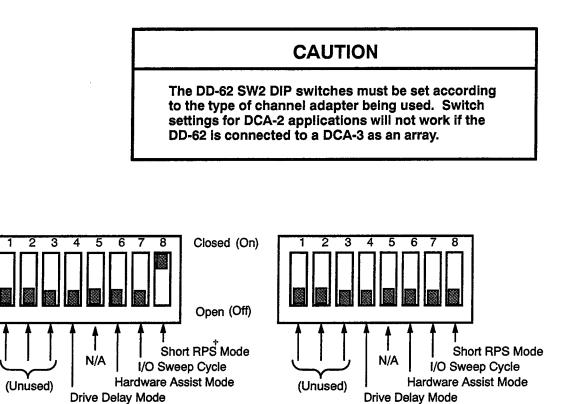

| Rear Panel DIP Switch 2  | 9-4  |

| Top Panel                | 9-5  |

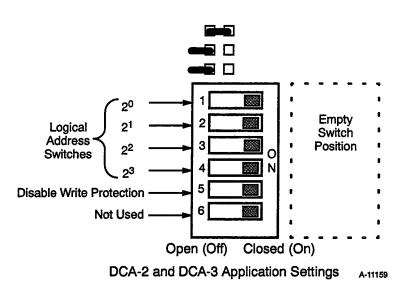

| Top Panel DIP Switch 3   | 9-5  |

| Logical Address Switches | 9-6  |

| Disable Write Protection | 9-7  |

| Jumpers                  | 9-7  |

| Internal Components      | 9-8  |

| Circuit Boards           | 9-8  |

| Power Supply             | 9-9  |

| HDA Module               | 9-9  |

| Platters                 | 9-10 |

| Heads                    | 9-10 |

#### 9 DD-62 AND RD-62 HARDWARE DESCRIPTION (continued)

| Actuator . | <br>9-10 |

|------------|----------|

|            |          |

Spindle and Motor9-10Maintenance Panel9-10

#### 10 DD-62 AND RD-62 FORMAT AND FLAW MANAGEMENT

| Cylinder Format                            | 10-1          |

|--------------------------------------------|---------------|

| Sector Format                              | 10-2          |

| Timing Fields                              | 10-3          |

| Data Field                                 | 10-3          |

| ECC Fields                                 | 10-3          |

| Defect Swallow                             | 10-4          |

| ID Field                                   | 10-4          |

| Media Flaws                                | 10-6          |

| Hideable Flaws                             | 10-6          |

| Hiding a Media Flaw                        | 10-6          |

| Sector Format with a Hideable Flaw         | 10-8          |

| Hiding Multiple Media Flaws in One Logical |               |

| Sector                                     | 10-8          |

| Reading a Sector with a Hideable Flaw      | 10 <b>-</b> 9 |

| Unhideable Flaws                           | 10-10         |

| Flaw Maps and Tables                       | 10-10         |

| Factory Flaw Table                         | 10-10         |

| User Flaw Table                            | 10-10         |

| UNICOS Flaw Map                            | 10-11         |

#### 11 RDE-6 REMOVABLE DISK ENCLOSURE

| RDE-6 Overview                            | 11-1         |

|-------------------------------------------|--------------|

| RDE-6 Component Locations                 | 11 <b>-2</b> |

| RDE-6 Cabinet Locking Mechanisms          | 11-4         |

| RDE-6 Bulkhead Connections and Cabling    | 11-6         |

| RDE-6 Drawer Insertion/Removal Procedures | 11-7         |

| Drawer Insertion Procedure                | 11-7         |

| Drawer Removal Procedure                  | 11-8         |

## 11 RDE-6 REMOVABLE DISK ENCLOSURE (continued)

| RDE-6 Servicing Information                            | 11-10 |

|--------------------------------------------------------|-------|

| RDE-6 and RD-62 Parts List                             | 11-10 |

| Spindle and/or Drawer Replacement Procedures           | 11-11 |

| RDE-6 Chassis Removal and Access                       | 11-13 |

| RDE-6 Power Controller Assembly Replacement Procedures | 11-16 |

| RD-62 Power-supply Replacement Procedures              | 11-17 |

| Solenoid Logic Control Board Replacement Procedures    | 11-19 |

| Mechanical Solenoid Assembly Replacement Procedures    | 11-21 |

## 12 DCA-2 SYSTEMS STATUS

| OLHPA                               | 12-1  |

|-------------------------------------|-------|

| General Status                      | 12-3  |

| DCA2:12 Statuses                    | 12-4  |

| Condition Bits                      | 12-4  |

| 6X Condition Bits                   | 12-4  |

| 7X Condition Bits                   | 12-5  |

| Adapter Status                      | 12-5  |

| Syndrome Status                     | 12-7  |

| Transfer Count Status               | 12-7  |

| Tag Status                          | 12-8  |

| DCA2:13 Statuses                    | 12-9  |

| Drive Ending Status                 | 12-9  |

| Initial Drive Ending Status         | 12-9  |

| Final Drive Ending Status           | 12-10 |

| ID Parameter 0 Status               | 12-10 |

| ID Parameter 1 Status               | 12-11 |

| Drive Status Response Block         | 12-12 |

| Drive Extended Status Block         | 12-16 |

| Flaw Location Information           | 12-19 |

| DD-60 Rear Panel Display I/O Status | 12-19 |

## **13 DCA-3 BASIC THEORY OF OPERATION**

| Data Format                   | 13-2 |

|-------------------------------|------|

| DCA-3 Options                 | 13-3 |

| 7DK Option                    | 13-3 |

| 7DL Option                    | 13-4 |

| 7DN Options                   | 13-7 |

| Deskew Buffers                | 13-8 |

| 6DM options                   | 13-9 |

| DA-60 and DA-62 Data Striping | 13-9 |

| DCA-3 Handling Precautions    | 13-9 |

|                               |      |

## **14 DCA-3 CHANNEL FUNCTIONS**

| Channel Function Descriptions                | 14-1  |

|----------------------------------------------|-------|

| DCA3:0 – Clear Channel Flags                 | 14-2  |

| DCA3:1 - Start Transfer                      | 14-2  |

| DCA3:1 - Start Input Transfer (even channel) | 14-2  |

| DCA3:1 - Start Output Transfer (odd channel) | 14-4  |

| DCA3:2 – Set ID Parameter 0                  | 14-4  |

| DCA3:3 – Set ID Parameter 1                  | 14-5  |

| DCA3:4 – Set Transfer Count                  | 14-5  |

| DCA3:5 - Start Device Function               | 14-6  |

| DCA3:6 – Disable Interrupt Enable Flag       | 14-8  |

| DCA3:7 – Enable Interrupt Enable             | 14-9  |

| DCA3:10 - Read Local Memory Address          | 14-9  |

| DCA3:11 – Read Inverted Local Memory Parcel  | 14.0  |

| Count                                        | 14-9  |

| DCA3:12 - Read Status 0                      | 14-9  |

| DCA3:13 - Read Status 1                      | 14-13 |

| DCA3:14 – Set Local Memory Starting Address  | 14-13 |

| DCA3:15 – Set Local Memory Parcel Count      | 14-14 |

| DCA3:16 – Write Control Bus Data             | 14-15 |

| DCA3:17 - Set Operating Mode                 | 14-16 |

| Set Array Type with $M0 = 0$                 | 14-16 |

| Set Array Mode with $M0 = 1$                 | 14-16 |

#### 15 DCA-3 TO DISK ARRAY CABLING

| Terminology                                     | 15-2  |

|-------------------------------------------------|-------|

| Drive vs. Spindle                               | 15-2  |

| Cabling Hardware                                | 15-3  |

| Cabling Hardware Components                     | 15-3  |

| DCA-3-to-spindle Data Cables                    | 15-4  |

| 2X Daisy Chain Cable                            | 15-6  |

| Spindle-to-spindle Synchronization Cable        | 15-8  |

| Data Cable Terminator                           | 15-9  |

| Synchronization (Sync) Cable Terminator         | 15-9  |

| IOS-E Bulkhead Connections                      | 15-10 |

| Cabling Restrictions                            | 15-12 |

| Cabling Hardware Requirements                   | 15-12 |

| Configuration Options                           | 15-13 |

| Single-channel to Single-unit Configuration     | 15-13 |

| Single-channel to Daisy Chain Configuration     | 15-13 |

| Alternate-path to Daisy Chain Configuration     | 15-13 |

| Disk Enclosure Resilient Configuration          | 15-14 |

| Single-channel to Single-array Configuration    | 15-14 |

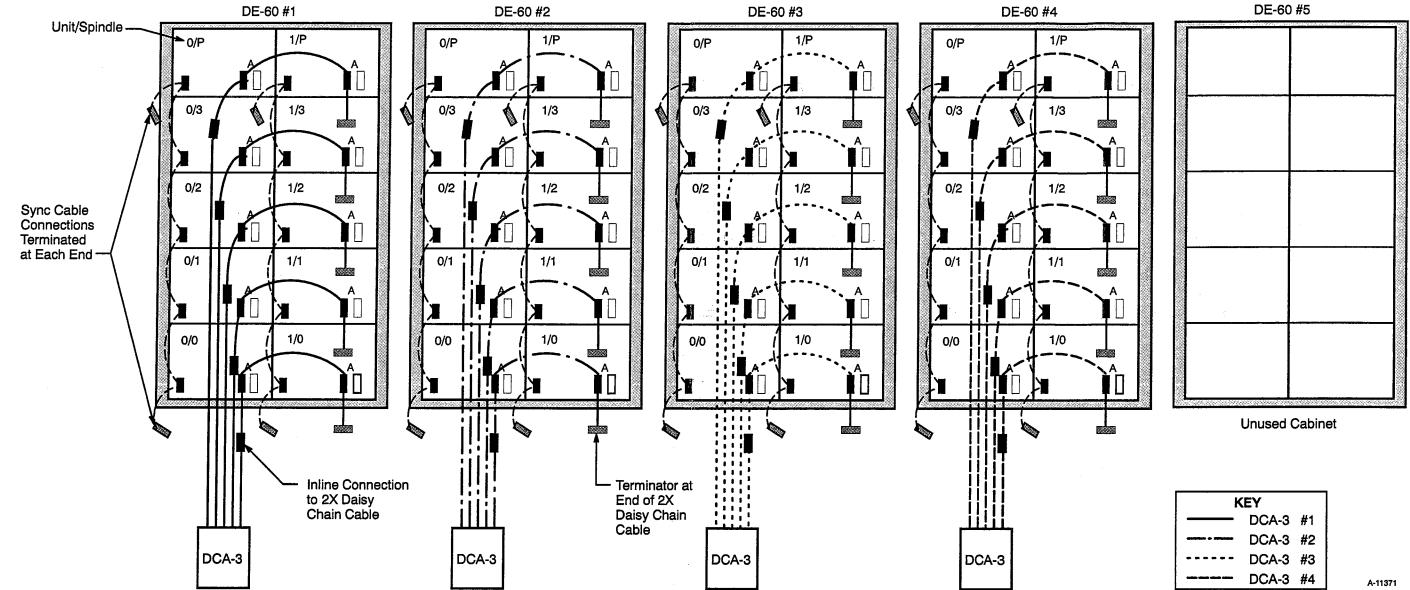

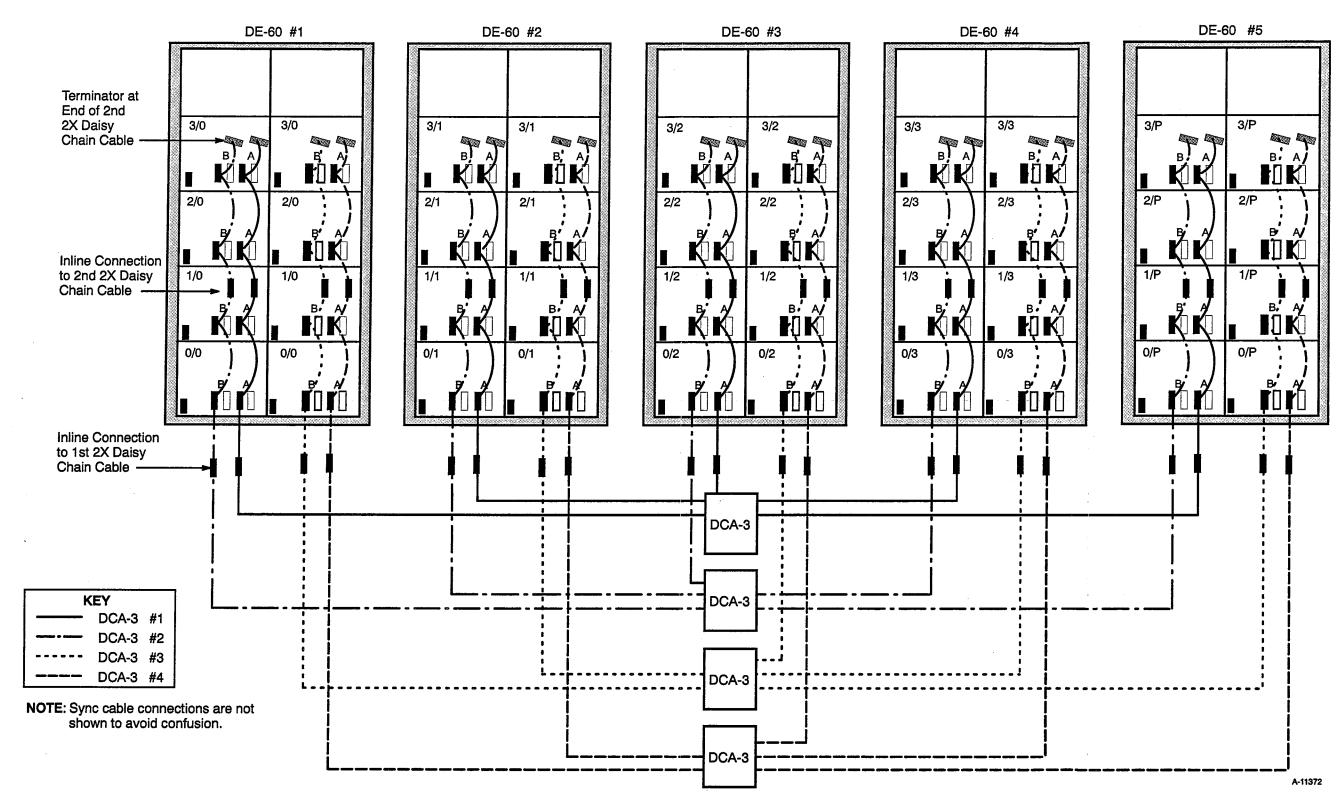

| Daisy Chained Configurations                    | 15-18 |

| Two-array Daisy Chain Configuration             | 15-18 |

| Three-array Daisy Chain Configuration           | 15-19 |

| Four-array Daisy Chain Configuration            | 15-20 |

| Five-array Daisy Chain Configuration            | 15-21 |

| Six-array Daisy Chain Configuration             | 15-22 |

| Seven- or Eight-array Daisy Chain Configuration | 15-22 |

| Alternate Path and Disk Enclosure Resiliency    | 15-22 |

| Minimum Resiliency                              | 15-22 |

| Enhanced Resiliency                             | 15-23 |

|                                                 |       |

## 16 DCA-3 SYSTEMS STATUS

| Status Cross-references | 16-1 |

|-------------------------|------|

| ERRPT                   | 16-1 |

| OLHPA                   | 16-3 |

## 16 DCA-3 SYSTEMS STATUS (continued)

| General Status                      | 16-6  |

|-------------------------------------|-------|

| DCA3:12 Statuses                    | 16-7  |

| Interrupt Status                    | 16-7  |

| SECDED Status                       | 16-8  |

| Transfer Count Status               | 16-9  |

| IPI Tag Status                      | 16-10 |

| Busy Status                         | 16-10 |

| Done Status                         | 16-11 |

| DMA Acknowledge Pending Status      | 16-11 |

| DCA3:13 Statuses                    | 16-12 |

| Drive Ending Status                 | 16-12 |

| Initial Drive Ending Status         | 16-12 |

| Final Drive Ending Status           | 16-13 |

| ID Parameter 0 Status               | 16-13 |

| ID Parameter 1 Status               | 16-14 |

| Bus A and Bus B Data                | 16-15 |

| Drive Status Response Block         | 16-15 |

| Drive Extended Status Block         | 16-19 |

| Flaw Location Information           | 16-22 |

| DD-60 Rear Panel Display I/O Status | 16-23 |

|                                     |       |

## **17 MAINTENANCE PROCEDURES**

| Diagnostics and Utilities                      | 17-1 |

|------------------------------------------------|------|

| Device Maintenance System 2                    | 17-1 |

| Disk Flaw Management System (DFM)              | 17-2 |

| Disk Device Maintenance System (DDMS)          | 17-2 |

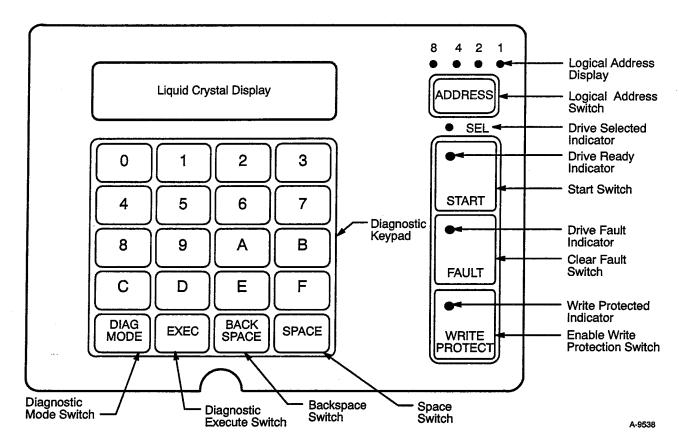

| Maintenance Panel                              | 17-3 |

| Installation and Removal                       | 17-5 |

| Installation                                   | 17-5 |

| Removal                                        | 17-5 |

| Diagnostic Test Execution                      | 17-6 |

| Spin Up and Spin Down Procedures               | 17-7 |

| Spin Up/Down Procedures for DCA-2 Applications | 17-7 |

| DD-60 Disk Drive                               | 17-7  |

|------------------------------------------------|-------|

| DD-61 Disk Drive                               | 17-8  |

| DD-62 Disk Drives                              | 17-9  |

| Spin Up/Down Procedures for DCA-3 Applications | 17-10 |

| DA-60 Spindles                                 | 17-10 |

| DA-62 Spindles                                 | 17-11 |

| Converting a DD-60 for DCA-3 Applications      | 17-12 |

| Spindle Removal and Replacement Procedures     |       |

## FIGURES

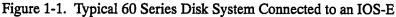

| Figure 1-1.  | Typical 60 Series Disk System Connected to an         IOS-E      | 1-1  |

|--------------|------------------------------------------------------------------|------|

| Figure 1-2.  | Front and Rear Views of the DE-60                                | 1-5  |

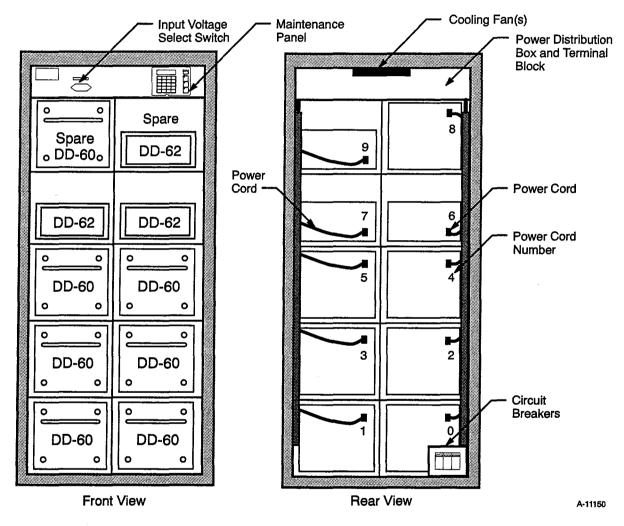

| Figure 1-3.  | RDE-6 with RD-62 Removable Disk Drives                           | 1-7  |

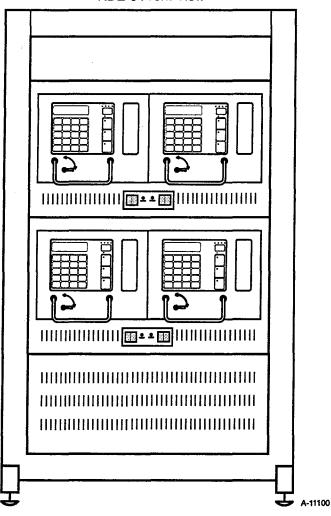

| Figure 1-4.  | Block Diagram of DCA-2 Operations                                | 1-9  |

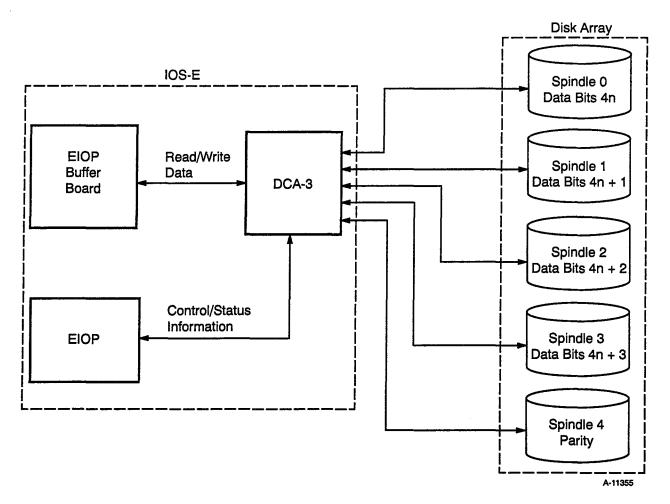

| Figure 1-5.  | Block Diagram of DCA-3 Operations                                | 1-10 |

| Figure 2-1.  | Initial Daisy Chain Cabling for 60 Series Disk<br>Systems        | 2-2  |

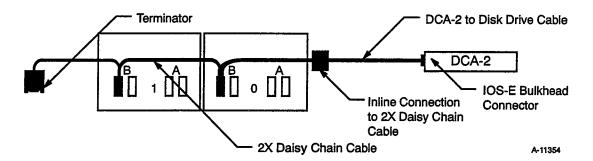

| Figure 2-2.  | 2X Daisy Chain Cabling for 60 Series Disk<br>Systems             | 2-2  |

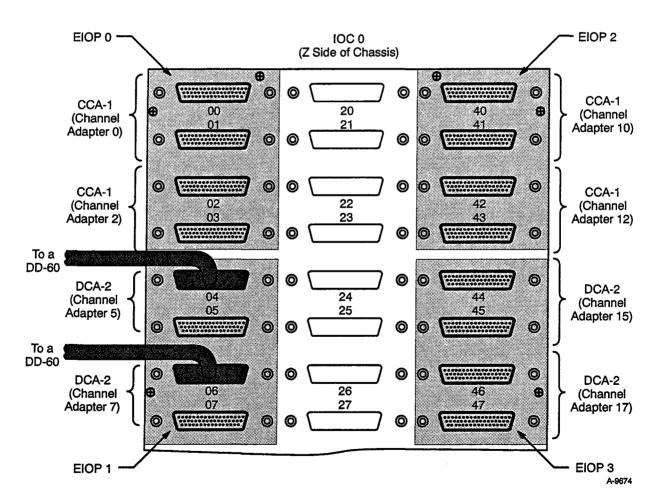

| Figure 2-3.  | Possible IOC 0 Configuration on a CRAY Y-MP8I<br>Computer System | 2-3  |

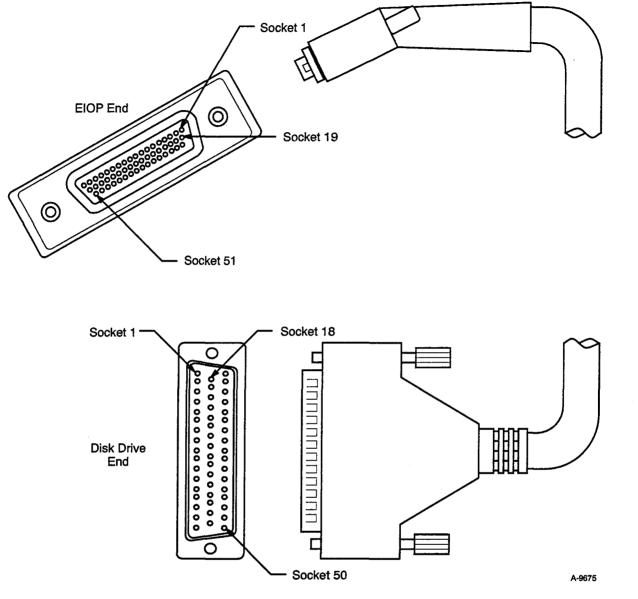

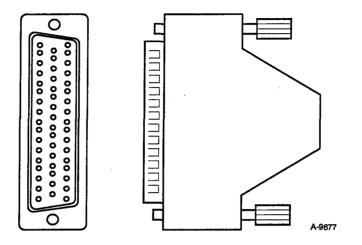

| Figure 2-4.  | DCA-2 to Disk Drive Cable Sockets                                | 2-6  |

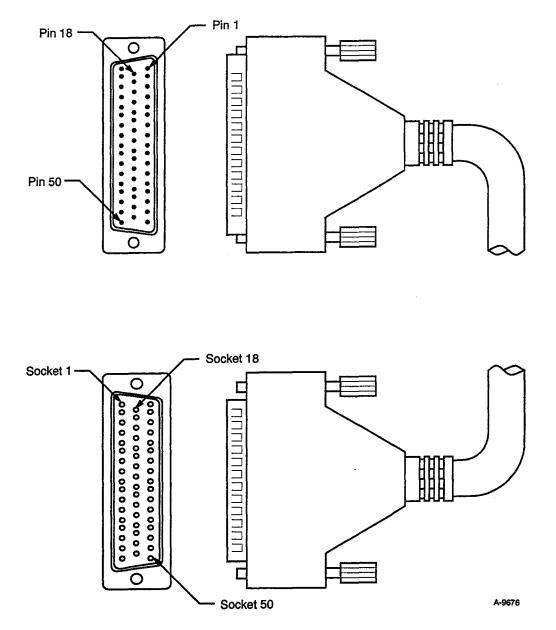

| Figure 2-5.  | Daisy Chain (Drive-to-drive) Cable Pins and Sockets              | 2-8  |

| Figure 2-6.  | Terminator for 60 Series Disk Systems                            | 2-9  |

| Figure 2-7.  | 60 Series Disk Drive Cable Label                                 | 2-10 |

| Figure 2-8.  | Single-port Configurations                                       | 2-11 |

| Figure 2-9.  | Single-port Configuration Cabling                                | 2-12 |

| Figure 2-10. | Daisy Chain Configuration                                        | 2-13 |

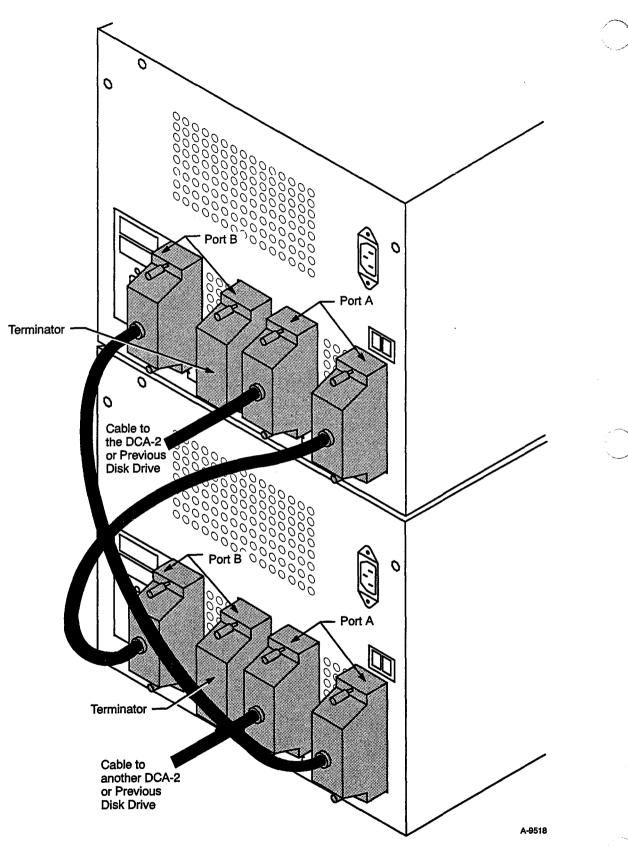

| Figure 2-11. | Daisy Chain Configuration Cabling                                | 2-14 |

| Figure 2-12. | Alternate-path Daisy Chain Configuration<br>Combinations         | 2-15 |

| Figure 2-13. | Alternate-path Configuration Cabling                             | 2-16 |

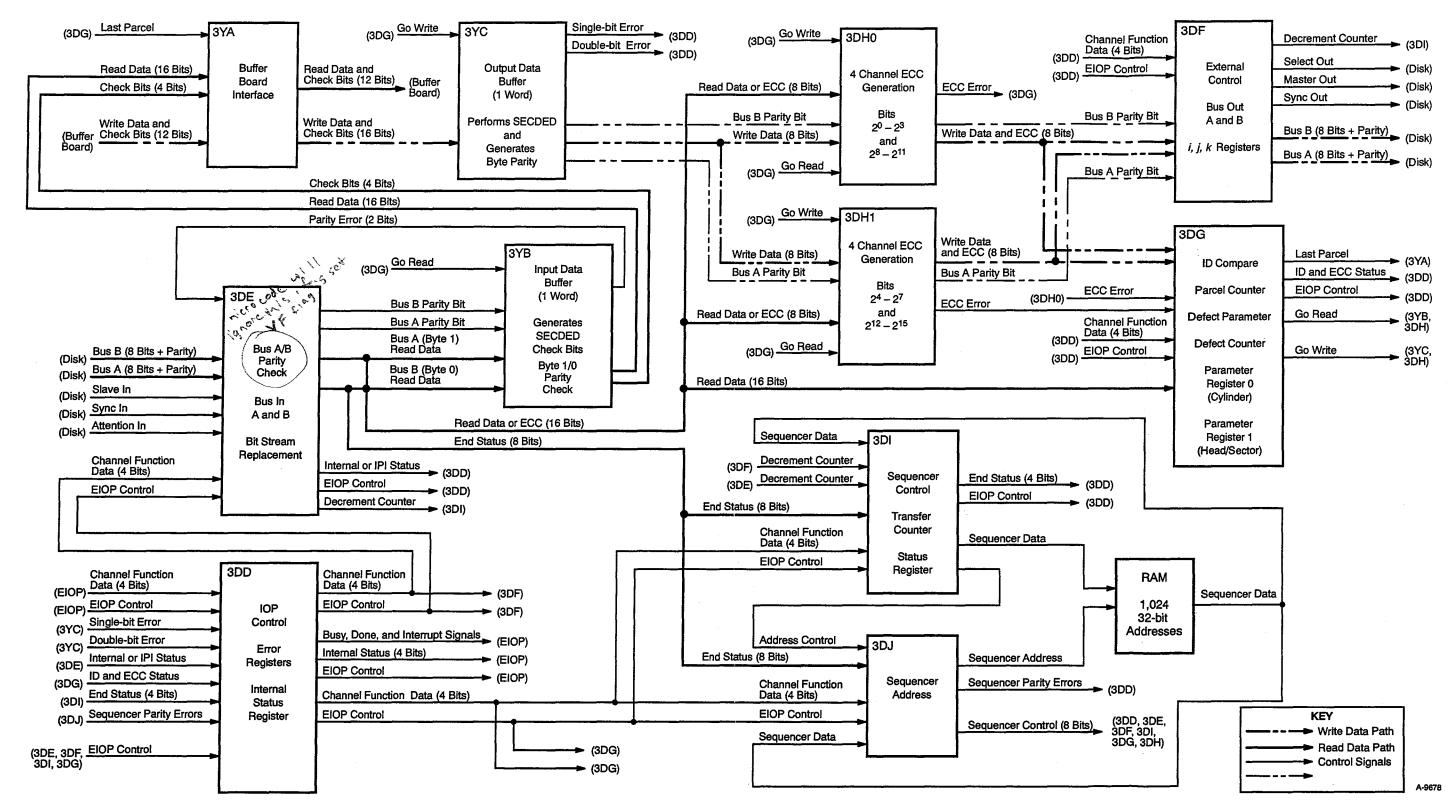

| Figure 3-1.  | DCA-2 Options, Data Paths, and Control Signals           | 3-3  |

|--------------|----------------------------------------------------------|------|

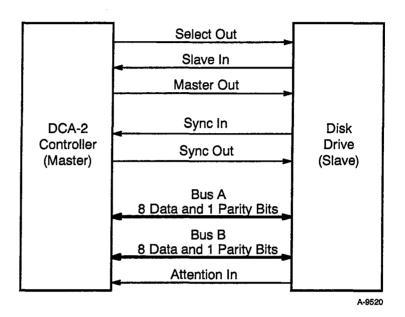

| Figure 3-2.  | IPI-2 Interface Signals                                  | 3-8  |

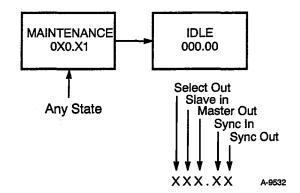

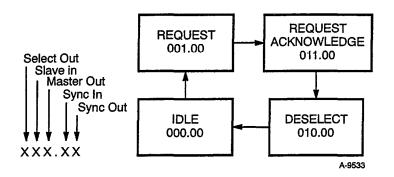

| Figure 3-3.  | IPI-2 Interface States                                   | 3-11 |

| Figure 3-4.  | Select Disk Drive Sequence                               | 3-14 |

| Figure 3-5.  | Bus Control Sequence                                     | 3-16 |

| Figure 3-6.  | Interlocked Transfer-to-disk Sequence                    | 3-18 |

| Figure 3-7.  | Interlocked Transfer-from-disk Sequence                  | 3-20 |

| Figure 3-8.  | Noninterlocked Transfer-to-disk Sequence                 | 3-22 |

| Figure 3-9.  | Noninterlocked Transfer-from-disk Sequence               | 3-24 |

| Figure 3-10. | Ending Status Sequence                                   | 3-26 |

| Figure 3-11. | Deselect Sequence                                        | 3-28 |

| Figure 3-12. | Interrupt Request (Poll) Sequence                        | 3-29 |

| Figure 3-13. | Reset Disk Drive Sequence                                | 3-30 |

| Figure 3-14. | Master Reset Sequence                                    | 3-31 |

| Figure 3-15. | Transfer Settings Request and Interrupt Request Sequence | 3-32 |

| Figure 4-1.  | EIOP Instruction d Field or EIOP B Register              | 4-2  |

| Figure 4-2.  | DCA2:1 Sequencer Starting Address                        | 4-2  |

| Figure 4-3.  | ID Parameter 0 Format                                    | 4-4  |

| Figure 4-4.  | ID Parameter 1 Format                                    | 4-4  |

| Figure 4-5.  | Transfer Count Format                                    | 4-5  |

| Figure 4-6.  | DCA2:5 Sequencer Starting Address Format                 | 4-5  |

| Figure 4-7.  | Current Local Memory Address Format                      | 4-6  |

| Figure 4-8.  | Inverted Parcel Count Format                             | 4-6  |

| Figure 4-9.  | Status Select Format                                     | 4-7  |

| Figure 4-10. | Adapter Status Format                                    | 4-7  |

| Figure 4-11. | 6X Condition Bits Format                                 | 4-8  |

| Figure 4-12. | 7X Condition Bits Format                                 | 4-8  |

| Figure 4-13. | Syndrome Status Format                                   | 4-8  |

| Figure 4-14. | Byte Count Status Format                                 | 4-9  |

| Figure 4-15. | Tag Status Format                                        | 4-9  |

| Figure 4-16. | Drive Ending Status Format                               | 4-10 |

| Figure 4-17. | Local Memory Starting Address Format                      | 4-11 |

|--------------|-----------------------------------------------------------|------|

| Figure 4-18. | Parcel Count Format                                       | 4-11 |

| Figure 4-19. | j and $k$ Register Values                                 | 4-12 |

| Figure 4-20. | Mode Bits for the Sequencer                               | 4-13 |

| Figure 4-21. | Bit Stream Select Bits                                    | 4-14 |

| Figure 4-22. | Disk Drive Address for Logical Address 5                  | 4-15 |

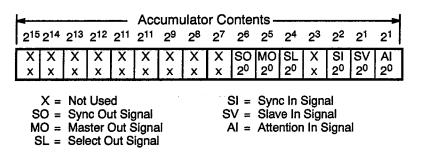

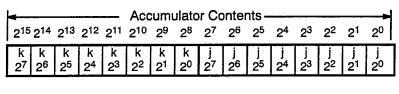

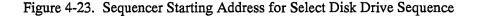

| Figure 4-23. | Sequencer Starting Address for Select Disk Drive Sequence | 4-16 |

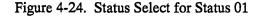

| Figure 4-24. | Status Select for Status 01                               | 4-16 |

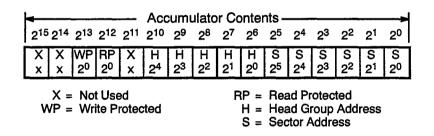

| Figure 4-25. | Drive Select Response in the Accumulator                  | 4-16 |

| Figure 4-26. | Transfer Count for a Seek Routine                         | 4-17 |

| Figure 4-27. | Parcel Count for a Seek Routine                           | 4-18 |

| Figure 4-28. | Load Cylinder Bus Control Code                            | 4-18 |

| Figure 4-29. | Sequencer Starting Address for Command Load               | 4-18 |

| Figure 4-30. | Transfer Count for a Load Position Routine                | 4-19 |

| Figure 4-31. | Parcel Count for a Load Position Routine                  | 4-20 |

| Figure 4-32. | Load Position Bus Control Code                            | 4-20 |

| Figure 4-33. | Sequencer Starting Address for a Deselect<br>Sequence     | 4-21 |

| Figure 4-34. | Interrupt Request in the Accumulator                      | 4-22 |

| Figure 4-35. | Sequencer Starting Address for a Poll Sequence            | 4-22 |

| Figure 4-36. | Transfer Count for a DD-60 Disk Drive                     | 4-23 |

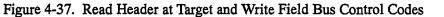

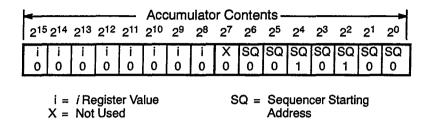

| Figure 4-37. | Read Header at Target and Write Field Bus Control Codes   | 4-23 |

| Figure 4-38. | Sequencer Starting Address for a Write Data<br>Sequence   | 4-24 |

| Figure 4-39. | Read Header at Target and Read Field Bus Control<br>Codes | 4-25 |

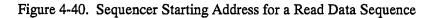

| Figure 4-40. | Sequencer Starting Address for a Read Data<br>Sequence    | 4-26 |

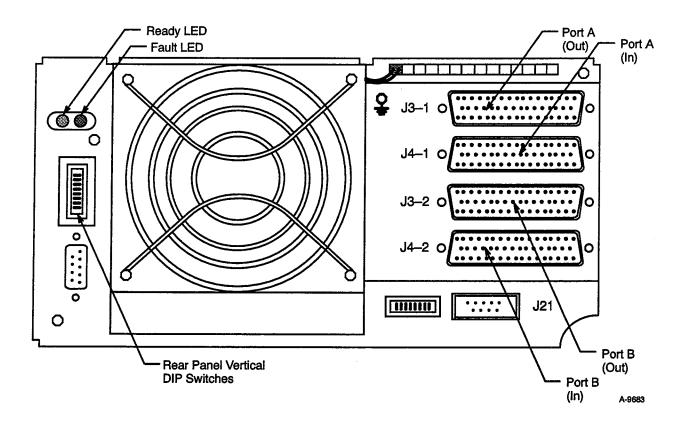

| Figure 5-1.  | Rear Panel of a DD-60 Disk Drive                          | 5-1  |

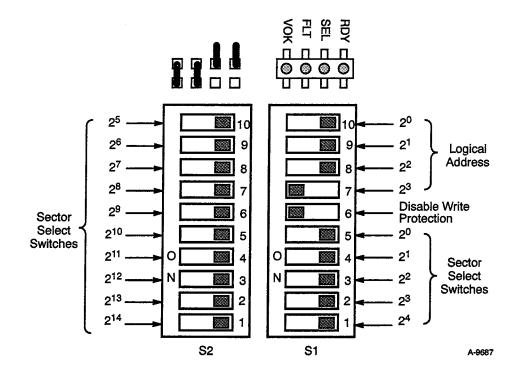

| Figure 5-2.  | Upper DIP Switches (S1) on the DD-60                      | 5-2  |

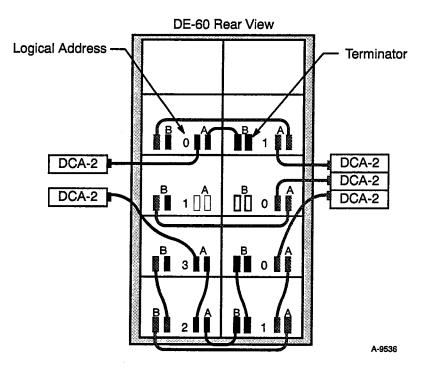

| Figure 5-3.  | Logical Addresses of DCA-2 Drives in<br>a DE-60           | 5-3  |

÷...

| Figure 5-4. | Lower DIP Switches (S2) on the DD-60                                       | 5-4 |

|-------------|----------------------------------------------------------------------------|-----|

| Figure 5-5. | DD-60 Rear Panel Displays                                                  | 5-6 |

| Figure 5-6. | Four-LED Display in the DD-60                                              | 5-7 |

| Figure 5-7. | DD-60 Component Locations                                                  | 5-8 |

| Figure 5-8. | DD-60 Physical Head Locations in the HDA                                   | 5-9 |

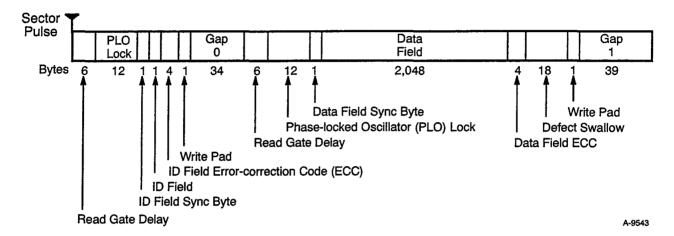

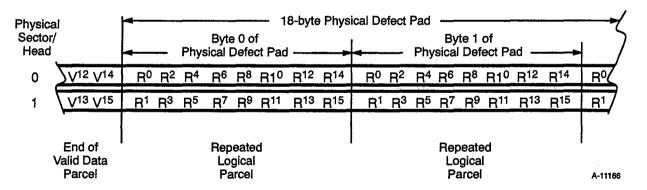

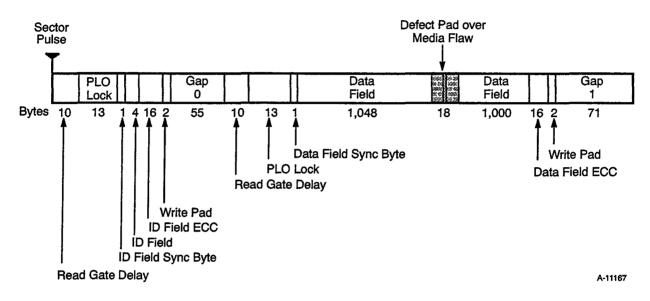

| Figure 6-1. | DD-60 Physical Sector Format                                               | 6-2 |

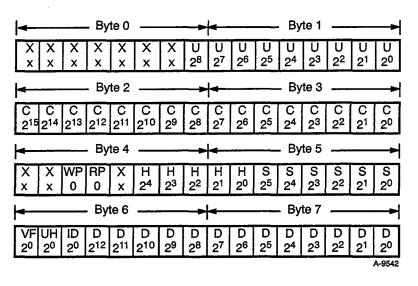

| Figure 6-2. | DD-60 Logical ID Information                                               | 6-4 |

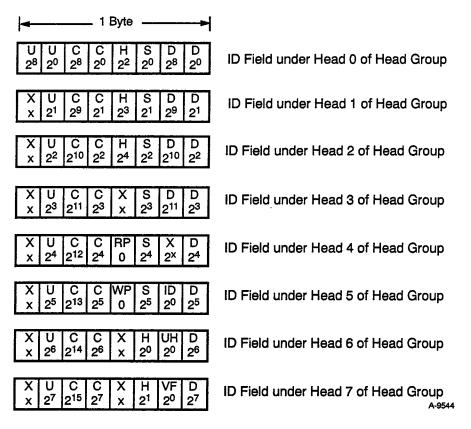

| Figure 6-3. | DD-60 Physical ID Fields                                                   | 6-5 |

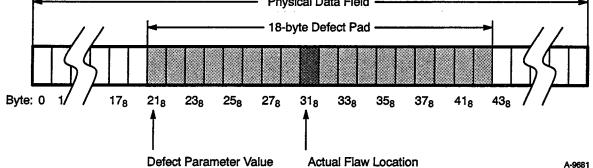

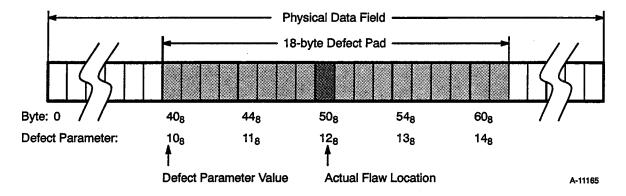

| Figure 6-4. | Defect Parameter and Actual Flaw Locations in a DD-60 Data Field           | 6-6 |

| Figure 6-5. | Bytes 0 and 1 of the Physical Defect Pads                                  | 6-7 |

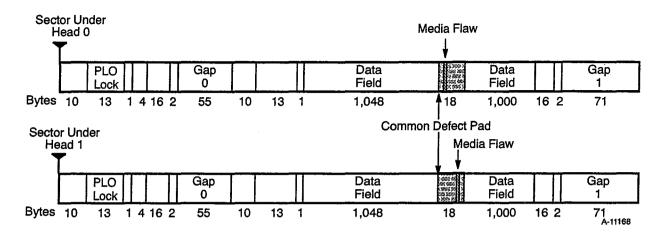

| Figure 6-6. | DD-60 Physical Sector with a Hideable Flaw                                 | 6-8 |

| Figure 6-7. | Two Physical Sectors with Hideable Flaws Covered         by One Defect Pad | 6-9 |

| Figure 7-1. | Rear Panel of a DD-61 Disk Drive                                           | 7-1 |

| Figure 7-2. | Rear Panel (I/O Board) DIP Switches on the DD-61                           | 7-2 |

| Figure 7-3. | Top Panel Jumpers on the DD-61                                             | 7-4 |

| Figure 7-4. | Top Panel LEDs on the DD-61                                                | 7-5 |

| Figure 7-5. | Top Panel (Control Board) DIP Switches on the      DD-61                   | 7-6 |

| Figure 7-6. | Logical Addresses of Disk Drives in a DE-60                                | 7-7 |

| Figure 7-7. | DD-61 Circuit Board Locations                                              | 7-8 |

| Figure 7-8. | DD-61 Physical Head Locations in the HDA                                   | 7-9 |

| Figure 8-1. | DD-61 Sector Format                                                        | 8-2 |

| Figure 8-2. | DD-61 ID Field Format                                                      | 8-3 |

| Figure 8-3. | Defect Parameter and Actual Flaw Locations in a DD-61 Data Field           | 8-5 |

| Figure 8-4. | DD-61 Sector with a Hideable Flaw                                          | 8-6 |

| Figure 9-1. | Rear Panel of a DD-62 Disk Drive                                           | 9-1 |

| Figure 9-2. | Rear Panel DIP Switch 1 (SW1)                                              | 9-2 |

| Figure 9-3. | Rear Panel DIP Switch 2 (SW2)                                              | 9-4 |

| Figure 9-4. | Top Panel DIP Switch 3 (SW3)                                               | 9-5 |

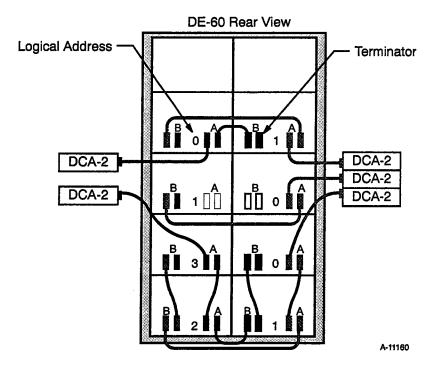

| Figure 9-5.   | Logical Addresses of DCA-2 Drives in a DE-60                               | . 9-6 |

|---------------|----------------------------------------------------------------------------|-------|

| Figure 9-6.   | Top Panel Jumpers on the DD-62                                             | 9-7   |

| Figure 9-7.   | DD-62 and RD-62 Circuit Board Locations                                    | 9-8   |

| Figure 9-8.   | DD/RD-62 Physical Head Locations in the HDA                                | 9-9   |

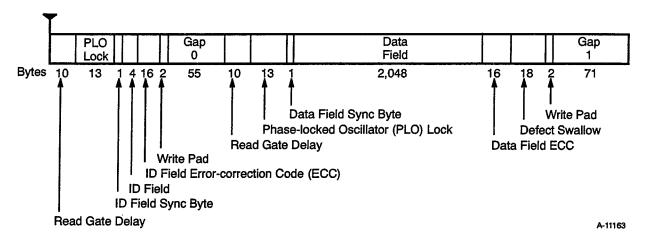

| Figure 10-1.  | DD-62 and RD-62 Physical Sector Format                                     | 10-2  |

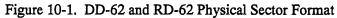

| Figure 10-2.  | DD-62 and RD-62 Logical ID Information                                     | 10-4  |

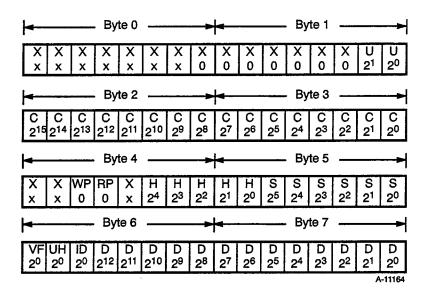

| Figure 10-3.  | DD-62 and RD-62 Physical ID Fields                                         | 10-5  |

| Figure 10-4.  | Defect Parameter and Actual Flaw Locations in a DD-62 and RD-62 Data Field | 10-6  |

| Figure 10-5.  | Bytes 0 and 1 of the Physical Defect Pad                                   | 10-7  |

| Figure 10-6.  | DD-62 and RD-62 Physical Sector with a Hideable Flaw                       | 10-8  |

| Figure 10-7.  | Two Physical Sectors with Hideable Flaws Covered by One Defect Pad         | 10-9  |

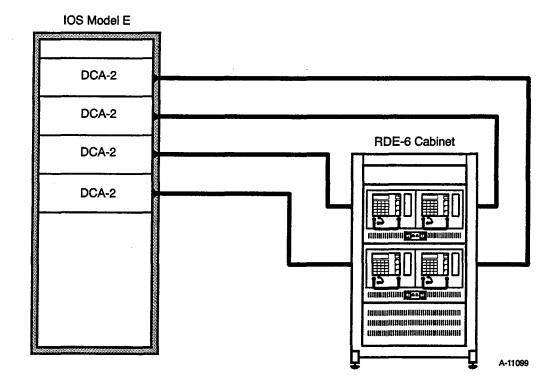

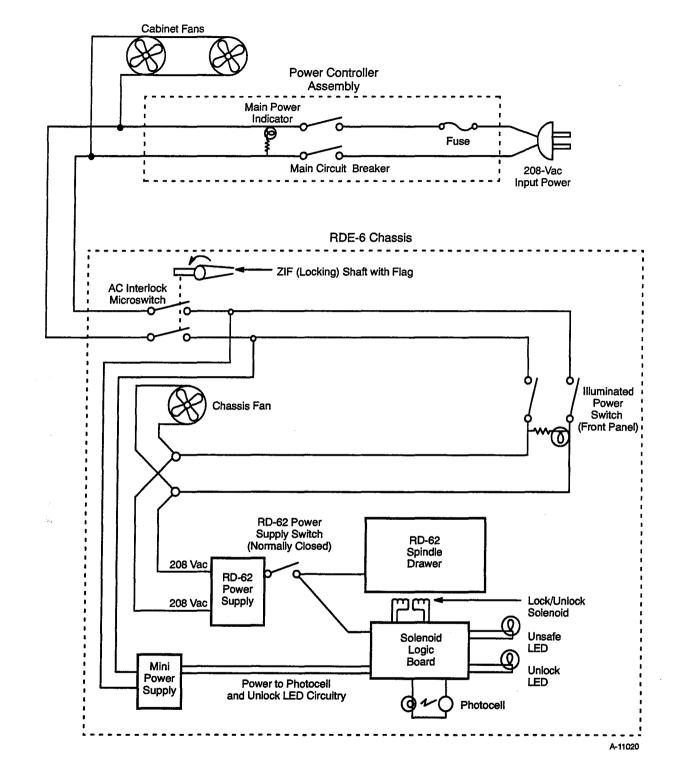

| Figure 11-1.  | RD-62 Cabling Configuration                                                | 11-1  |

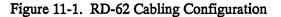

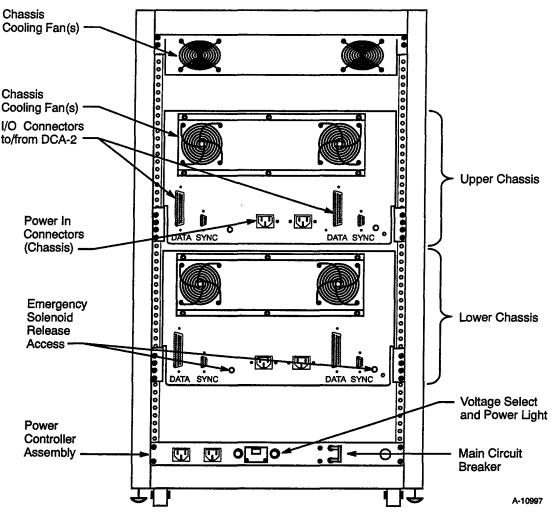

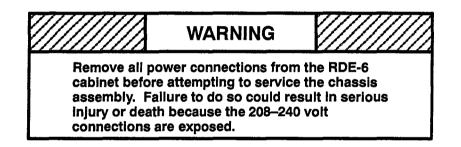

| Figure 11-2.  | RDE-6 Cabinet                                                              | 11-2  |

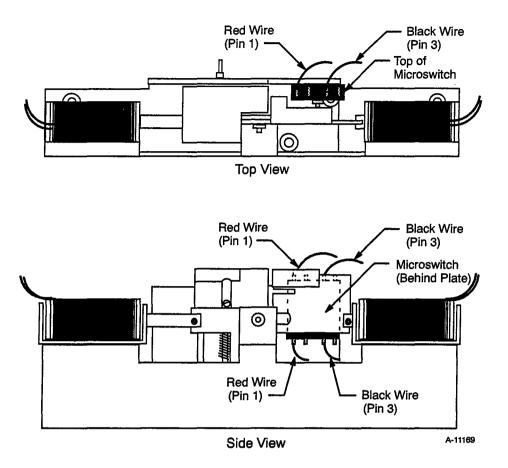

| Figure 11-3.  | RDE-6 Chassis Interlock Switches and Indicators                            | 11-5  |

| Figure 11-4.  | RDE-6 Cabinet (Rear)                                                       | 11-6  |

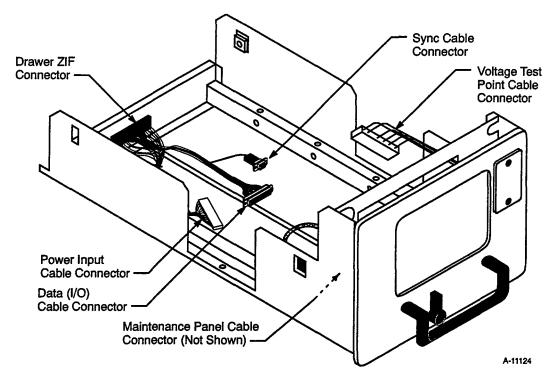

| Figure 11-5.  | RD-62 Drawer Assembly (not including spindle)                              | 11-12 |

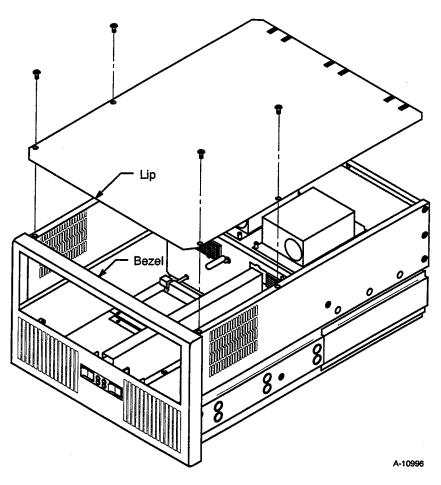

| Figure 11-6.  | RDE-6 Chassis Top Cover Removal                                            | 11-15 |

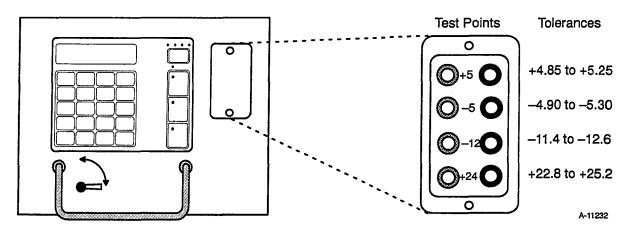

| Figure 11-7.  | RD-62 Voltage Test Points                                                  | 11-17 |

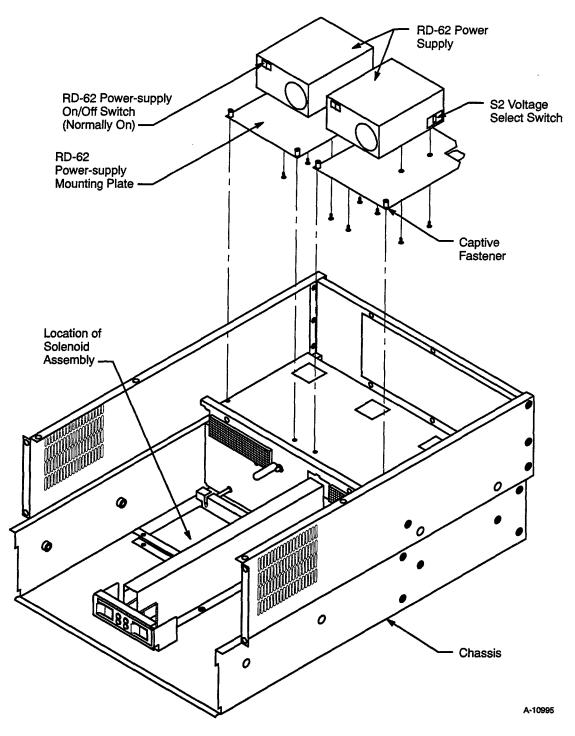

| Figure 11-8.  | RD-62 Power-supply Positions                                               | 11-18 |

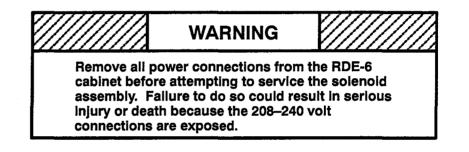

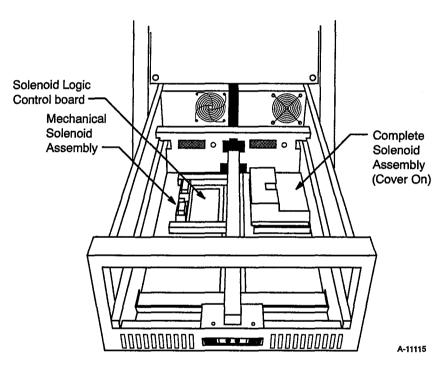

| Figure 11-9.  | RDE-6 Solenoid Assemblies                                                  | 11-19 |

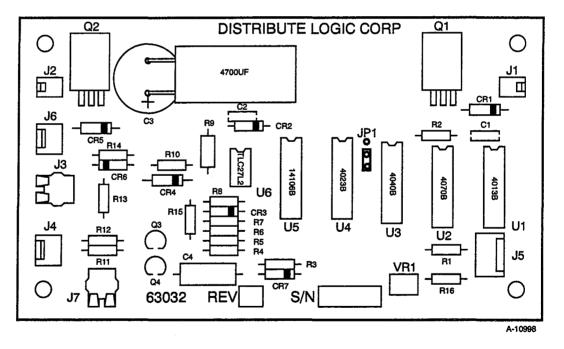

| Figure 11-10. | Solenoid Logic Control Board                                               | 11-20 |

| Figure 11-11. | Mechanical Solenoid Assembly                                               | 11-22 |

| Figure 12-1.  | OLHPA Error Report                                                         | 12-1  |

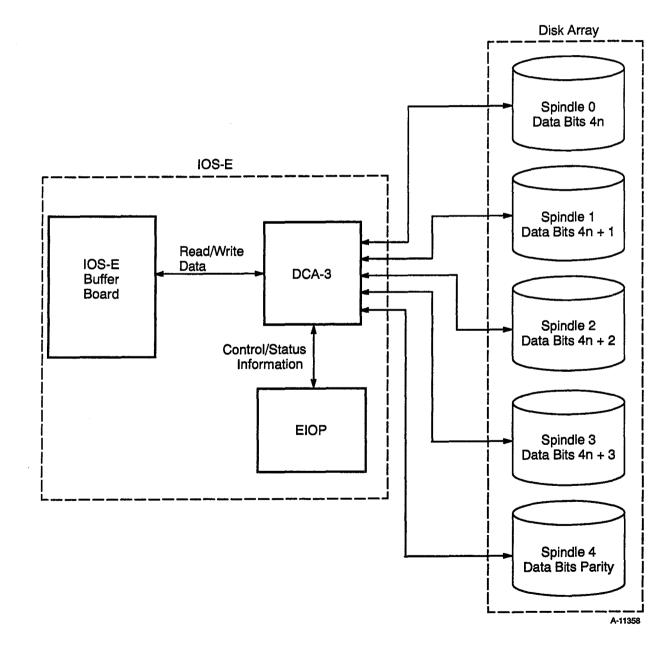

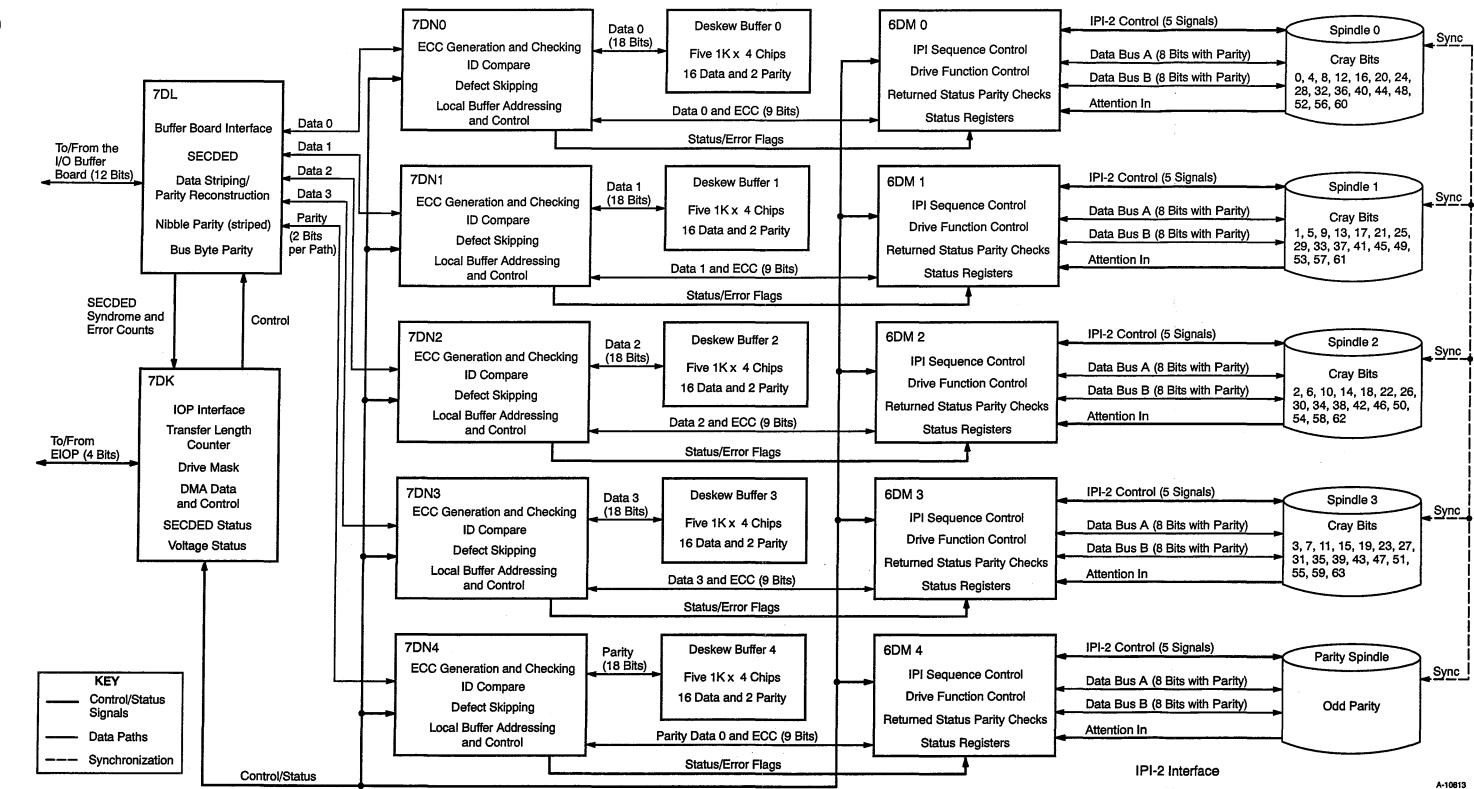

| Figure 13-1.  | Block Diagram of DCA-3 to Disk Array<br>Interface                          | 13-1  |

| Figure 13-2.  | DCA-3 Block Diagram                                                        | 13-5  |

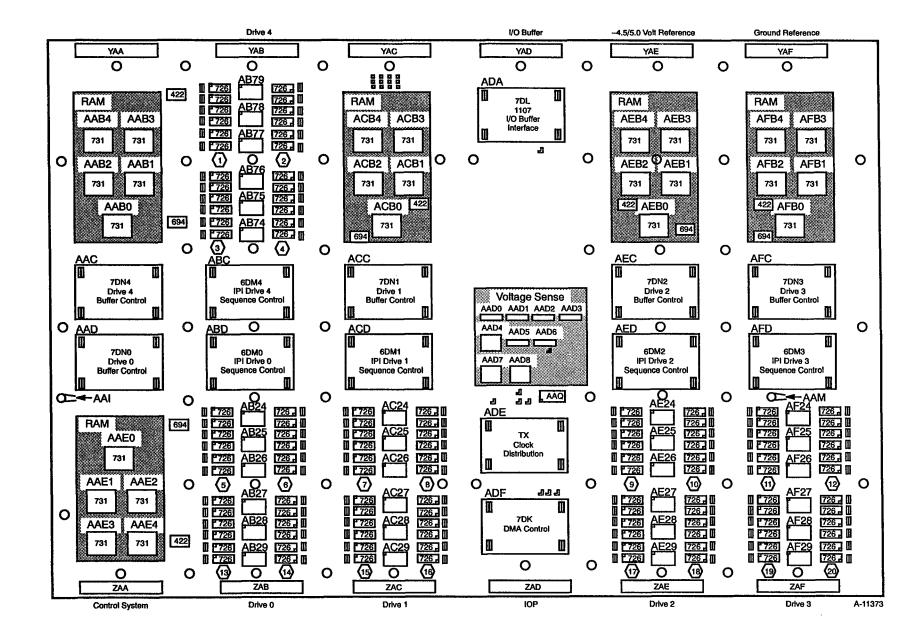

| Figure 13-3.  | DCA-3 Board Assembly                                                       | 13-12 |

| Figure 14-1.  | EIOP Instruction d Field or EIOP B Register                                | 14-2  |

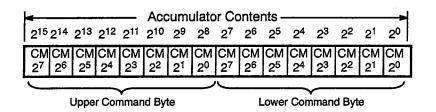

| Figure 14-2.  | DCA3:1 Accumulator Contents for Drive<br>Response        | .14-3 |

|---------------|----------------------------------------------------------|-------|

| Figure 14-3.  | DCA3:1 Accumulator Contents for Drive<br>Command         | 14-4  |

| Figure 14-4.  | ID Parameter 0 Format                                    | 14-4  |

| Figure 14-5.  | ID Parameter 1 Format                                    | 14-5  |

| Figure 14-6.  | Transfer Count Format                                    | 14-5  |

| Figure 14-7.  | DCA3:3 Parameter 1 Control Parcel                        | 14-6  |

| Figure 14-8.  | Current Local Memory Address Format                      | 14-9  |

| Figure 14-9.  | Inverted Parcel Count Format                             | 14-9  |

| Figure 14-10. | Local Memory Starting Address Format                     | 14-14 |

| Figure 14-11. | Parcel Count Format                                      | 14-14 |

| Figure 14-12. | Control Register Values                                  | 14-15 |

| Figure 14-13. | DCA3:17 Control Parcel (Even Channel)                    | 14-16 |

| Figure 14-14. | DCA3:17 Control Parcel (Odd Channel)                     | 14-16 |

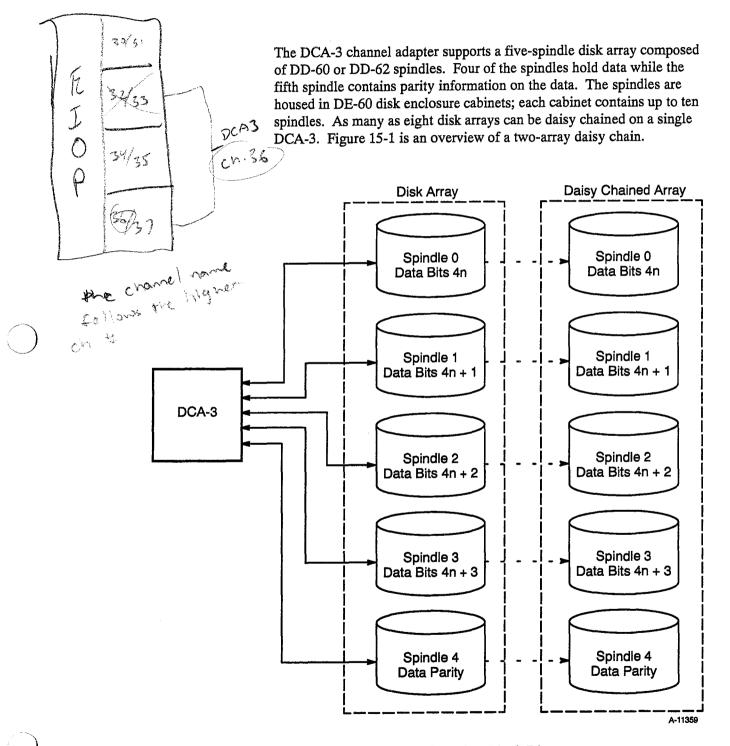

| Figure 15-1.  | Disk Array Overview Block Diagram                        | 15-1  |

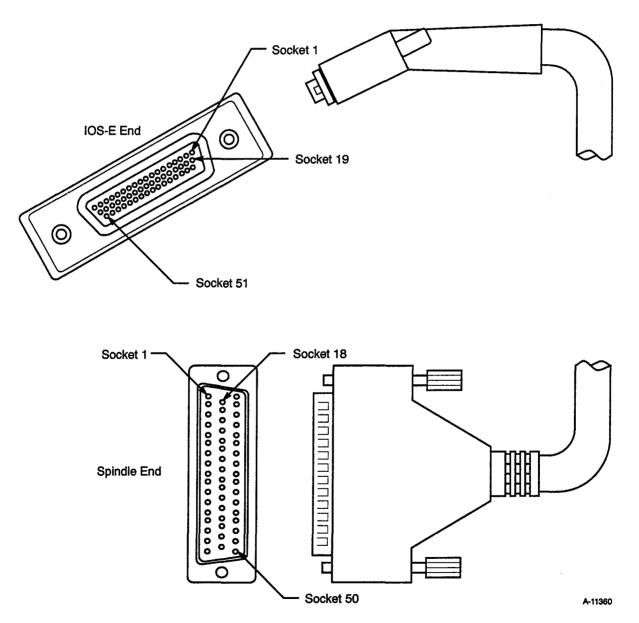

| Figure 15-2.  | DCA-3-to-spindle Data Cable                              | 15-4  |

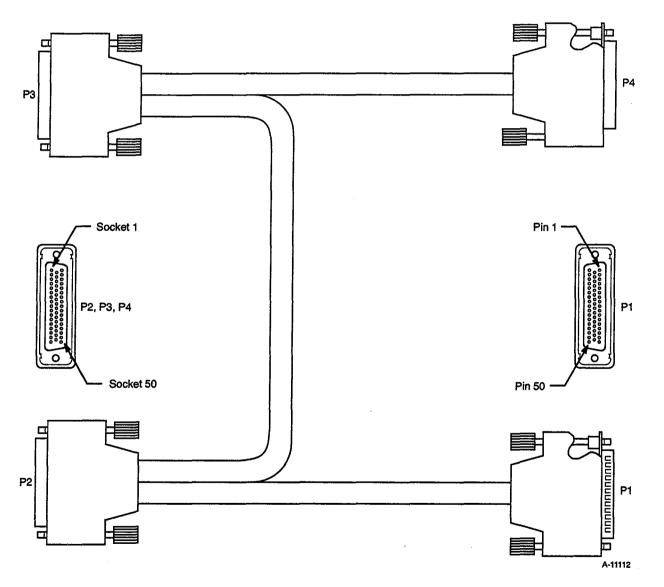

| Figure 15-3.  | 2X Daisy Chain Cable                                     | 15-6  |

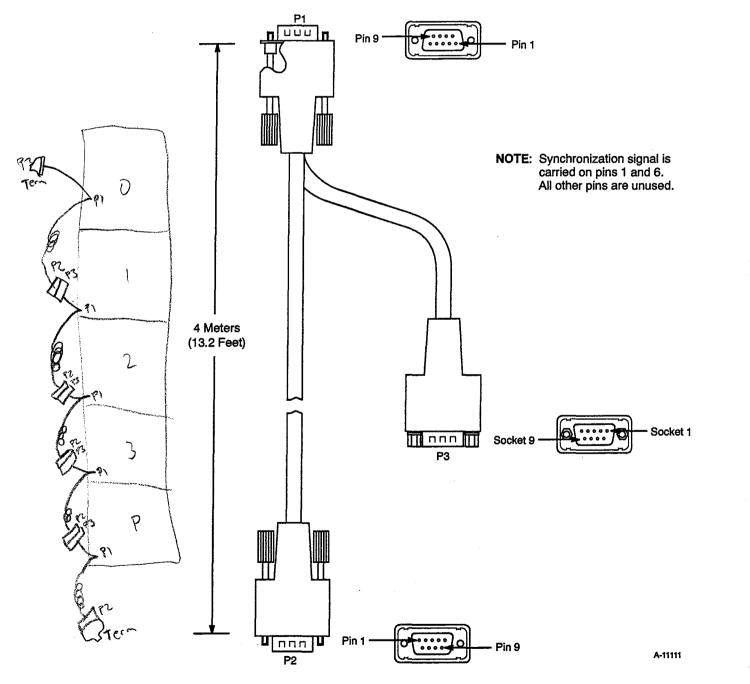

| Figure 15-4.  | Synchronization (Sync) Cable                             | 15-8  |

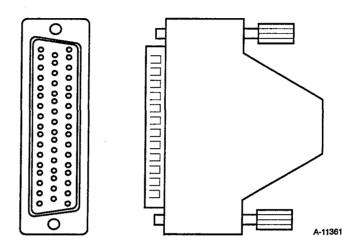

| Figure 15-5.  | Data Cable Terminator for 60 Series Disk                 | 15-9  |

| Eiguro 15 6   | Arrays                                                   | 15-9  |

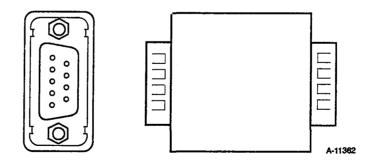

| Figure 15-6.  | Sync Cable Terminator for 60 Series Disk<br>Arrays       | 15-9  |

| Figure 15-7.  | DCA-3 Bulkhead Connections for 700 Series                |       |

|               | IOS-E                                                    | 15-11 |

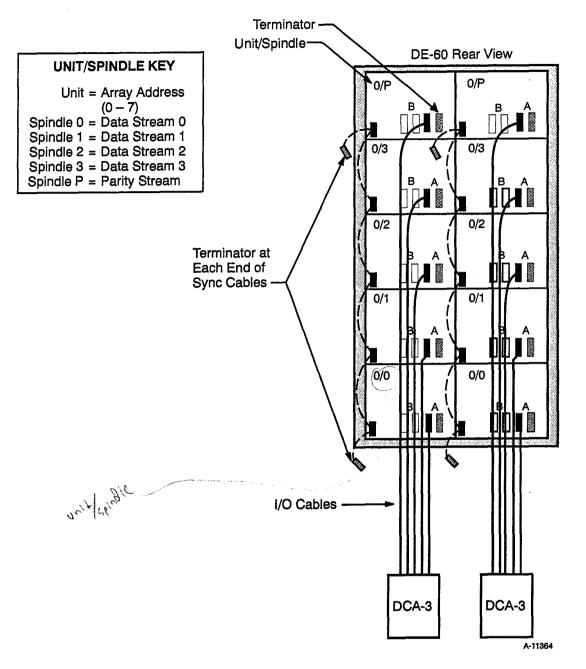

| Figure 15-8.  | Single-array Cabling (2 Channels Shown)                  | 15-15 |

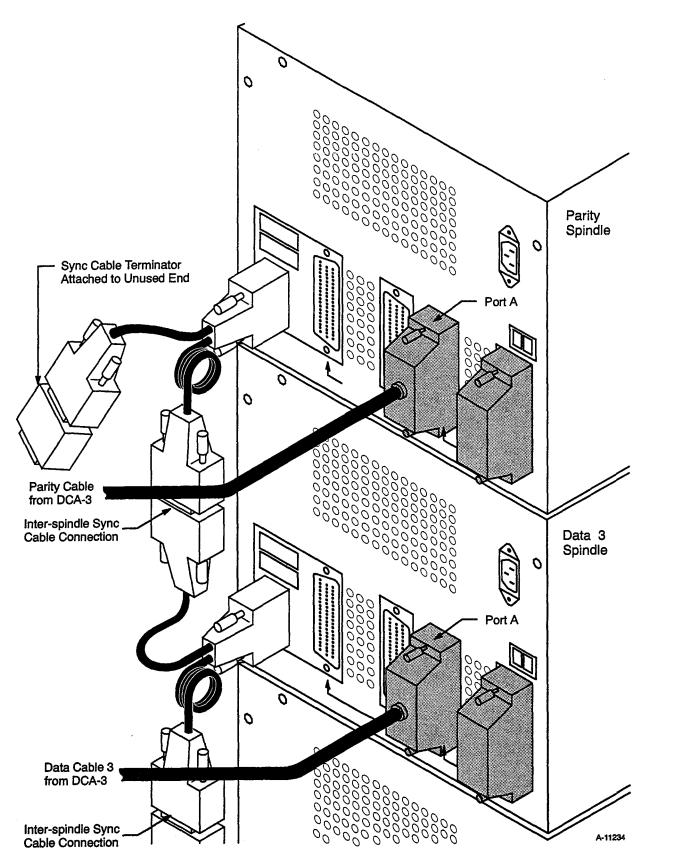

| Figure 15-9.  | Single-array Cable Connections                           | 15-16 |

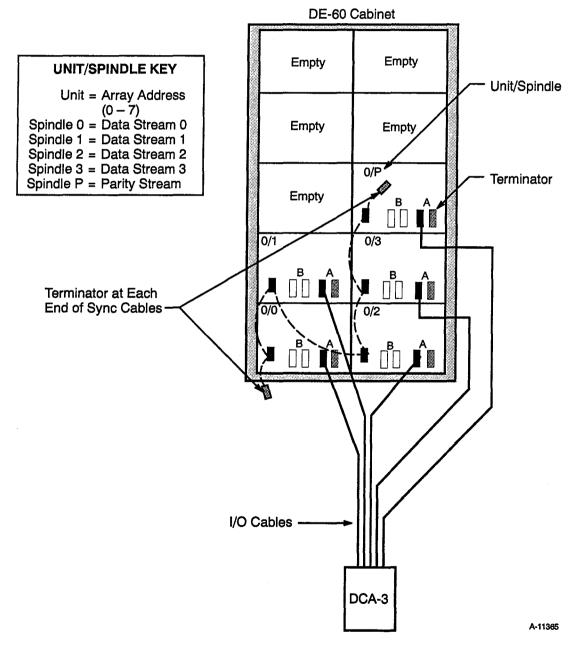

| Figure 15-10. | Single-array Cabling (Partially Populated Cabinet)       | 15-17 |

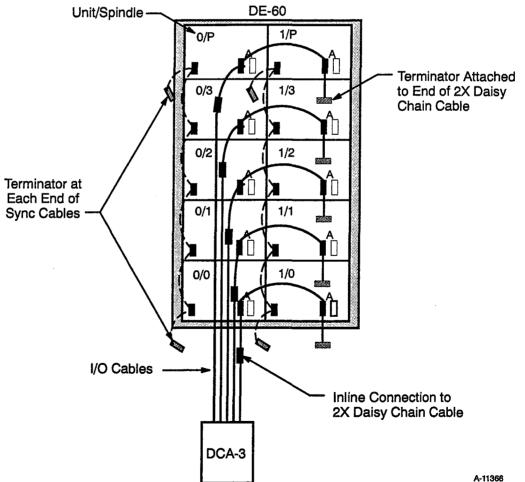

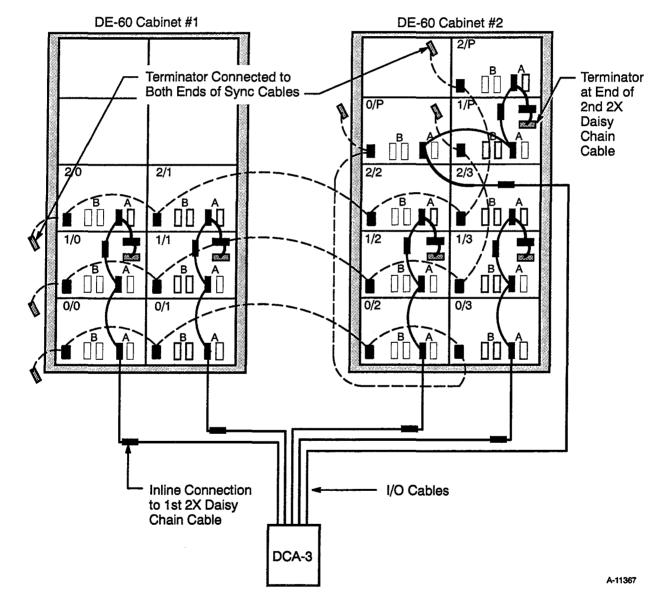

| Figure 15-11. | Single-channel, Two-array Daisy Chain                    | 15-18 |

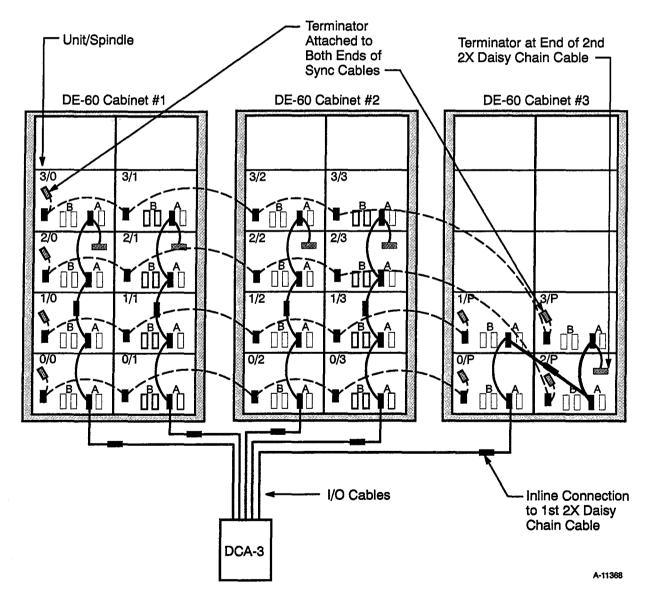

| Figure 15-12. | Single-channel, Three-array Daisy Chain<br>Configuration | 15-19 |

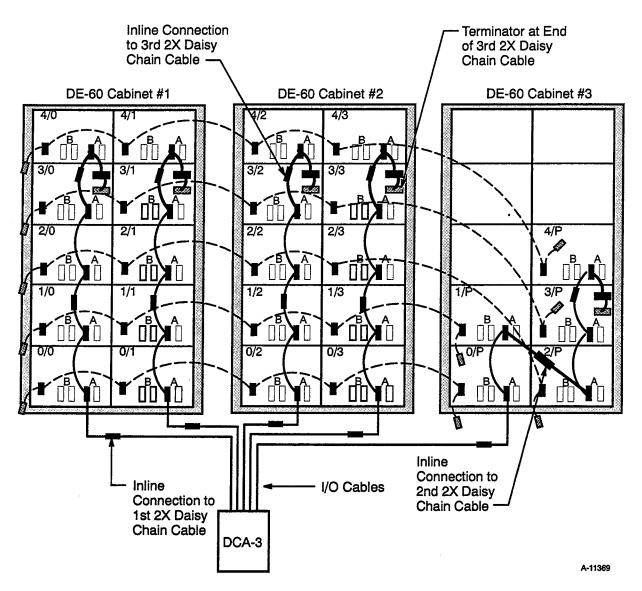

| Figure 15-13. | Single-channel, Four-array Daisy Chain<br>Configuration  | 15-20 |

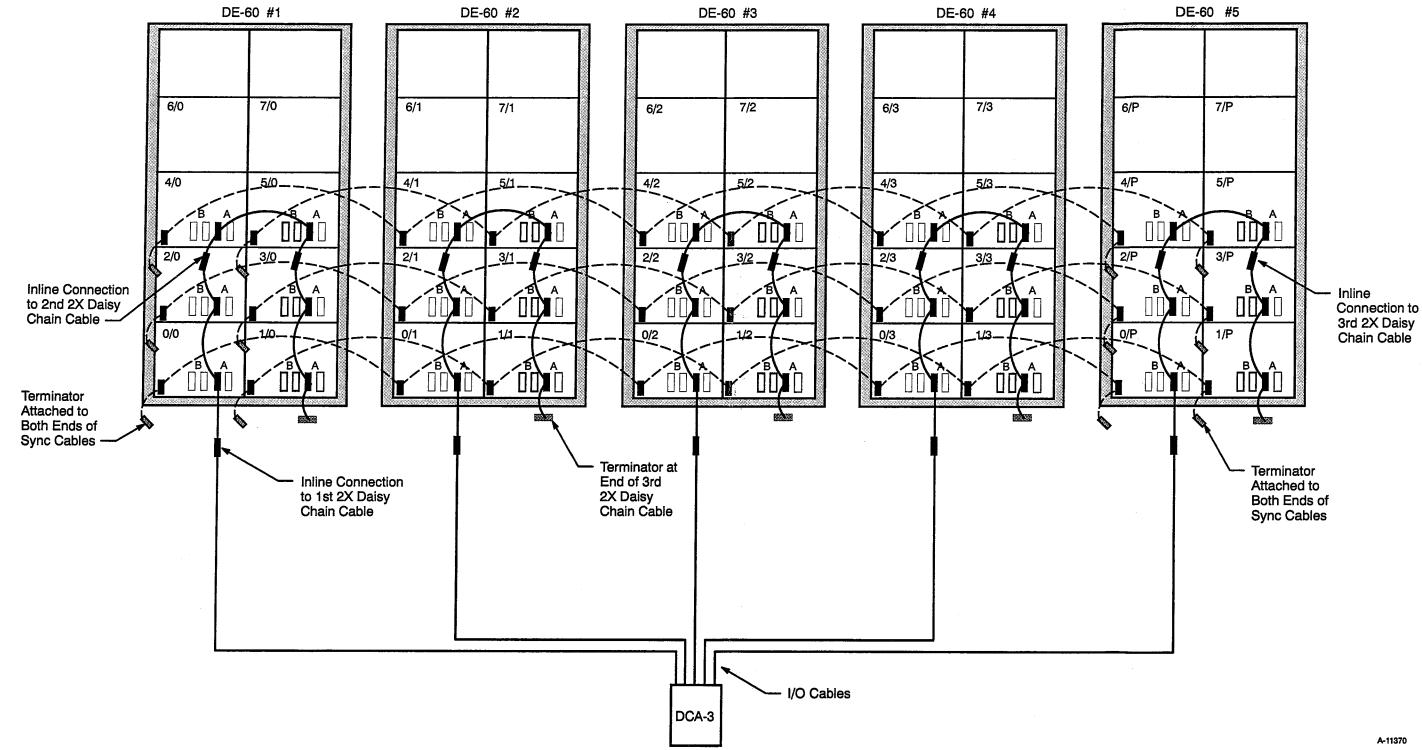

| Figure 15-14. | Single-channel, Five-array Daisy Chain                                                         |       |

|---------------|------------------------------------------------------------------------------------------------|-------|

|               | Configuration                                                                                  | 15-21 |

| Figure 15-15. | Single-channel, Six-array Daisy Chain                                                          | 15-25 |

| Figure 15-16. | Four-channel, Eight-array Configuration with no<br>Alternate Path or Disk Enclosure Resiliency | 15-27 |

| Figure 15-17. | Four-channel, Eight-array Configuration with<br>Alternate Path and Disk Enclosure Resiliency   | 15-29 |

| Figure 16-1.  | ERRPT error display (sheet 1 of 2)                                                             | 16-1  |

| Figure 16-2.  | OLHPA Error Report (Sheet 1 of 2)                                                              | 16-3  |

| Figure 17-1.  | Maintenance Panel                                                                              | 17-3  |

| Figure 17-2.  | DD-60 Read/Write Circuit Board Locations                                                       | 17-13 |

| Figure 17-3.  | Lower DIP Switch (S2) Settings on the DD-60                                                    | 17-14 |

| Figure 17-4.  | Example of pddconf command output                                                              | 17-15 |

| Figure 17-5.  | Example of pddconf command output                                                              | 17-19 |

\_\_\_\_\_

TABLES

| Table 1-1. | DD-60, DD-61, DD-62, and RD-62                              |             |

|------------|-------------------------------------------------------------|-------------|

|            | Characteristics                                             | 1-4         |

| Table 1-2. | Characteristics of a Fully Loaded DE-60                     | 1-6         |

| Table 1-3. | Characteristics of a Fully Loaded RDE-6                     | 1 <b>-8</b> |

| Table 1-4. | DA-60 and DA-62 Characteristics                             | 1-12        |

| Table 2-1. | 60 Series Disk Systems Cable Descriptions                   | 2-1         |

| Table 2-2. | DCA-2 to Disk Drive Cable Socket Definitions                | 2-5         |

| Table 2-3. | Daisy Chain Cable Pin and Socket Definitions                | 2-7         |

| Table 2-4. | Comparison of 60 Series Disk Drive<br>Configurations        | 2-10        |

| Table 3-1. | Bus A and Bus B Contents for Each IPI Bus State<br>Sequence | 3-13        |

| Table 3-2. | Disk Drive Address on Bus A                                 | 3-14        |

| Table 3-3. | Drive Select Response on Bus B                              | 3-15        |

| Table 3-4. | Bus Control Command on Bus A                                | 3-16        |

| Table 3-5. | Sample Bus Control Commands Used by CRI                     | 3-17        |

| Table 3-6. | Bus Control Response on Bus B                               | 3-17        |

| Table 3-7.                                           | Controller Status on Bus A                    | 3-26 |  |  |  |

|------------------------------------------------------|-----------------------------------------------|------|--|--|--|

| Table 3-8.                                           | Sample Controller Statuses                    | 3-27 |  |  |  |

| Table 3-9.                                           | Drive Ending Status on Bus B                  | 3-27 |  |  |  |

| Table 3-10.    Sample Drive Ending Statuses          |                                               |      |  |  |  |

| Table 3-11.                                          | Interrupt Request on Bus A                    | 3-29 |  |  |  |

| Table 3-12.                                          | Drive Select Response on Bus B                | 3-29 |  |  |  |

| Table 3-13.                                          | Selective Reset on Bus A                      | 3-30 |  |  |  |

| Table 3-14.                                          | Master Reset on Bus A                         | 3-31 |  |  |  |

| Table 3-15.                                          | Transfer Settings Request on Bus A            | 3-32 |  |  |  |

| Table 3-16.                                          | Transfer Settings on Bus B                    | 3-32 |  |  |  |

| Table 3-17.                                          | Drive Interrupt Request on Bus A              | 3-33 |  |  |  |

| Table 3-18.                                          | Drive Interrupts on Bus B                     | 3-33 |  |  |  |

| Table 4-1.                                           | Channel Functions                             | 4-1  |  |  |  |

| Table 4-2.                                           | Function Modifier Bits                        | 4-3  |  |  |  |

| Table 4-3.                                           | Sequencer Mode Bits                           | 4-13 |  |  |  |

| Table 4-4.         RPS Parameter Parcel Descriptions |                                               |      |  |  |  |

| Table 5-1.                                           | Upper DIP Switch Settings for Logical Address | 5-3  |  |  |  |

| Table 5-2.                                           | Four-LED Display Description                  | 5-7  |  |  |  |

| Table 6-1.                                           | DD-60 Cylinder Map                            | 6-1  |  |  |  |

| Table 6-2.                                           | DD-60 Sector Field Sizes                      | 6-2  |  |  |  |

| Table 6-3.                                           | DD-60 Logical ID Information Description      | 6-4  |  |  |  |

| Table 6-4.                                           | User Flaw Table Format                        | 6-11 |  |  |  |

| Table 7-1.                                           | Top Panel Jumper Descriptions                 | 7-4  |  |  |  |

| Table 7-2.                                           | Top Panel LED Descriptions                    | 7-5  |  |  |  |

| Table 7-3.                                           | Upper DIP Switch Settings for Logical Address | 7-7  |  |  |  |

| Table 8-1.                                           | DD-61 Cylinder Map                            | 8-1  |  |  |  |

| Table 8-2.                                           | DD-61 Logical ID Information Description      | 8-3  |  |  |  |

| Table 8-3.                                           | User Flaw Table Format                        | 8-8  |  |  |  |

| Table 9-1.                                           | SW3 DIP Switch Settings for Logical Address   | 9-6  |  |  |  |

| Table 9-2.                                           | Top Panel Jumper Descriptions                 | 9-7  |  |  |  |

| Table 10-1.                                          | DD-62 and RD-62 Cylinder Map                  | 10-1 |  |  |  |

| Table 10-2.                                          | DD-62 and RD-62 Sector Field Sizes            | 10-2 |  |  |  |

| Table 10-3.  | DD-62 and RD-62 Logical ID Information |       |  |  |  |

|--------------|----------------------------------------|-------|--|--|--|

|              | Description                            | 10-4  |  |  |  |

| Table 10-4.  | User Flaw Table Format                 |       |  |  |  |

| Table 11-1.  | RDE-6 Indicators                       |       |  |  |  |

| Table 11-2.  | RDE-6 Switches                         |       |  |  |  |

| Table 11-3.  | RDE-6 and RD-62 Parts List             |       |  |  |  |

| Table 12-1.  | Status Name Cross-reference Chart      |       |  |  |  |

| Table 12-2.  | General Status                         |       |  |  |  |

| Table 12-3.  | 6X Condition Bits Status               | 12-4  |  |  |  |

| Table 12-4.  | 7X Condition Bits Status               | 12-5  |  |  |  |

| Table 12-5.  | Adapter Status                         | 12-6  |  |  |  |

| Table 12-6.  | Syndrome Status                        | 12-7  |  |  |  |

| Table 12-7.  | Transfer Count Status                  | 12-7  |  |  |  |

| Table 12-8.  | Tag Status                             | 12-8  |  |  |  |

| Table 12-9.  | Drive Ending Status                    |       |  |  |  |

| Table 12-10. | Disk Drive Status on Bus B             | 12-10 |  |  |  |

| Table 12-11. | ID Parameter 0 Status                  | 12-10 |  |  |  |

| Table 12-12. | ID Parameter 1 Status                  |       |  |  |  |

| Table 12-13. | Exception Status (Byte 0)              |       |  |  |  |

| Table 12-14. | Unsolicited Exceptions Status (Byte 1) | 12-13 |  |  |  |

| Table 12-15. | Bus Control Exceptions Status (Byte 2) | 12-13 |  |  |  |

| Table 12-16. | Drive Exceptions Status (Byte 3)       | 12-14 |  |  |  |

| Table 12-17. | Drive Exceptions Status (Byte 4)       | 12-14 |  |  |  |

| Table 12-18. | Drive Exceptions Status (Byte 5)       | 12-15 |  |  |  |

| Table 12-19. | Drive Exceptions Status (Byte 6)       | 12-15 |  |  |  |

| Table 12-20. | Drive Exceptions Status (Byte 7)       | 12-16 |  |  |  |

| Table 12-21. | Interface Flags Status (Byte 0)        | 12-16 |  |  |  |

| Table 12-22. | Data Received Flags Status (Byte 1)    | 12-17 |  |  |  |

| Table 12-23. | Data Control Flags Status (Byte 2)     | 12-17 |  |  |  |

| Table 12-24. | Disk Drive Status (Byte 3)             | 12-17 |  |  |  |

| Table 12-25. | Disk Drive Alarms Status (Byte 4)      | 12-18 |  |  |  |

| Table 12-26. | Vendor-defined Status (Byte 5)         | 12-18 |  |  |  |

|              |                                        |       |  |  |  |

| Table 12-27. | Vendor-defined Status (Byte 6)                                   | 12-18 |  |  |

|--------------|------------------------------------------------------------------|-------|--|--|

| Table 12-28. | . Head Skew Status (Byte 7)                                      |       |  |  |

| Table 12-29. | OLHPA Flaw Location Information                                  | 12-19 |  |  |

| Table 12-30. | DD-60 Rear Panel Display I/O Status                              | 12-19 |  |  |

| Table 13-1.  | DCA-3 Disk Array Data Striping                                   | 13-4  |  |  |

| Table 13-2.  | DCA-3 to DA-60 Data Bit Distribution                             | 13-10 |  |  |

| Table 13-3.  | DCA-3 to DA-62 Data Bit Distribution                             | 13-11 |  |  |

| Table 14-1.  | DCA-3 Channel Functions                                          | 14-1  |  |  |

| Table 14-2.  | DCA3:1 Function Modifier Bits                                    | 14-3  |  |  |

| Table 14-3.  | DCA-3 Transfer Counts                                            | 14-6  |  |  |

| Table 14-4.  | DCA3:5 Device Function Descriptions                              | 14-7  |  |  |

| Table 14-5.  | DCA3:12 Status Parcels                                           | 14-10 |  |  |

| Table 14-6.  | DCA3:13 Status Parcels                                           | 14-13 |  |  |

| Table 14-7.  | Sample Bus Control Commands Used by CRI                          | 14-15 |  |  |

| Table 15-1.  | Disk Array Cabling Components                                    | 15-3  |  |  |

| Table 15-2.  | DCA-3-to-spindle Data Cable Socket Definitions                   | 15-5  |  |  |

| Table 15-3.  | 2X Daisy Chain Cable Pin and Socket Definitions                  | 15-7  |  |  |

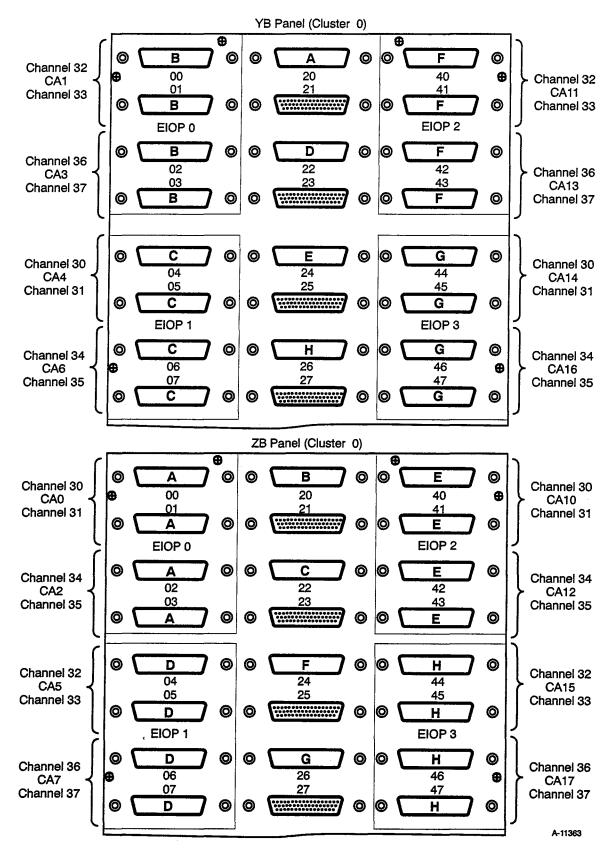

| Table 15-4.  | DCA-3 Bulkhead Connections for 700 Series<br>Chassis (Cluster 0) | 15-10 |  |  |

| Table 15-5.  | Disk Array Cabling Hardware Requirements                         | 15-12 |  |  |

| Table 16-1.  | Status Name Cross-reference Chart                                | 16-5  |  |  |

| Table 16-2.  | General Status                                                   | 16-6  |  |  |

| Table 16-3.  | Interrupt Status Bits                                            | 16-7  |  |  |

| Table 16-4.  | SECDED Status Bits                                               | 16-8  |  |  |

| Table 16-5.  | Transfer Count Status Bits                                       | 16-9  |  |  |

| Table 16-6.  | IPI Tag Status Bits                                              | 16-10 |  |  |

| Table 16-7.  | Busy Status Bits                                                 | 16-10 |  |  |

| Table 16-8.  | Done Status Bits                                                 | 16-11 |  |  |

| Table 16-9.  | DMA Acknowledge-pending Status Bits                              | 16-11 |  |  |

| Table 16-10. | Drive Ending Status                                              | 16-12 |  |  |

| Table 16-11. | Ending Status Byte Definitions                                   | 16-13 |  |  |

| Table 16-12. | ID Parameter 0 Status                                 | 16-14 |  |  |

|--------------|-------------------------------------------------------|-------|--|--|

| Table 16-13. | ID Parameter 1 Status                                 |       |  |  |

| Table 16-14. | Bus A and Bus B Data                                  |       |  |  |

| Table 16-15. | Exception Status (Byte 0)                             | 16-16 |  |  |

| Table 16-16. | Unsolicited Exceptions Status (Byte 1)                |       |  |  |

| Table 16-17. | Bus Control Exceptions Status (Byte 2)                |       |  |  |

| Table 16-18. | Drive Exceptions Status (Byte 3)                      | 16-17 |  |  |

| Table 16-19. | Drive Exceptions Status (Byte 4)                      | 16-17 |  |  |

| Table 16-20. | Drive Exceptions Status (Byte 5)                      | 16-18 |  |  |

| Table 16-21. | Drive Exceptions Status (Byte 6)                      | 16-18 |  |  |

| Table 16-22. | Drive Exceptions Status (Byte 7)                      | 16-19 |  |  |

| Table 16-23. | Interface Flags Status (Byte 0)                       | 16-19 |  |  |

| Table 16-24. | able 16-24. Data Received Flags Status (Byte 1)       |       |  |  |

| Table 16-25. | Cable 16-25.       Data Control Flags Status (Byte 2) |       |  |  |

| Table 16-26. | Disk Drive Status (Byte 3)                            | 16-21 |  |  |

| Table 16-27. | Disk Drive Alarms Status (Byte 4)                     | 16-21 |  |  |

| Table 16-28. | Vendor-defined Status (Byte 5)                        | 16-22 |  |  |

| Table 16-29. | Vendor-defined Status (Byte 6)                        | 16-22 |  |  |

| Table 16-30. | Head Skew Status (Byte 7)                             | 16-22 |  |  |

| Table 16-31. | OLHPA Flaw Location Information                       | 16-22 |  |  |

| Table 16-32. | DD-60 Rear Panel Display I/O Status                   | 16-23 |  |  |

| Table 17-1.  | Maintenance Panel Switches and Displays               | 17-4  |  |  |

| Table 17-2.  | 60 Series Disk Maintenance Panel Tests                | 17-6  |  |  |

| Table 17-3.  | DD-60 Rear Panel I/O Status Definitions               | 17-17 |  |  |

| Table 17-4.  | DD-62 Maintenance Panel Status Definitions            | 17-17 |  |  |

xxix

# **1** DISK SYSTEM OVERVIEW

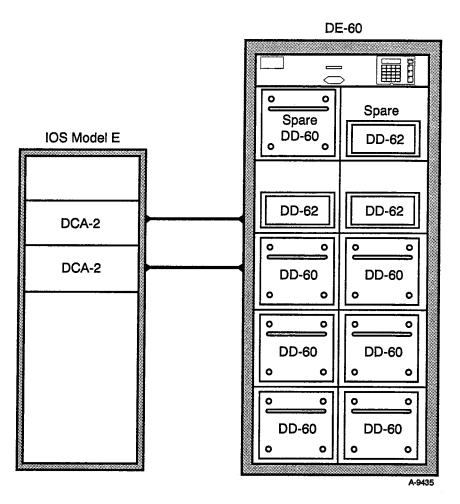

A disk system consists of DD-60, DD-61, and/or DD-62 spindles, a DE-60 disk enclosure, and spare spindle(s). The system connects to an I/O subsystem model E (IOS-E) through a disk channel adapter, either a DCA-2 (for DD-60, DD-61, or DD-62) or a DCA-3 (for the DA-60 or DA-62 disk array).

Figure 1-1 is a block diagram of a 60 series disk system connected to a DCA-2. The DE-60 contains ten disk drives. Three DD-62s (one is a spare DD-62) are connected to one DCA-2, and seven DD-60s (one is a spare DD-60) are connected to another DCA-2.

#### **Disk Drives**

DD-60, DD-61, and DD-62 disk drives provide long-term data storage for a Cray Research, Inc. (CRI) computer system. The DD-60 provides a fast data-transfer rate and the DD-61 and DD-62 provide increased datastorage capacity. The RD-62 provides the same performance capabilities as the DD-62; however, the RD-62 can be removed from the removable disk enclosure (RDE-6) cabinet.

#### **DD-60 Disk Drive**

The DD-60 is a parallel-head storage unit. Its sustained transfer rate ranges from 16 to 20 Mbytes/s, and it has a storage capacity of 1.96 Gbytes.

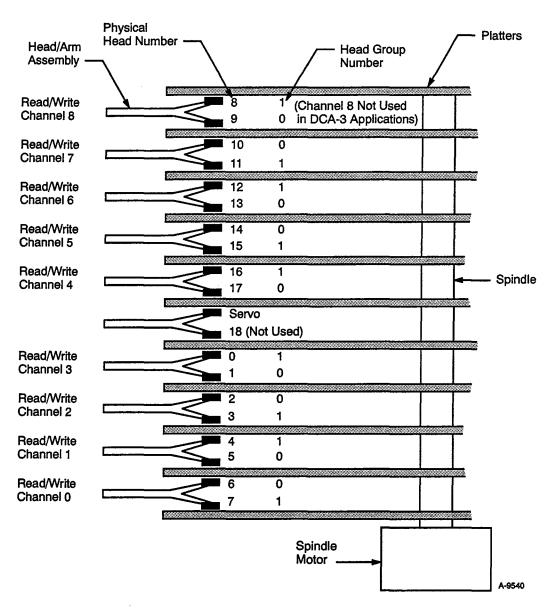

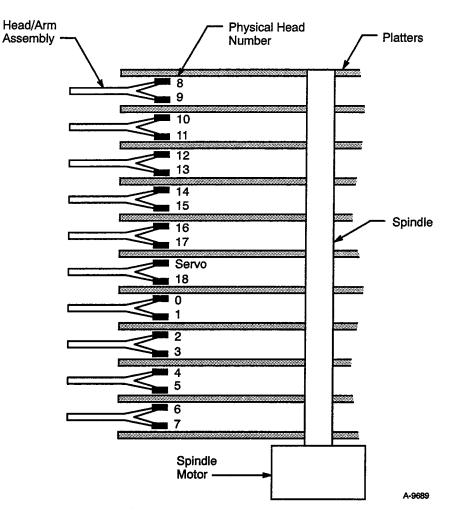

One DD-60 contains two groups of nine parallel read/write heads and one servo head. During data transfers to and from the DCA-2, only one group of heads (0 or 1) is used at a time. Eight of the heads transfer data, while the ninth head transfers a parity bit (the parity head is unused when the disk system is connected to a DCA-3). The servo head transfers head position information to the control circuitry in the DD-60.

A sector of data from a DD-60 contains 2,048 64-bit words of system data. The DCA-2 creates the sector from eight physical sectors in the DD-60 (one from each head). Each physical sector contains 256 64-bit words of data.

A logical track is made from eight physical tracks of data in the DD-60. One track contains 23 sectors where data can be stored and retrieved by the operating system.

Two tracks make up one cylinder. The DD-60 has 2,608 data cylinders, 2 maintenance cylinders, and 1 flaw table cylinder.

#### **DD-61 Disk Drive**

The DD-61 is a serial-head storage unit. It has a sustained transfer rate of 2.6 Mbytes/s and a storage capacity of 2.23 Gbytes.

One DD-61 contains 19 serial read/write heads and one servo head. During data transfers to and from the DCA-2, only one head (0 through 22<sub>8</sub>) is used at a time. The servo head transfers head position information to the control circuitry in the DD-61. DD-61s are not supported by the DCA-3 as a disk array. A sector of data from a DD-61 contains 512 64-bit words of IOP data. Data is transferred between the DD-61 and DCA-2 in blocks of this fixed size. One track contains 11 sectors where data can be stored and retrieved by the IOS-E.

Nineteen tracks make up one cylinder in the DD-61. DD-61s contain 2,608 data cylinders, 2 maintenance cylinders, and 1 flaw table cylinder.

#### DD-62 Disk Drive

The DD-62 is a two-head parallel storage unit. It has a sustained transfer rate of 8.14 Mbytes/s and a storage capacity of 2.73 Gbytes.

One DD-62 contains nine read/write head groups and one servo head. During data transfers to and from the DCA-2, two heads are used at a time. The servo head transfers head position information to the servo control circuitry in the DD-62.

A sector of data from a DD-62 contains 512 64-bit words of IOP data. Data is transferred between the DD-62 and DCA-2 in blocks of this fixed size. Each track contains 28 sectors where data can be stored and retrieved by the IOS-E.

The DCA-2 creates a sector from two physical sectors in the DD-62 (one from each head in the head group). Each physical sector contains one half of an IOP data sector.

Nine logical tracks make up one cylinder in the DD-62. DD-62s contain 2,652 data cylinders, 2 maintenance cylinders, and 1 flaw table cylinder.

#### **RD-62 Disk Drive**

The RD-62 is a two-head parallel storage unit that is identical to the DD-62 in performance. It has a sustained transfer rate of 8.14 Mbytes/s and a storage capacity of 2.73 Gbytes.

The RD-62 is housed in an RDE-6 enclosure that enables individual drives to be easily removed and replaced by the customer. The RDE-6 enclosure contains up to four RD-62s. Connections to the RD-62s are made through a bulkhead on the RDE-6 cabinet. Because of the limitations of the RDE-6 bulkhead, RD-62s do not support daisy chain or alternate-path cabling configurations like the DD-62s. In all other respects, the RD-62 is equivalent to the DD-62.

#### DD-60, DD-61, DD-62, and RD-62 Comparison

DD-60s and DD-61s are Sabre VI disk drives; DD-62s and RD-62s are Sabre VII disk drives. All drives are formatted to CRI specifications. Table 1-1 lists the characteristics of the DD-60, DD-61, DD-62, and RD-62.

#### Table 1-1. DD-60, DD-61, DD-62, and RD-62 Characteristics

| Characteristic                                    | DD-60                                                          | DD-61                                                          | DD-62 and RD-62                                                |

|---------------------------------------------------|----------------------------------------------------------------|----------------------------------------------------------------|----------------------------------------------------------------|

| Spindle type                                      | Sabre VI<br>9 head parallel                                    | Sabre VI<br>19 head serial                                     | Sabre VII<br>2 head parallel                                   |

| Sustained transfer rate                           | 16 – 20 Mbytes/s                                               | 2.3 - 2.6 Mbytes/s                                             | 8.14 Mbytes/s                                                  |

| Burst transfer rate                               | 24 Mbytes/s                                                    | 3.0 Mbytes/s                                                   | 9.34 Mbytes/s                                                  |

| Storage capacity (formatted)                      | 1.96 Gbytes                                                    | 2.23 Gbytes                                                    | 2.73 Gbytes                                                    |

| Heads per drive                                   | 16 data<br>2 parity<br>1 servo                                 | 19 data<br>1 servo                                             | 18 data<br>1 servo                                             |

| Heads active at one time                          | 8 data<br>1 parity                                             | 1 data                                                         | 2 data                                                         |

| Cylinders per drive                               | 0-2,610 (0-5062 <sub>8</sub> )                                 | 0-2,610 (0-5062 <sub>8</sub> )                                 | 0-2,654 (0-51368)                                              |

| Head groups                                       | 0 – 1 (0 – 1 <sub>8</sub> )                                    | 0 – 18 (0 – 22 <sub>8</sub> )                                  | 0-8 (0-10 <sub>8</sub> )                                       |

| Sectors per logical track                         | 0-22 (0-26 <sub>8</sub> )                                      | 0-10 (0-128)                                                   | 0-27 (0-33 <sub>8</sub> )                                      |

| Logical sector size in 64-bit words               | 2,048 CRI words                                                | 512 CRI words                                                  | 512 CRI words                                                  |

| Flaw table cylinder                               | 2,610 (5062 <sub>8</sub> )                                     | 2,610 (5062 <sub>8</sub> )                                     | 2,654 (5136 <sub>8</sub> )                                     |

| Maintenance (CE) cylinder                         | 2,608 (5060 <sub>8</sub> )                                     | 2,608 (5060 <sub>8</sub> )                                     | 2,652 (5134 <sub>8</sub> )                                     |

| Average single track seek time                    | 3 ms                                                           | 3 ms                                                           | 3 ms                                                           |

| Average seek time                                 | 13 ms                                                          | 13 ms                                                          | 12 ms                                                          |

| Full track seek time                              | 26 ms                                                          | 26 ms                                                          | 26 ms                                                          |

| Average latency                                   | 8.3 ms                                                         | 8.3 ms                                                         | 6.87 ms                                                        |

| Rotational speed (nominal)                        | 3,600 rpm                                                      | 3,600 rpm                                                      | 4,365 rpm                                                      |

| Start time<br>(without sequence delay)            | 1 min, 30 s                                                    | 1 min, 30 s                                                    | 1 min, 30 s                                                    |

| Stop time (maximum)                               | 60 s                                                           | 60 s                                                           | 60 s                                                           |

| Single disk drive weight (including power supply) | 55 lbs<br>25 kg                                                | 41 lbs<br>18.6 kg                                              | 40 lbs<br>18.1 kg                                              |

| Actuator type                                     | Balanced rotary                                                | Balanced rotary                                                | Balanced rotary                                                |

| Data coding to/from media                         | Nonreturn to zero<br>(NRZ) / 2 – 7 run<br>length limited (RLL) | Nonreturn to zero<br>(NRZ) / 2 – 7 run<br>length limited (RLL) | Nonreturn to zero<br>(NRZ) / 1 – 7 run<br>length limited (RLL) |

| Type of interface                                 | Intelligent peripheral<br>interface-2 (IPI-2)                  | Intelligent peripheral<br>interface-2 (IPI-2)                  | Intelligent peripheral<br>interface-2 (IPI-2)                  |

## **DE-60 Disk Enclosure**

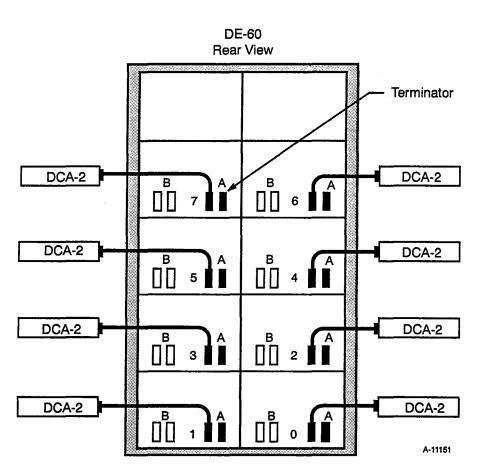

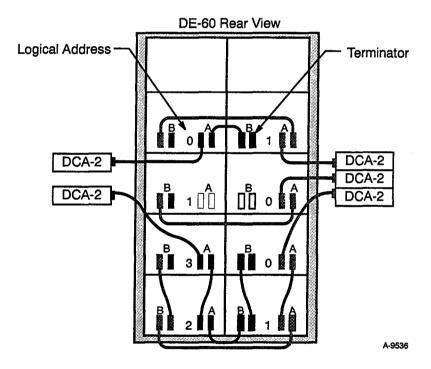

The DE-60 disk enclosure houses combinations of one to ten DD-60, DD-61, and DD-62 disk drives. For example, Figure 1-2 shows a DE-60 with six DD-60s, two DD-62s, one spare DD-62, and one spare DD-60. In addition to the disk drives, the DE-60 contains a terminal block, cooling fan(s), and a maintenance panel.

Figure 1-2. Front and Rear Views of the DE-60

The terminal block and voltage switch connect each drive to one of the three-phase loads. A delta output is configured for a 400-Vac input, and a wye output is used for 208-Vac input power. Power cords connect the terminal block to each disk drive and are cut to length for each position in the cabinet. The power cords are numbered as shown in Figure 1-2.

. .

The cooling fan(s) transfer exhaust air from the disk drives to the computer room. The exhaust air exits the rear of the disk drives, moves through the cooling fans, and leaves the DE-60 through a vent in the top of the cabinet.

The maintenance panel is used to run disk drive diagnostics. Refer to the "Maintenance Procedures" section of this manual for more information on the maintenance panel.

The characteristics of a fully loaded DE-60 vary depending on the number of DD-60s, DD-61s, or DD-62s it contains. Table 1-2 compares physical characteristics of a DE-60 with ten DD-60s, DD-61s, or DD-62s installed.

| Characteristic                                                                               | Ten DD-60s                                                                                          | Ten DD-61s                                                                                             | Ten DD-62s                                                                                         |  |

|----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|--|

| Height                                                                                       | 61.75 in. (157 cm)                                                                                  | 61.75 in. (157 cm)                                                                                     | 61.75 in. (157 cm)                                                                                 |  |

| Width                                                                                        | 24.00 in. (61 cm)                                                                                   | 24.00 in. (61 cm)                                                                                      | 24.00 in. (61 cm)                                                                                  |  |

| Depth                                                                                        | 41.50 in. (105 cm)                                                                                  | 41.50 in. (105 cm)                                                                                     | 41.5 in. (105 cm)                                                                                  |  |

| Floor space                                                                                  | 6.9 ft <sup>2</sup> (0.6 m <sup>2)</sup>                                                            | 6.9 ft <sup>2</sup> (0.6 m <sup>2)</sup>                                                               | 6.9 ft <sup>2</sup> (0.6 m <sup>2)</sup>                                                           |  |

| Weight                                                                                       | 960 lbs (435 kg)                                                                                    | 812 lbs (368 kg)                                                                                       | 810 lbs (367 kg)                                                                                   |  |

| Heat load<br>(8 disk drives)                                                                 | 8,600 Btu/hr<br>(2,520 W)                                                                           | 4,770 Btu/hr<br>(1,400 W)                                                                              | 5,700 Btu/hr<br>(1,670 W)                                                                          |  |

| Cooling                                                                                      | Air-cooled                                                                                          | Air-cooled                                                                                             | Air-cooled                                                                                         |  |

| Minimum side<br>clearance                                                                    | 2.00 in. (5 cm)                                                                                     | 2.00 in. (5 cm)                                                                                        | 2.00 in. (5 cm)                                                                                    |  |

| Minimum front<br>clearance                                                                   | 36.00 in. (91 cm)                                                                                   | 36.00 in. (91 cm)                                                                                      | 36.00 in. (91 cm )                                                                                 |  |

| Minimum back<br>clearance                                                                    | 30.00 in. (76 cm)                                                                                   | 30.00 in. (76 cm)                                                                                      | 30.00 in. (76 cm)                                                                                  |  |

| Power cable                                                                                  | 6.0 ft (1.8 m)                                                                                      | 6.00 ft (1.8 m)                                                                                        | 6.00 ft (1.8m)                                                                                     |  |

| Maximum data<br>cable length<br>(standard)                                                   | 65.6 ft (20 m)                                                                                      | 65.6 ft (20 m)                                                                                         | 65.6 ft (20 m)                                                                                     |  |

| Maximum data<br>cable length<br>(optional)                                                   | 98.4 ft (30 m)                                                                                      | 98.4 ft (30 m)                                                                                         | 98.4 ft (30 m)                                                                                     |  |