# CRAY-3 Hardware Description Manual

Publication Number: 3207

Fifth Revision July 30th, 1993

Cray Computer Corporation 1110 Bayfield Drive Colorado Springs, CO 80906 • •

# Copyright

Copyright © 1993 by Cray Computer Corporation. All Rights Reserved. This manual or parts thereof may not be reproduced in any form unless permitted by contract or by written permission of Cray Computer Corporation.

Copyright © 1986, 1987 by Cray Research, Inc. All Rights Reserved. This manual or parts thereof may not be reproduced in any form unless permitted by contract or by written permission of Cray Research, Inc.

Autotasking, CF77, CFT, CFT2, CFT77, CRAY-2, CRAY X-MP, CRAY Y-MP2E, and SEGLDR are trademarks and CRAY, CRAY-1, CRAY Y-MP, HSX, UNICOS, and X-MP EA are registered trademarks of Cray Research, Inc.

bdb, CRAY-3, CRAY-4, CSOS, Doyle, Holmes, Hudson, stb, Watson, and Wigins are trademarks of Cray Computer Corporation.

BSD is a registered trademark of the University of California, Berkeley.

Ethernet is a registered trademark of the Xerox Corporation.

Fluorinert is a registered trademark of 3M (Minnesota Mining and Manufacturing).

HYPERchannel is a trademark, and NSC is a registered trademark of Network Systems Corporation.

libtcl is authored by Professor John Osterhout, U.C. Berkeley and extended by Cray Computer Corporation.

Macintosh is a registered trademark and Quadra is a trademark of Apple Computer, Inc.

NeWS, NFS, OpenWindows, Sun, Sun Microsystems, Inc., SunView, and XView are trademarks and Sun Workstation and SunOS are registered trademarks of Sun Microsystems, Inc.

System V is a trademark, and OPEN LOOK and UNIX are registered trademarks of USL (UNIX System Laboratories) in the United States and other countries.

OSF and OSF/Motif are trademarks of Open Software Foundation.

POSIX is a trademark of The Institute of Electrical and Electronics Engineers, Inc.

SPARCstation and SPARCware are trademarks of SPARC International, Inc.

UltraNet is a registered trademark of Ultra Network Technologies, Inc.

VAST is a registered trademark of Pacific Sierra Research Corporation.

X Window System is a trademark of the Massachusetts Institute of Technology.

The CSOS operating system is derived from Cray Research, Incorporated's UNICOS operating system. The UNICOS operating system is derived from the USL's UNIX System V operating system. UNICOS is also based in part on the Fourth Berkeley Software Distribution under license from The Regents of the University of California.

## Reader Comments

If you have any comment about the technical accuracy, content, or organization of this manual, please tell us. You can contact us in any of the following ways:

Call our Technical Publications department at (719) 579-6464 from 8 a.m. to 5 p.m. (Mountain Time).

Send us electronic mail from a CSOS or UNIX system to pubs@craycos.com

Write to us at the following address:

Cray Computer Corp. Technical Publications Department P.O. Box 17500 Colorado Springs, CO 80935

We value your comments and will respond to them promptly.

.

# Table of Contents

|           | Copyrighti<br>Reader Commentsiii<br>Table of Contentsv<br>Introductionix |       |

|-----------|--------------------------------------------------------------------------|-------|

| Chapter 1 | CRAY-3 Overview 1                                                        |       |

|           | Packaging Overview1                                                      | 1.1   |

|           | The Octants                                                              | 1.1.1 |

|           | The Modules                                                              | 1.1.2 |

|           | The Printed Circuit Boards                                               | 1.1.3 |

|           | The Logic, Power and Resistor Plates                                     | 1.1.4 |

|           | The Integrated Circuits                                                  | 1.1.5 |

|           | Design Overview15                                                        | 1.2   |

|           | Performance Specifications                                               | 1.2.1 |

|           | Common Memory17                                                          | 1.2.2 |

|           | Background Processing                                                    | 1.2.3 |

|           | Foreground Processing                                                    | 1.2.4 |

|           | CRAY-3 Product Description                                               | 1.3   |

| Chapter 2 | Circuit Component Design 29    |            |

|-----------|--------------------------------|------------|

|           | GaAs Component Design          | 2.1        |

|           | Transistor Design              | 2.2        |

|           | Current Source Design          | 2.3        |

|           | Diode Design                   | 2.4        |

|           | Capacitor Design40             | 2.5        |

|           | Resistor Design46              | 2.6        |

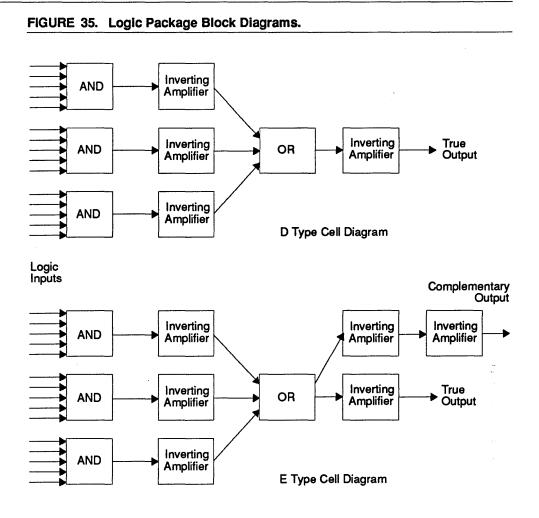

|           | Logic Package Design           | 2.7        |

|           | D Cell Design                  | 2.7.1      |

|           | E Cell Design                  | 2.7.2      |

|           | F Cell Design                  | 2.7.3      |

|           | FF and FG Cell Design          | 2.7.4      |

|           | FJ and FK Cell Design          | 2.7.5      |

|           | Clock Amplifier Design60       | 2.8        |

|           | Other Circuits                 | 2.9        |

|           | The Vector Register Package    | 2.10       |

|           | The Silicon Memory Packages    | 2.11       |

|           | The CRAY-3 Cell Library        | 2.12       |

| hapter 3  | Integrated Circuit Artwork 79  |            |

|           | The IC Assembly                | 3.1        |

|           | Pouting on IC 98               | 3.2        |

|           | Routing an IC                  |            |

|           | Verification of the IC Artwork | 3.3        |

| Chapter 4 |                                | 3.3        |

| Chapter 4 | Verification of the IC Artwork | 3.3<br>4.1 |

| Chapter 4 | Verification of the IC Artwork |            |

| Chapter 4 | Verification of the IC Artwork | 4.1        |

| hapter 4  | Verification of the IC Artwork | 4.1<br>4.2 |

| Chapter 5 | Integrated Circuit Fabrication 11      | 3              |

|-----------|----------------------------------------|----------------|

|           | Integrated Circuit Fabrication11       | 3 5.1          |

|           | Canon Wafer Stepper11                  | 6 5.1.1        |

|           | GaAs Fab Processing Steps              | 8 5.1.2        |

|           | Wafer Processing12                     | 4 5.2          |

|           | FAST Testing12                         | .4 5.2.1       |

|           | Grinding                               |                |

|           | Dicing                                 |                |

|           | Pick and Place                         |                |

| Chapter 6 | Module Structure 13                    | 3              |

|           | Overview                               | 3 6.1          |

|           | Printed Circuit Board Manufacturing    | 9 6.2          |

|           | The 25 mm Circuit Boards14             | <b>1</b> 6.3   |

|           | Logic Plates15                         | 6.4            |

|           | Resistor Plates15                      | 4 6.5          |

|           | Power Plates15                         | 8 6.6          |

|           | Memory Board Bypass Capacitors         | 6.7            |

|           | Power Blades                           | 6.8            |

| 7         | Logic Connectors16                     | 7 6.9          |

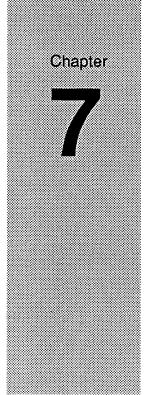

| Chapter 7 | Module Assembly, Testing and Repair 17 | 1              |

|           | Final Assembly of the Module17         | ' <b>1</b> 7.1 |

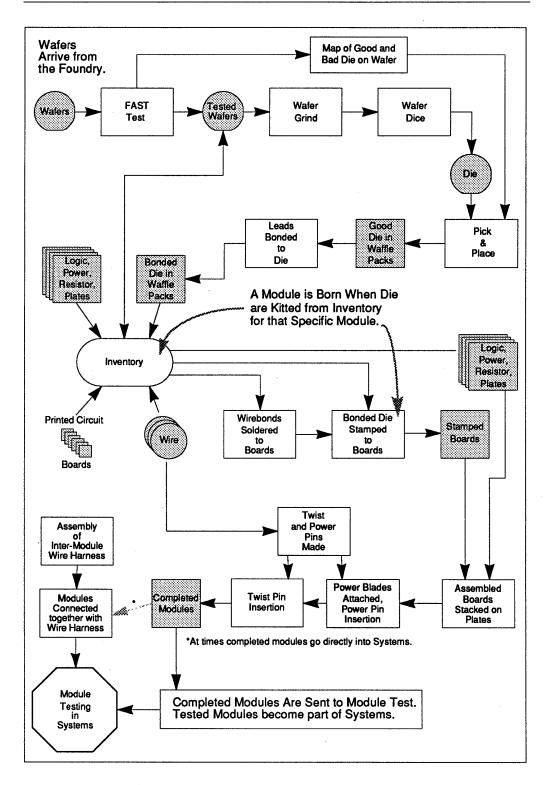

|           | Kitting                                | 3 7.1.1        |

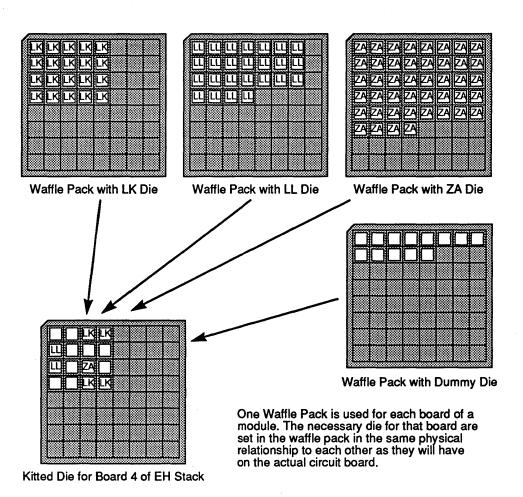

|           | Board Soldering                        |                |

|           | Die Attach                             |                |

|           | Twist Pin Manufacturing                |                |

|           | Pinning the Module Assembly            |                |

|           | Module Testing                         |                |

|           | Pulse-Power Testing19                  | 0 7.2.1        |

|           | Full-Power Testing                     | 6 7.2.2        |

|           | Module Repair                          | 2 7.3          |

| Failure Analysis                                  | 203                                                                                                                                                                                                                                                                                                                                                                                                                                               | 7.4            |

|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| Cabinet Design 20                                 | 07                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |

| System Cabinet                                    | :07                                                                                                                                                                                                                                                                                                                                                                                                                                               | 8.1            |

| Octant Assembly2                                  | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                | 8.2            |

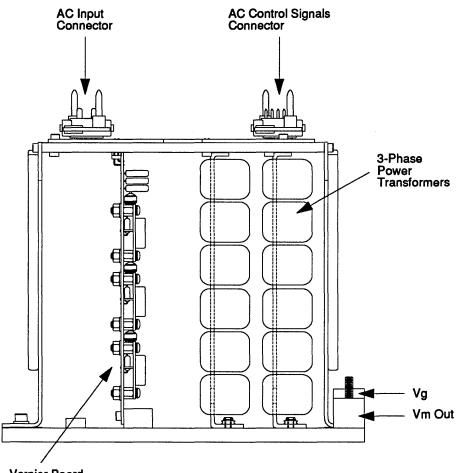

| Power Supplies                                    | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                | 8.3            |

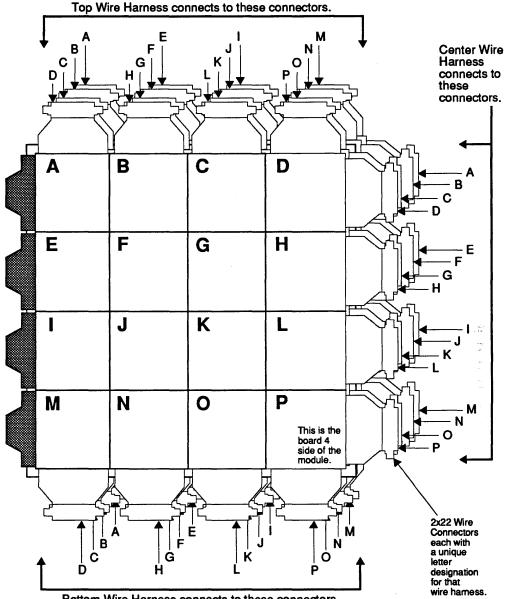

| Wire Harnesses                                    | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                | 8.4            |

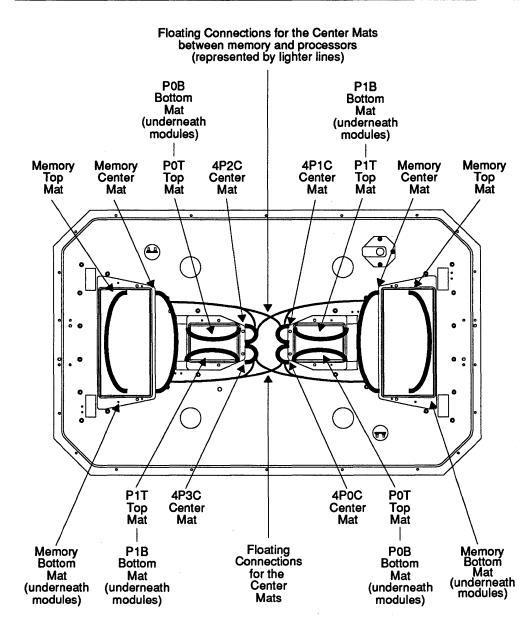

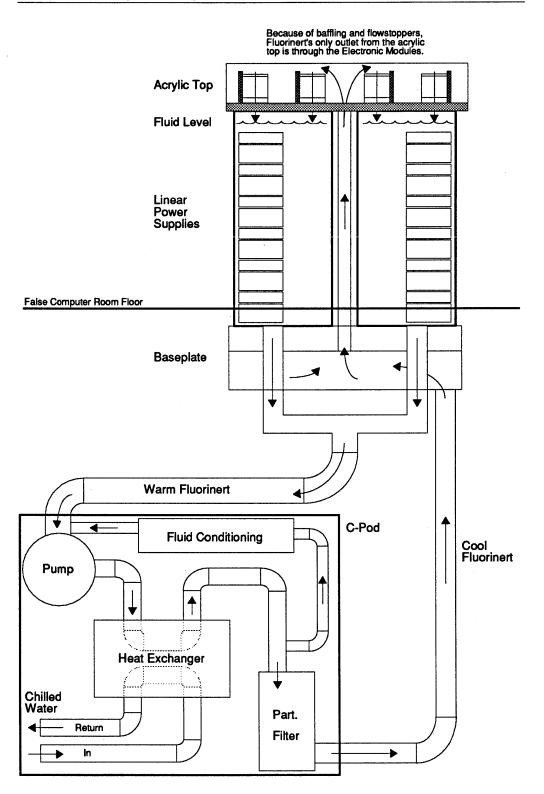

| Cooling                                           | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                | 8.5            |

| •                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 8.6            |

|                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 8.7            |

| -                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 8.7.1          |

|                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 8.7.2          |

|                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 8.7.3          |

|                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 8.7.4          |

|                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 8.7.5          |

| AC Box                                            | 47                                                                                                                                                                                                                                                                                                                                                                                                                                                | 8.7.6          |

| DC Bulkhead                                       | 48                                                                                                                                                                                                                                                                                                                                                                                                                                                | 8.7.7          |

| Peripheral Equipment2                             | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                | 8.8            |

| DD-49 Disk Unit                                   | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                | 8.8.1          |

| DS-40 Disk Subsystem2                             | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                | 8.8.2          |

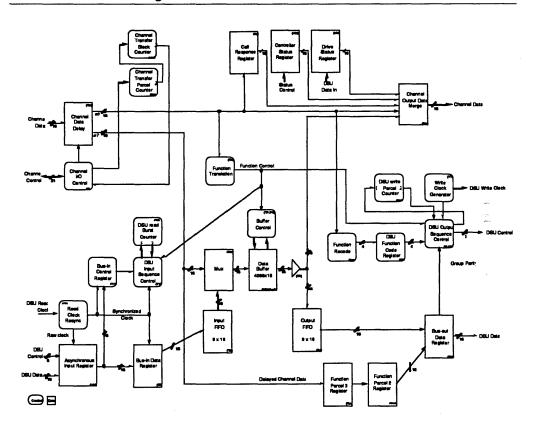

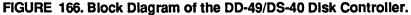

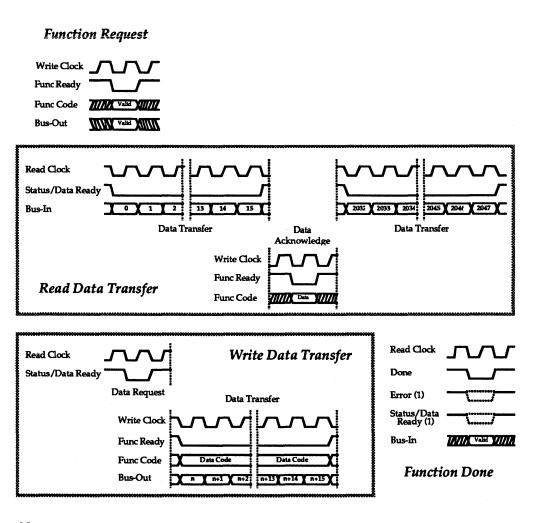

| CRAY-3 Circuits for the DD-49 and DS-402          | 52                                                                                                                                                                                                                                                                                                                                                                                                                                                | 8.8.3          |

| RAID Disk Array Subsystem                         | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                | 8.8.4          |

| CRAY-3 HIPPI Circuitry                            | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                | 8.8.5          |

| Integrated Circuit Packages Used in the CRAY-3 25 | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |

| CRAY-3 Board Stack Assignments 27                 | 79                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |

|                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                |

|                                                   | Cabinet Design2System Cabinet2Octant Assembly2Power Supplies2Wire Harnesses2Cooling2Translator Cards2System Control Pod2Front Panel User Controls2Maintenance Panel2Electronic Module2Motor Starters2Clock Source2AC Box2DC Bulkhead2Peripheral Equipment2DS-40 Disk Unit2CRAY-3 Circuits for the DD-49 and DS-402RAID Disk Array Subsystem2CRAY-3 HIPPI Circuitry2Integrated Circuit Packages Used in the CRAY-32CRAY-3 Board Stack Assignments2 | System Cabinet |

# Introduction

This is the fifth revision of this manual. The previous version was dated January 15, 1991. All sections have been revised and many new sections added to reflect changes which have occurred over the last twenty-nine months in the design, manufacturing and testing of the CRAY-3 supercomputer system. This current version of the manual has over 300 pages, more than 160 illustrations and 22 tables, whereas the previous version had just over 100 pages and 45 illustrations.

Much effort has been expended to make this latest edition of the manual accurate and up-to-date. However, this is really an impossible task since procedures and design are in an almost continuous state of flux. At some point a decision must be made to "go to press" knowing that by the time the manual reaches most readers certain items of fact will have already changed.

### Purpose

The CRAY-3 Hardware Description Manual is intended to provide the person who is working on the project with a general reference manual to the component hardware that comprises a CRAY-3 computer system. It is ideal for introducing a new employee to the overall project. The manual will also find interested readers among current and future customers, since it provides a unique summary of information on the CRAY-3 that is not available in any other form.

#### Organization

The manual first presents an overview of the CRAY-3 computer system looking at both the overall architecture of the machine and the implementation of that design in the hardware and packaging. This is done in Chapter 1. The overview of the packaging begins at the highest level (the System Cabinet) and works down to the lowest level (the integrated circuit die). This helps the reader become familiar with how all the parts fit together in the complete machine. The overview of the packaging is presented before the overview of the design to introduce some of the terminology which is employed in discussing the design.

In the remaining chapters each major component is discussed in much greater detail. In these chapters the presentation order is just the opposite of that in the introduction. The chapters proceed from the lowest level (the design of the integrated circuit components) to the highest level (the system cabinets and peripheral equipment).

The manual has tried to reach a balance between being overly technical and obtuse, and simplistic and obvious. This has not been an easy task given the inherently technical subject matter and the broad spectrum of potential readers.

Hopefully, employees of Cray Computer Corporation, whatever their position, will find the CRAY-3 Hardware Description Manual interesting and informative, for they are viewed as the primary readers.

# **CRAY-3** Overview

This chapter introduces the CRAY-3 computer system by providing three overviews of the machine. The first overview looks at the implementation of the design in the hardware and packaging. Giving an overview of the hardware first will introduce some of the terminology needed for the following discussions. The second overview looks at the design and architecture of the machine. This overview includes a summary of the machine's performance specifications. Much of this discussion uses the CRAY-2 as a point of reference for performance comparisons. The third overview ends the chapter with a summary of the machine in the form of a product description.

It is important for the reader to grasp the big picture presented in these three overviews so that later discussions about each individual component or group of components can be better understood in the overall context of the complete machine.

## **1.1 Packaging Overview**

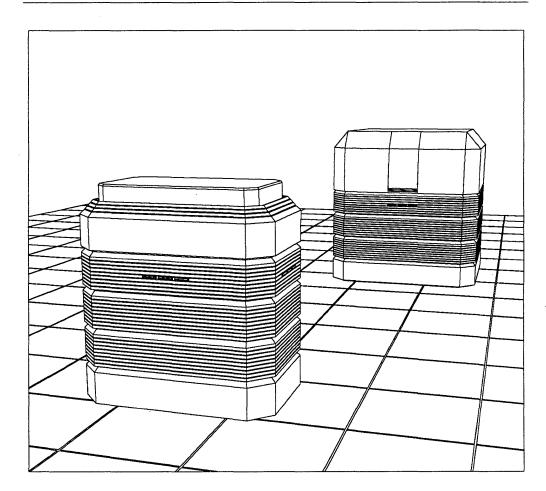

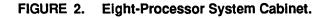

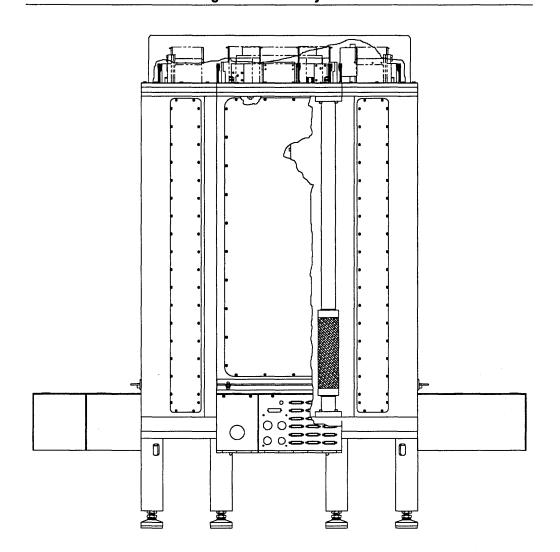

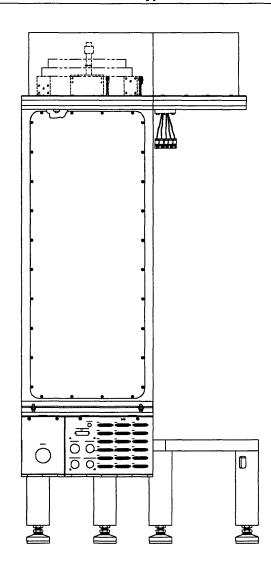

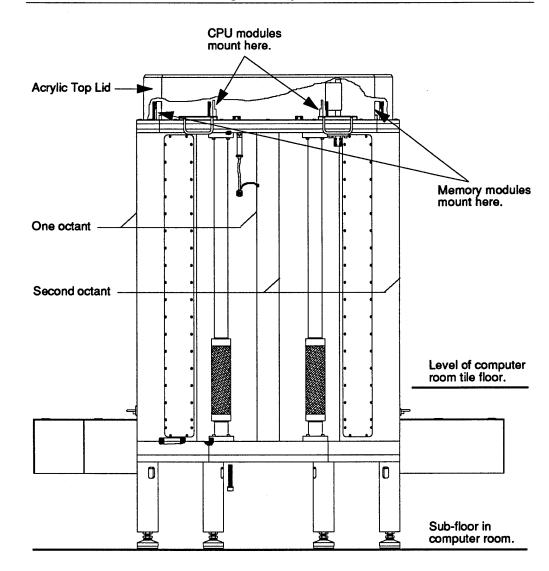

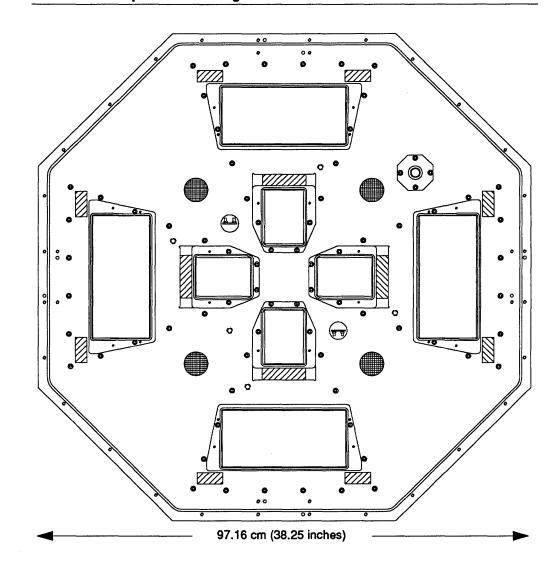

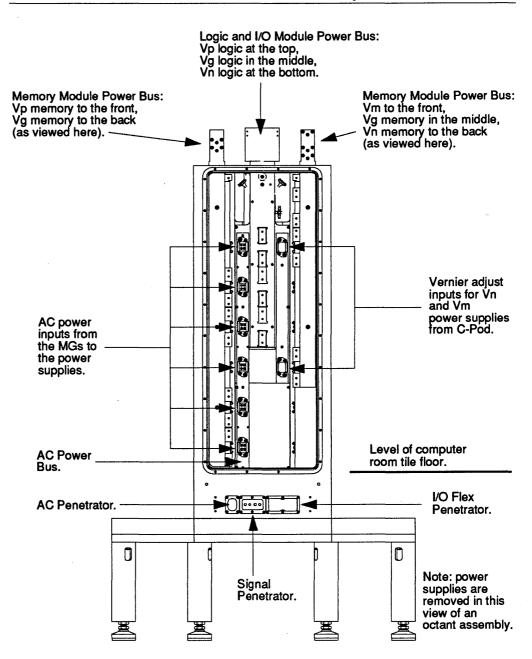

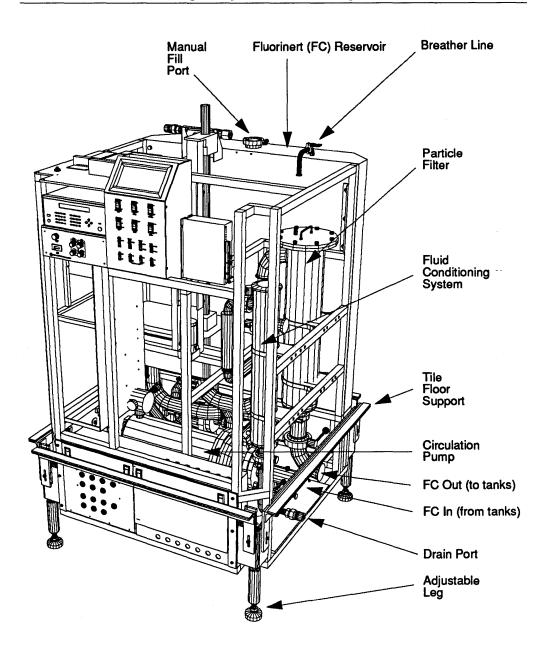

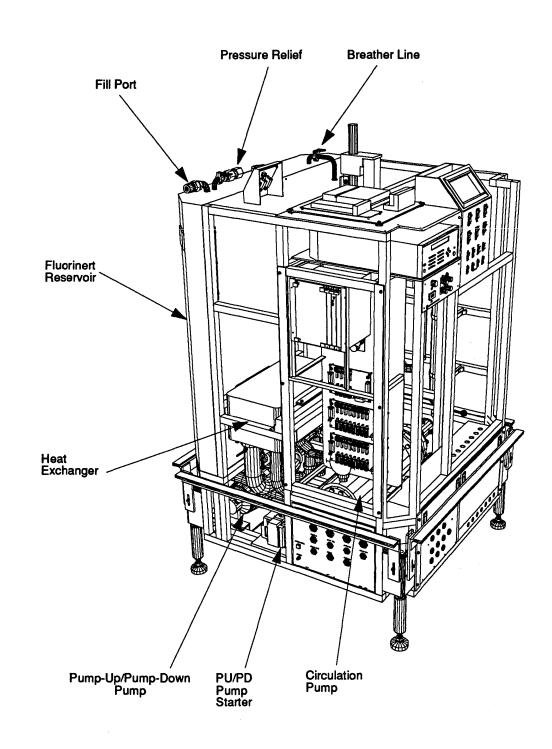

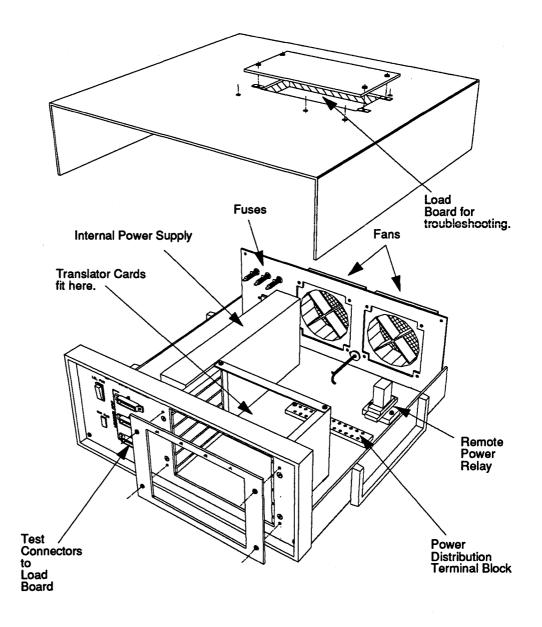

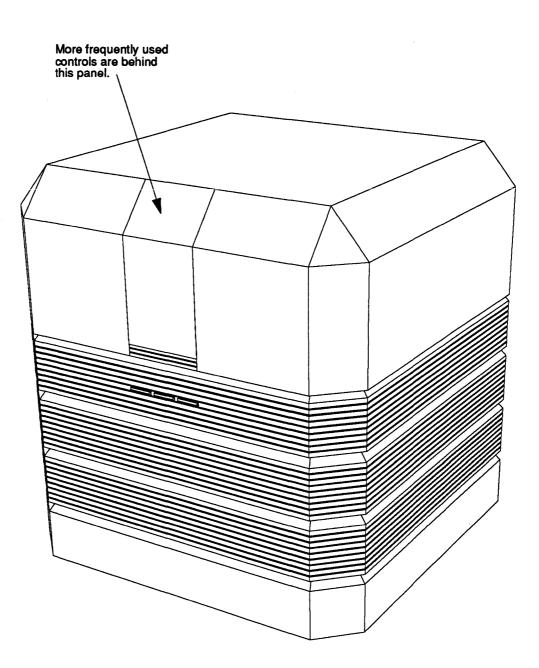

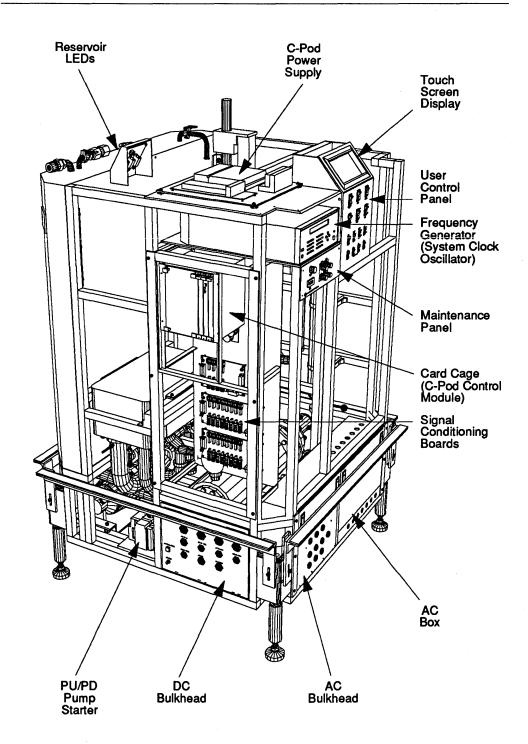

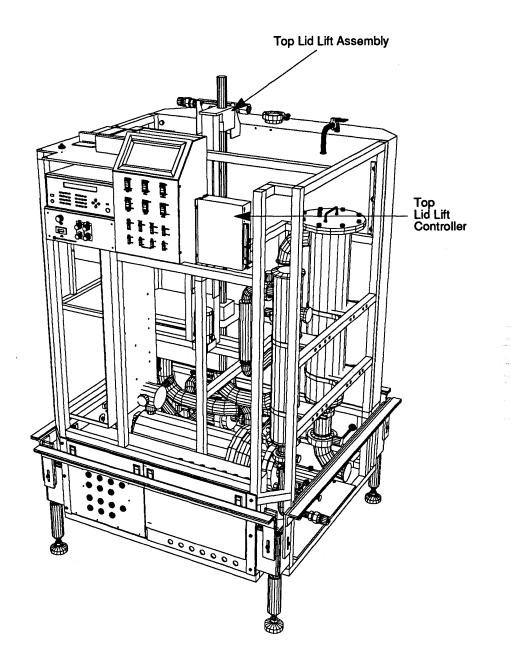

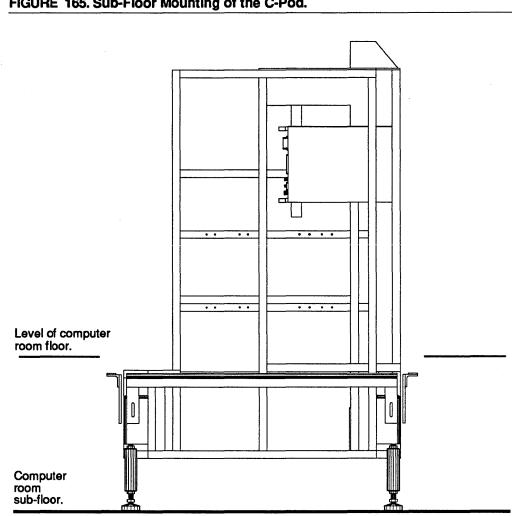

The CRAY-3 hardware is constructed of synchronous networks of binary circuits. These circuits are packaged in 336 modules for a 16-processor machine. The 336 modules fit into the top section of the System Cabinet. The System Cabinet for a 16-processor machine is in the shape of an octagon 109.22 cm (43 inches) wide and 121.92 cm (48 inches) above a computer room false floor. The power supplies for the modules are located below the modules

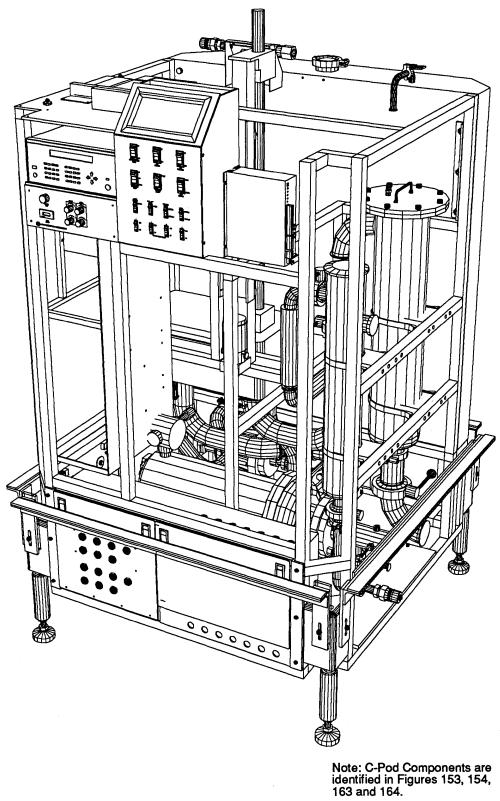

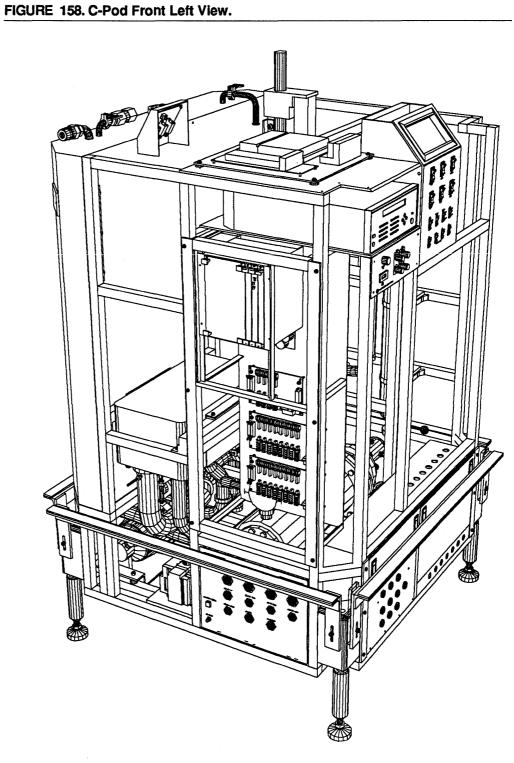

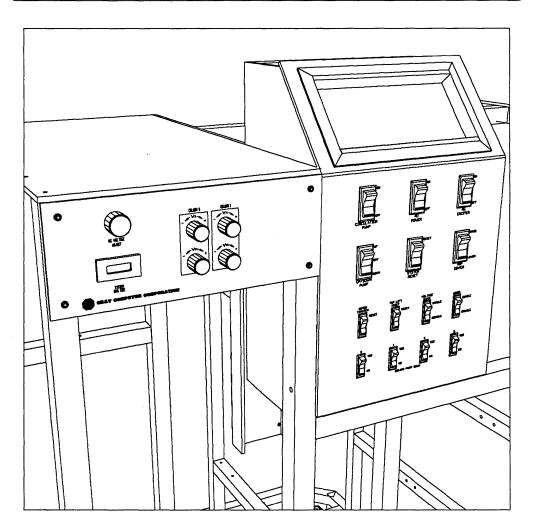

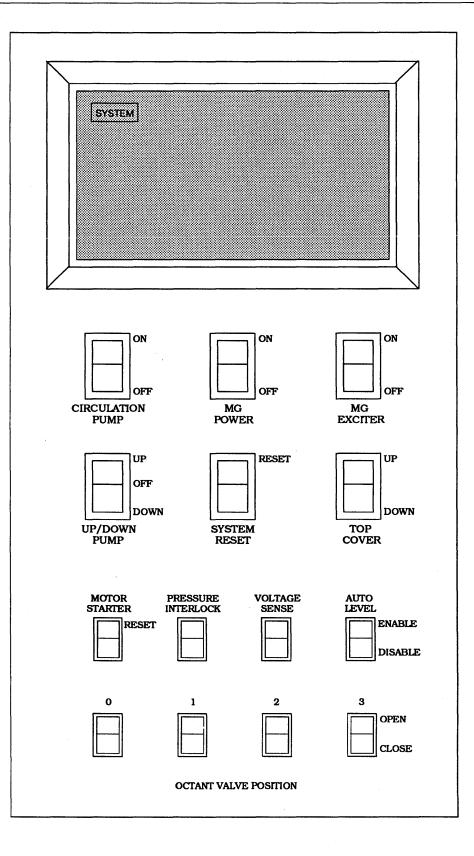

in the bottom section of the System Cabinet. Another cabinet, the Control Pod (commonly called the C-Pod), located near the System Cabinet, contains the pumps, heat exchangers, reservoir, filters and control circuits for the cooling system, the system clock, controls for the power supplies and other mechanical and electronic monitoring devices. Computer control and program initiation and monitoring is done from a workstation console which may be located in another room.

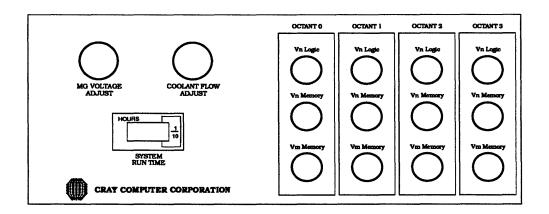

#### FIGURE 1. Four-Processor System Cabinet and Control Pod.

The System Cabinet and the C-Pod are located near each other in a computer room with a false floor. The cooling and electrical connections required between the two cabinets are made underneath the false floor in the computer room so as to be invisible. The System Cabinet (the foreground cabinet in Figure 1) contains all of the logic and memory circuits of the computer in the top eight inches. The remainder of the System Cabinet houses all of the power supplies for the logic and memory circuits of the machine.

The CRAY-3 represents the first supercomputer to use gallium arsenide integrated circuits instead of silicon integrated circuits for all of its logic

circuits. Silicon integrated circuits are still used for the memory circuits in the machine.

The Four-Processor CRAY-3 System delivered to the National Center for Atmospheric Research on May 24, 1993 uses 62,738 integrated circuits all located on the 84 modules directly underneath the bronzed acrylic lid. The machine requires 90,000 watts of power and gives off 310,000 BTUs of heat—enough to heat six 2,000 square foot homes.

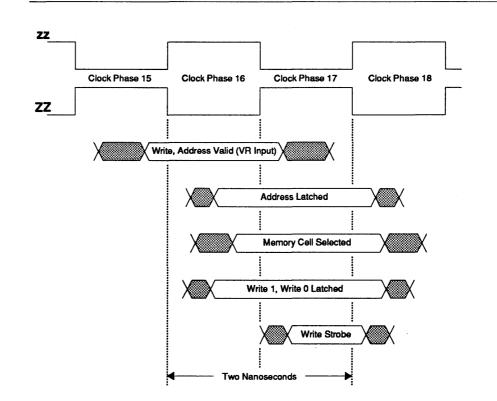

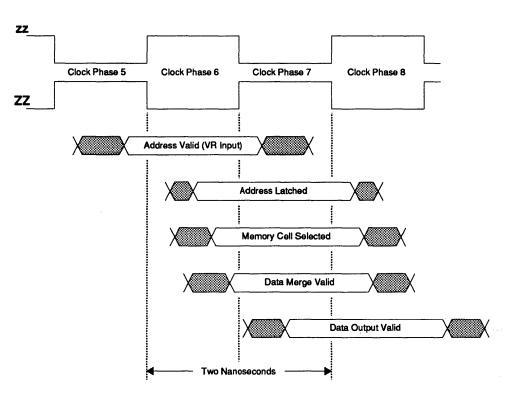

All of the binary circuits in the machine are synchronized to a 500 megahertz oscillator located in the C-Pod. The oscillator signal is transmitted as a square wave over 60 ohm twisted-pair wires to each of the module connectors in the System Cabinet. Wire lengths are controlled so that the travel time to the individual modules is accurate within 50 picoseconds. The oscillator square wave is delivered to each individual circuit package requiring a clock input within each module through traces on the logic plates and printed circuit

boards. A pulse is then formed from the square wave by the clock amplifiers in each integrated circuit package to gate data and control into the latches within the IC packages. This strobe pulse occurs simultaneously throughout the machine with a period of two nanoseconds. This time is referred to as the "machine clock period".

Another pulse is also formed from the inverted clock signal by identical clock amplifiers and is used to gate information into the latches one-half clock period later than the normal clock signal. This half clock period of time (one nanosecond) is referred to as a "clock phase time". The normal clock signal latches information in the even clock phases. The invert clock signal latches information in the odd clock phases. This dual phase system clock allows information to be latched into successive logic cells every nanosecond.

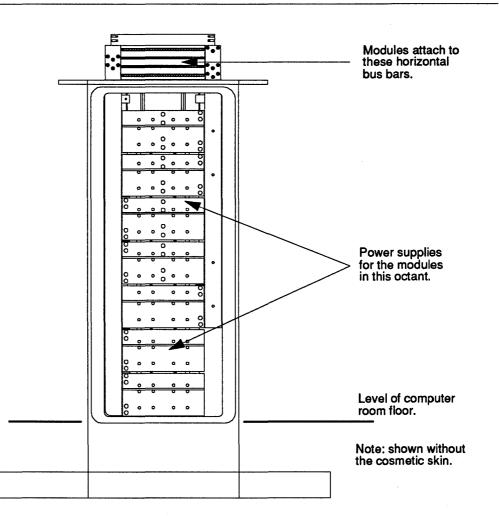

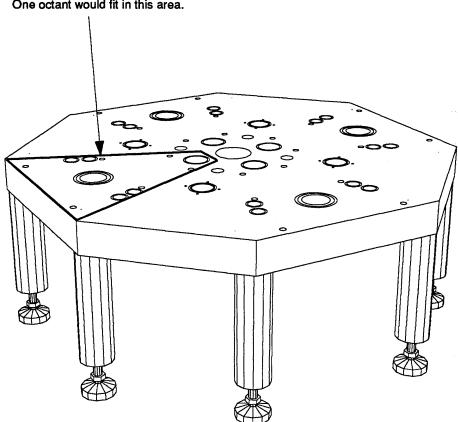

The System Cabinet is covered by a cosmetic shell or skin which gives the CRAY-3 the appearance of being of one piece. However, the System Cabinet is really modular in design and consists of groups of octants. Each octant contains a one- or two-processor piece of a complete 16-processor machine, including the memory modules, I/O module or modules and power supplies associated with the modules for that octant. Each module is in turn made up of various types of printed circuit boards; namely, the power plates, the resistor plate, the logic plates, and the smaller printed circuit boards which hold the IC packages for both logic and memory circuits.

#### 1.1.1 The Octants

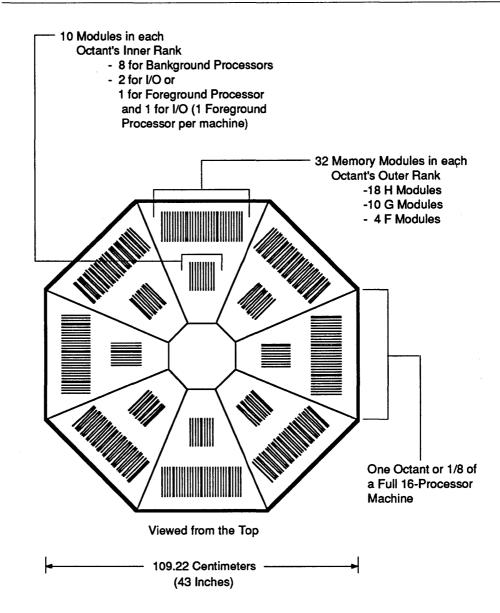

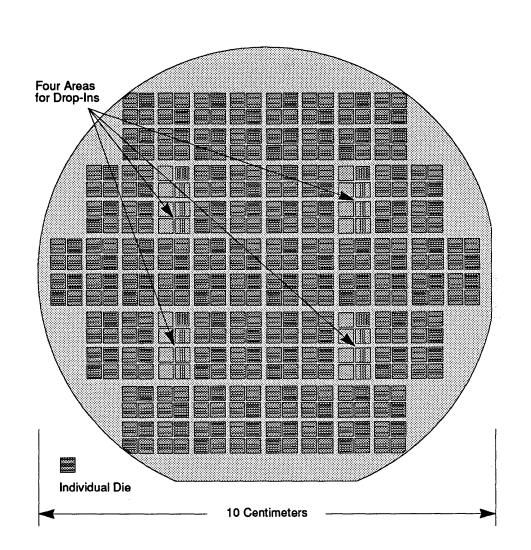

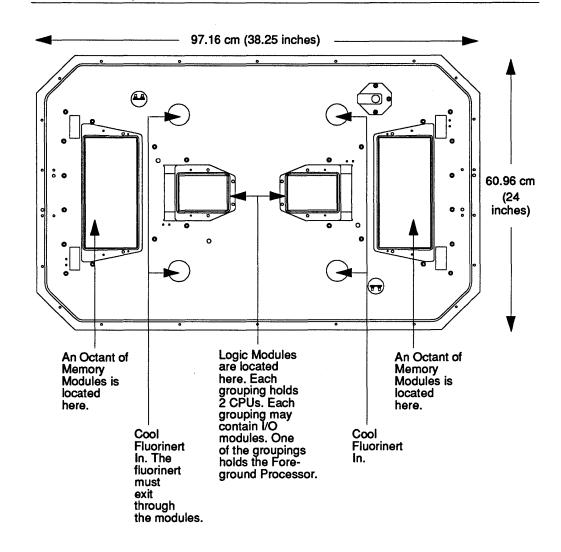

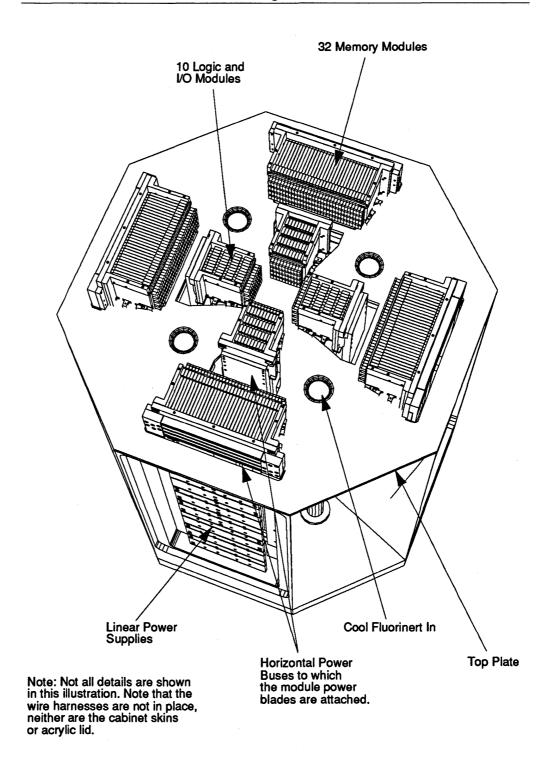

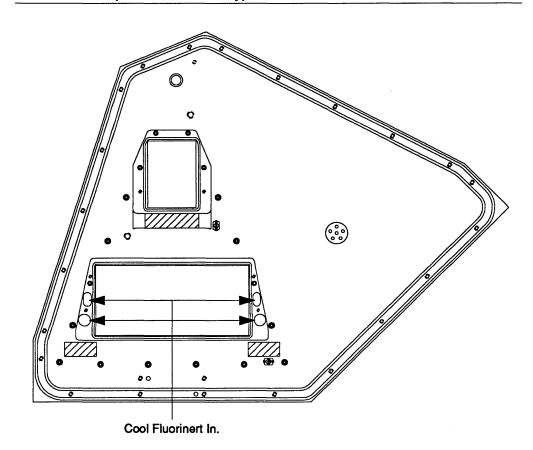

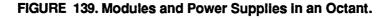

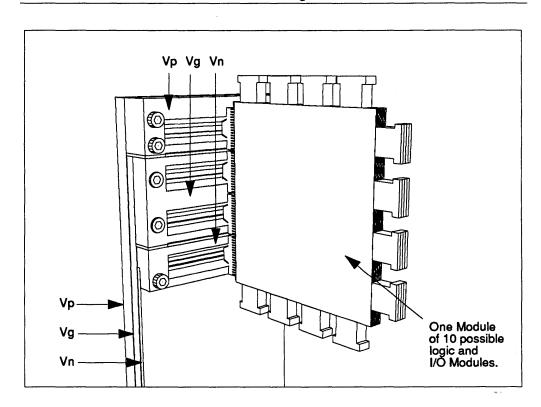

The 336 modules for a 16-processor machine are arranged in the System Cabinet in eight columns which form a closed octagon. Each column or octant contains 42 modules in two ranks, arranged in an outer rank of 32 and an inner rank of 10. This arrangement of modules is illustrated in Figure 3. Fluorinert, an inert electronic liquid, circulates in the cabinet frame and flows through the modules for cooling. The temperature, liquid velocity and turbulence through the modules are all controlled by various sensors and monitoring devices. The octagon of module columns is located on top of a similar structure containing power supplies for the system. The power supplies are also cooled by the circulating liquid. Total power consumption for the system is approximately 360 kilowatts or approximately 45 kilowatts per octant.

The CRAY-3 computer system can be configured in one-, two-, four-, eight-, or 16-processor versions. Since each one- or two-processor segment of the machine resides in one of the octants, a one- or two-processor machine would consist of one octant, a four-processor machine would consist of two octants, an eight-processor machine would be made up of four octants, and a 16-processor machine would have a full complement of eight octants utilizing the full octagon for its modules and power supplies.

Before leaving our introduction to octants, one should note that the term "octant" is often used to refer to two different, but integrally related parts of the CRAY-3. The term can be used to describe that physical portion of the System Cabinet where a group of 42 modules and their associated power supplies and wire harnesses reside. This is the sense in which we have used the term above. In this sense the term is often expanded to "octant assembly" or shortened to simply the "tank." This terminology is most often employed by the mechanical design group. Alternately, the term "octant" is often used by the logic design engineers when referring to a specific group of modules which could be placed into an octant assembly. In this sense one may refer to "Octant 6" (meaning a specific group of 42 modules) or to "an octant of memory" (meaning a specific

group of 32 memory modules) which could move about from one System Cabinet's octant assembly to another, or from one two-processor pulse power test station to a System Cabinet (or "tank"). In the first sense, a specific, physical location is being intended. In the second sense a specific group of modules that form a functional unit and that may move from one specific location to another is being intended.

#### 1.1.2 The Modules

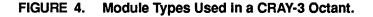

There are four basic types and ten unique modules used in the CRAY-3, each designated by a letter of the alphabet:

- The Background Processors—A, B, C, and D Modules.

- The Foreground Processor—E Module.

- Common Memory—F, G, and H Modules.

- I/O Modules—L and M Modules.

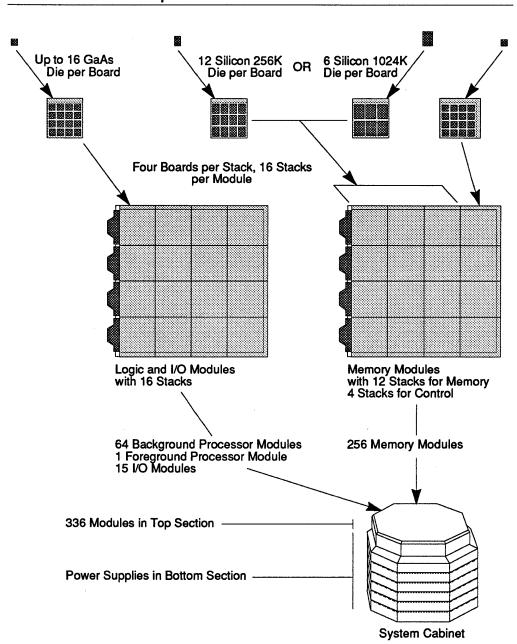

The Background Processors (A, B, C and D Modules) make up one processing unit (similar to a CPU in smaller computers). When we say "this is a two-processor CRAY-3" we are implying that it has two A, two B, two C, and two D modules. Likewise, a 16-processor machine has sixteen A, sixteen B, sixteen C and sixteen D modules. Each machine has one E module (the Foreground Processor) and each octant will also have 32 Common Memory modules, and zero, one, or two I/O modules of some kind depending upon customer needs. Therefore, in a 16-processor machine with 336 modules, 256 are reserved for Common Memory, 64 for Background Processors, one for the Foreground Processor and 15 for control of I/O devices such as disk drives.

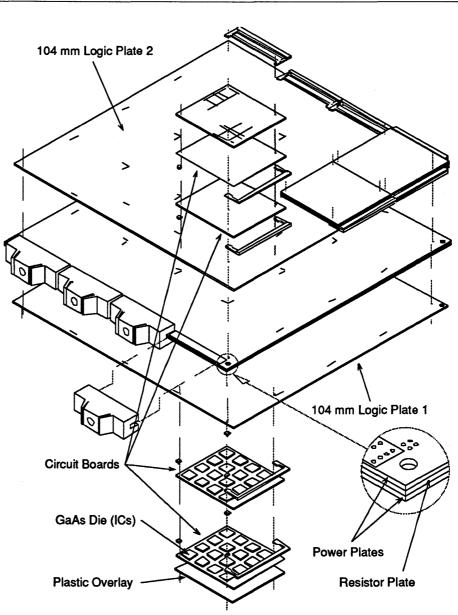

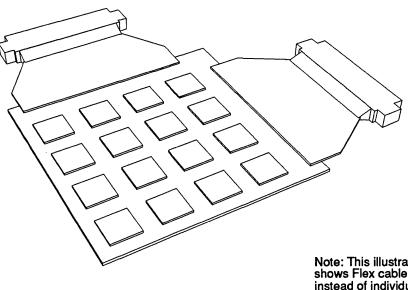

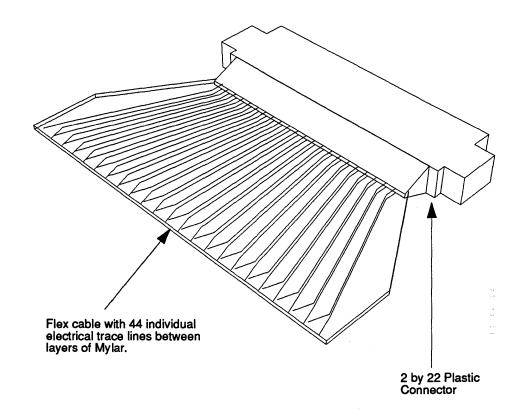

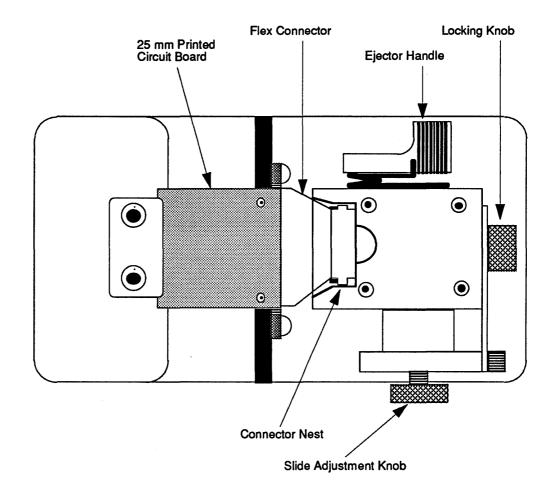

FIGURE 5. CRAY-3 Electronic Module.

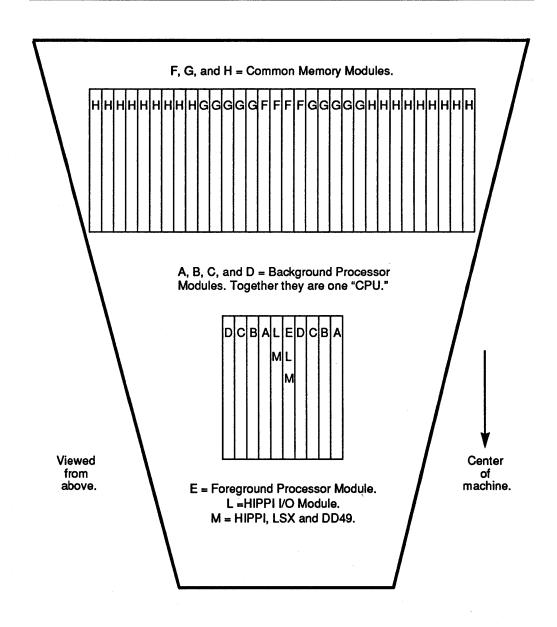

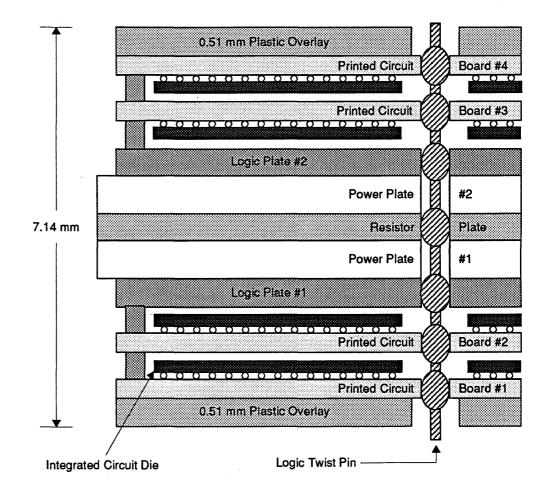

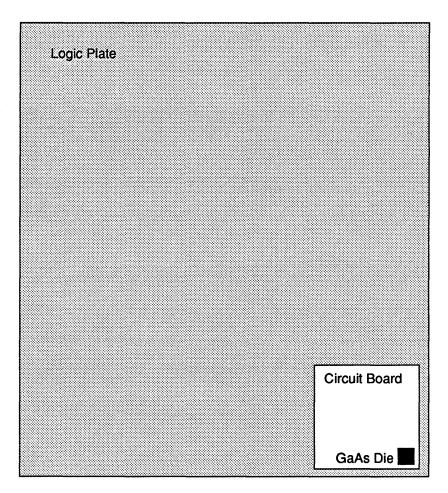

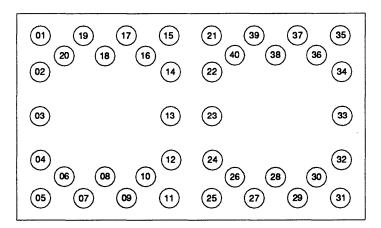

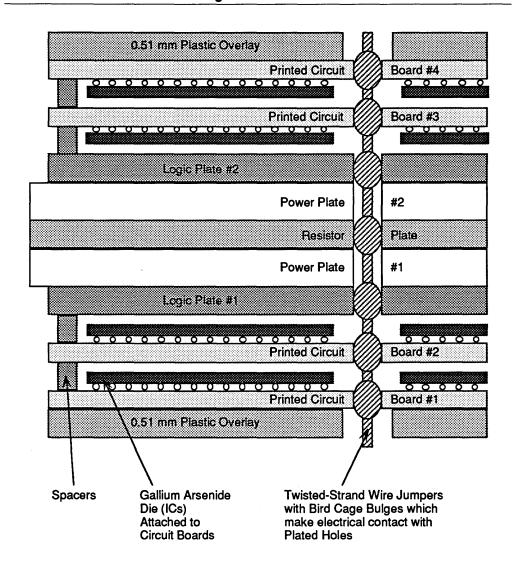

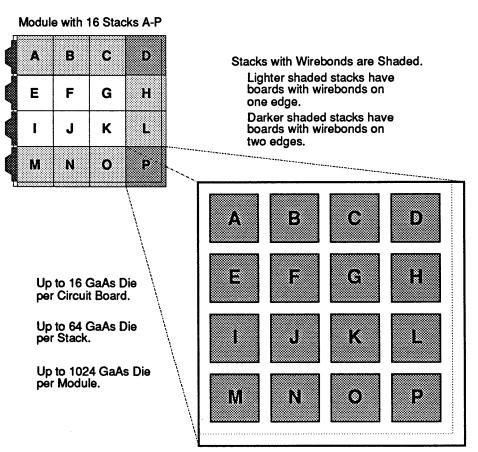

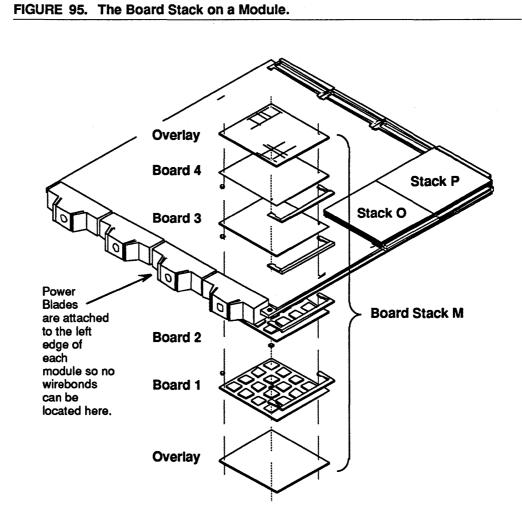

The modules are three dimensional structures measuring 121 mm by 107 mm by 7.14 mm thick. The circuit packages within the modules are unpackaged gallium arsenide or silicon die mounted directly on multi-layer circuit boards.

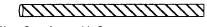

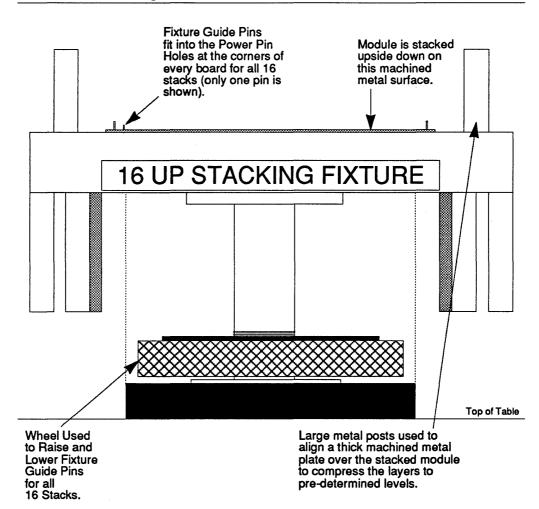

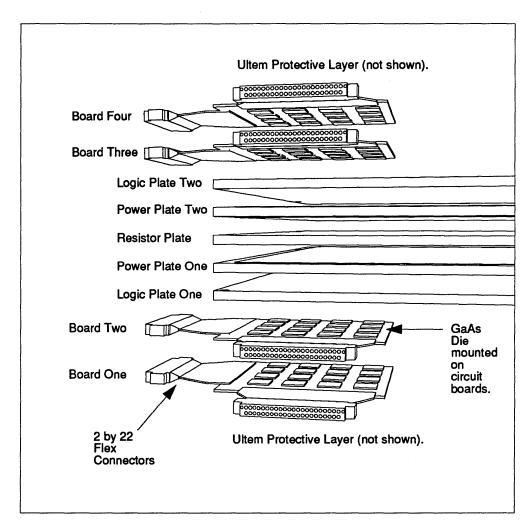

These boards are arranged in a four-by-four matrix of board stacks, each stack four boards deep (thick). In the center of this structure are two multi-layer logic plates which provide routing of logic signals between the sixteen board stacks in the module. Between the two logic plates of the module are two multi-layer power plates for power distribution to the board stacks. At the center of the module, between the power plates, is the resistor plate for signal termination. Some experiments are currently being conducted which place the resistor plate on the outside of this inner group of plates to provide for better cooling of the resistors. Use individual resistor boards on the outside of the logic plates rather than one resistor plate. The layers of the module sandwich can be seen in Figures 6 and 7.

FIGURE 6. Layers in a Module.

## 1.1.3 The Printed Circuit Boards

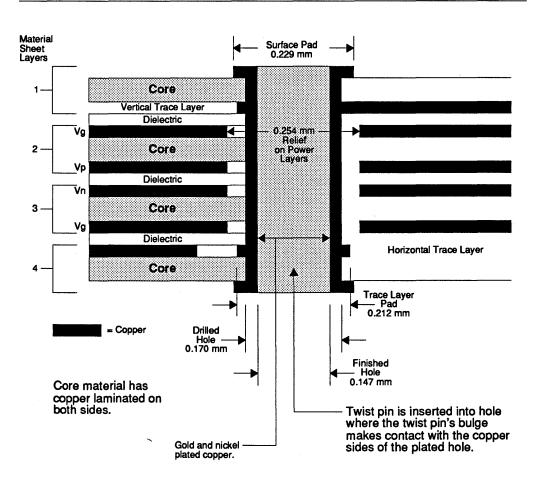

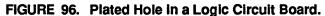

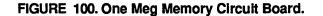

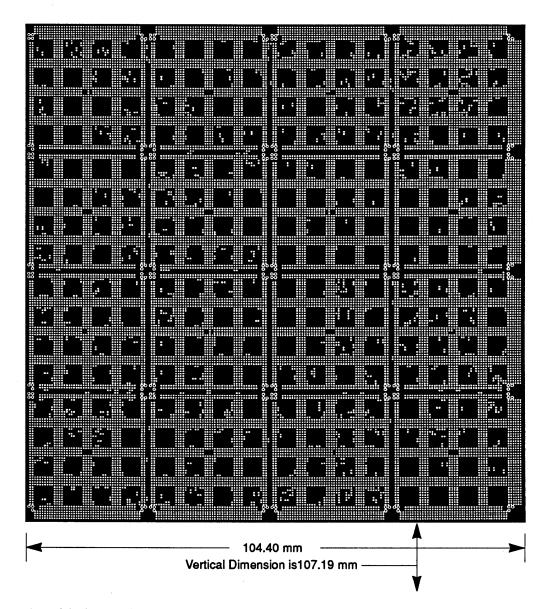

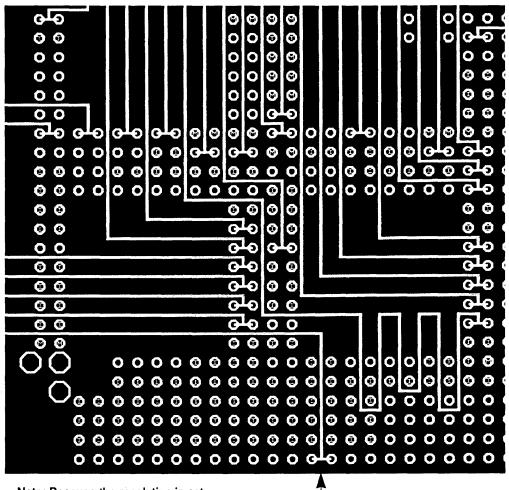

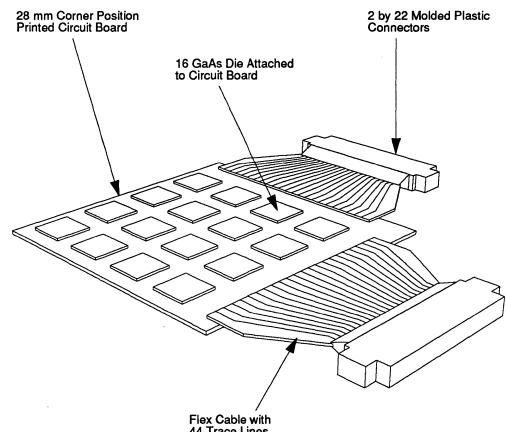

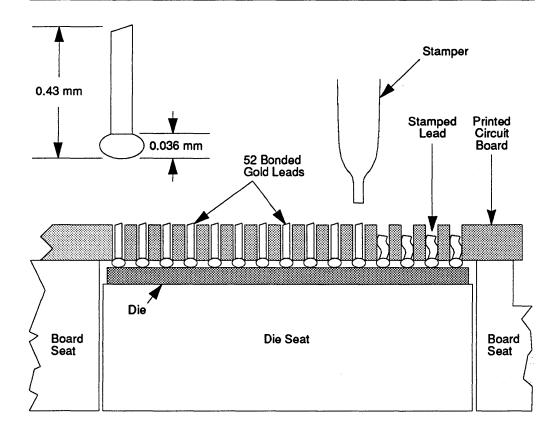

The printed circuit boards used in the CRAY-3 have the same basic properties of most modern printed circuit boards. They have very thin copper traces and serve as a place for mounting all of the ICs. However, they are smaller and thinner than most printed circuit boards commonly seen in electronic equipment. CRAY-3 printed circuit boards are only 28 mm x 25 mm in size, have eight layers (two of which are used for logic signal trace lines) and are only 0.38 mm thick.

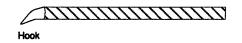

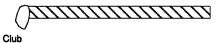

Illustrations shown are approximately actual size.

Up to sixteen GaAs die may be attached to each of these small circuit boards with fifty-two very small gold pins used to attach each die. The printed circuit boards provide the copper traces needed to interconnect the signals from one die to another, as well as to distribute the power and logic signals from the power and logic plates to the die. The logic signal trace lines on each printed circuit board are only 0.048 mm wide (a human hair averages 0.070 mm in diameter). The digital data for the 25 mm circuit boards is routed, drawn, and tested in the Artwork Department at Cray Computer Corporation. The circuit boards are manufactured at Cray Computer Corporation's own facility in Colorado Springs.

#### 1.1.4 The Logic, Power and Resistor Plates

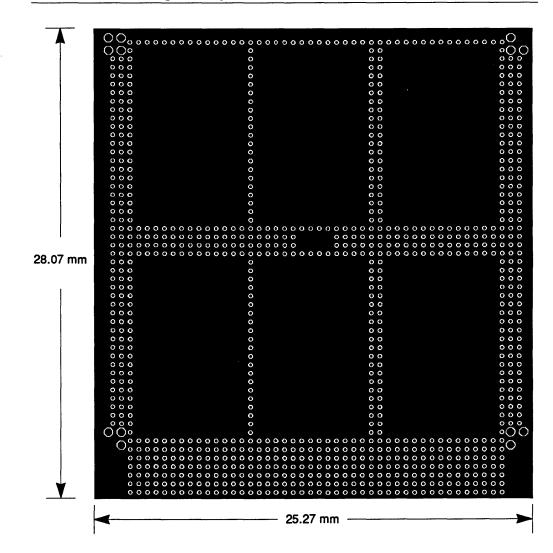

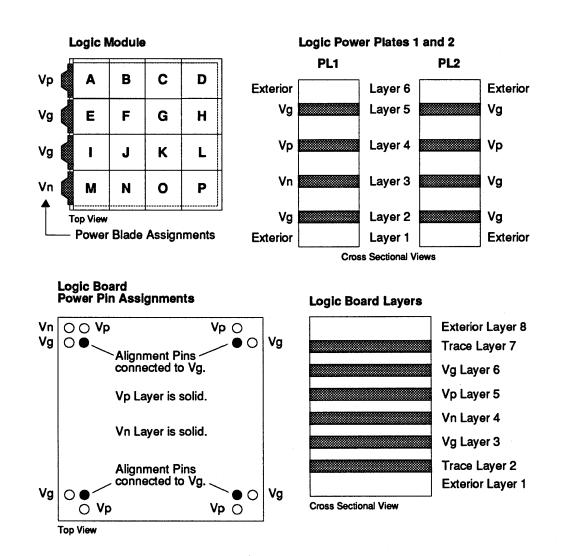

The Logic Plate is simply a larger size circuit board (107 mm by 104 mm and 0.46 mm thick). The reason for this difference in size should be apparent if you think of the logic plate's primary function—to distribute logic signals to and from the smaller 25 mm circuit boards which fit side-by-side making a square four circuit boards by four circuit boards, or sixteen in each layer of circuit boards. So the logic plate needs to cover the area of four 25 mm circuit boards if it is going to distribute signals to all those smaller boards. The logic plate contains eight layers, as do the 25 mm circuit boards, but whereas only two layers are used for drawing logic trace lines on the circuit boards, six layers are used for drawing logic trace lines on the logic plates.

When people refer to "the logic plate" they are often using that expression to describe more than a single logic plate since the logic plates are always used in pairs, drawn together, and considered a single, functional unit even though they are physically two separate plates. Furthermore, in addition to the two logic plates, the two power plates and the single resistor plate are also generally considered to be part of the logic plate's working assembly. Therefore, in our discussions, the power plates and resistor plate will be included in the section on the logic plates.

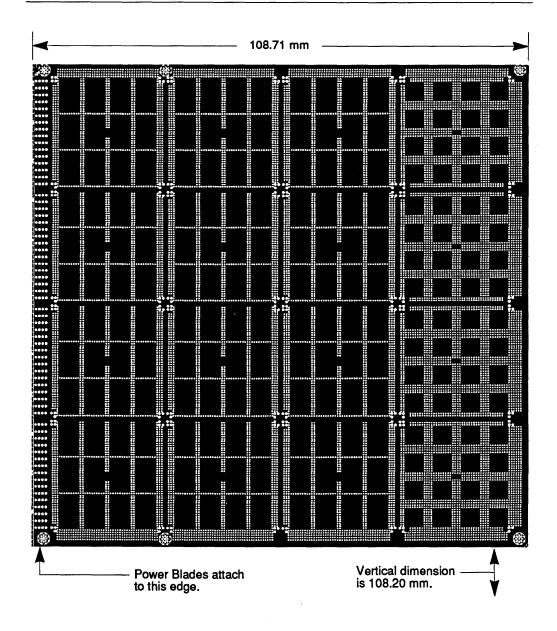

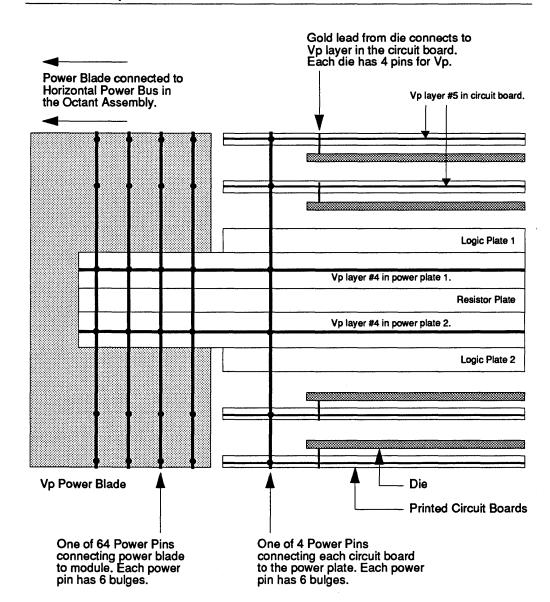

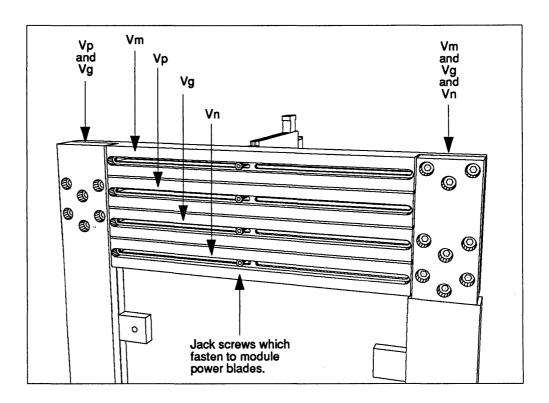

The power plates contain no logic signal traces. The power plate serves to deliver the necessary voltages from the power blades to all of the power pins at the corners of each 25 mm circuit board. From there the power layers of each circuit board deliver the appropriate voltages to the proper pins of each IC. The power plate is longer than the logic plates in one dimension to provide space for the power blades to contact the outside surface of each power plate.

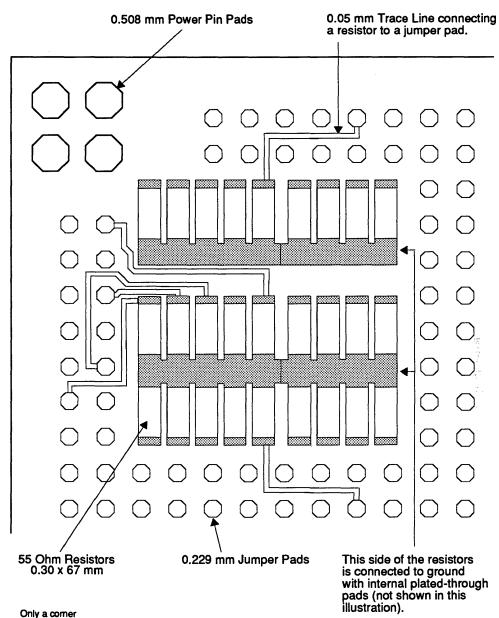

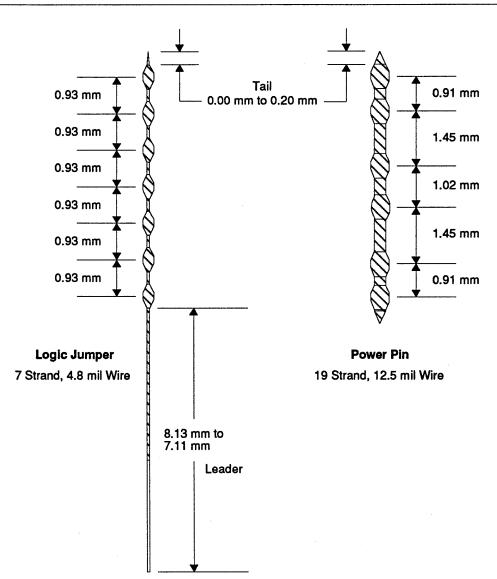

The resistor plate is sandwiched between the two power plates and contains the 55 ohm terminating resistors used to match the impedance of the signal transmission lines used throughout the logic circuits of the computer. The resistors are connected to the appropriate signal trace line through twist pin jumpers which carry the signal vertically through the module layers. As noted earlier, experiments are under way which change the positioning of the resistor plate in the module sandwich or which replace the resistor plate with individual resistor boards, also changing the position of the resistors relative to

other layers of the module sandwich. The outcome of these experiments will be reflected in later revisions of this manual.

#### 1.1.5 The Integrated Circuits

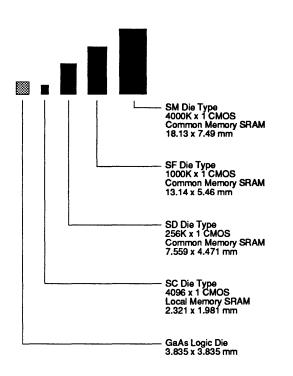

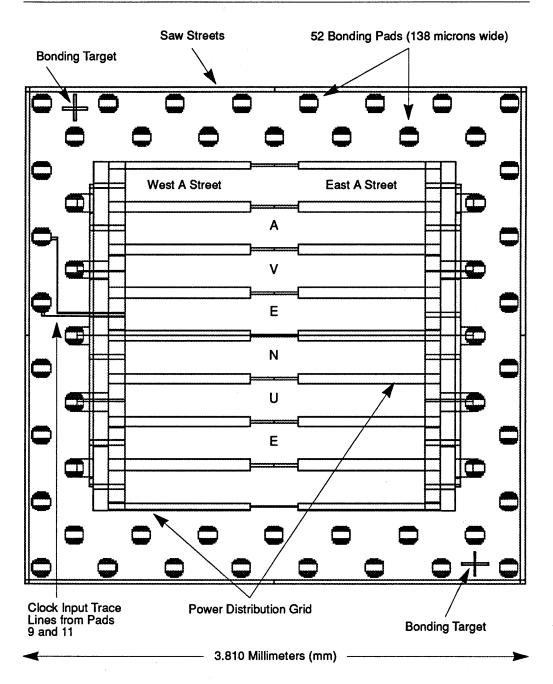

The smallest electronic parts used in the CRAY-3 are the integrated circuit packages or ICs. Sometimes people will refer to them as "chips" or generally after they have been manufactured and without being packaged in tiny containers, as "die." The physical size of the gallium arsenide die as they appear on the printed circuit boards is  $3.835 \times 3.835$  millimeters. There are 498 different GaAs integrated circuit packages used in the logical networks of the machine. Each of these circuits consists of an array of up to 128 basic logic cells. There are 36 different logic cells from which all the circuits are built. The maximum equivalent gate capacity of the circuit packages is approximately 500. The logic circuit packages have 52 bonding pads for connection to the printed circuit boards.

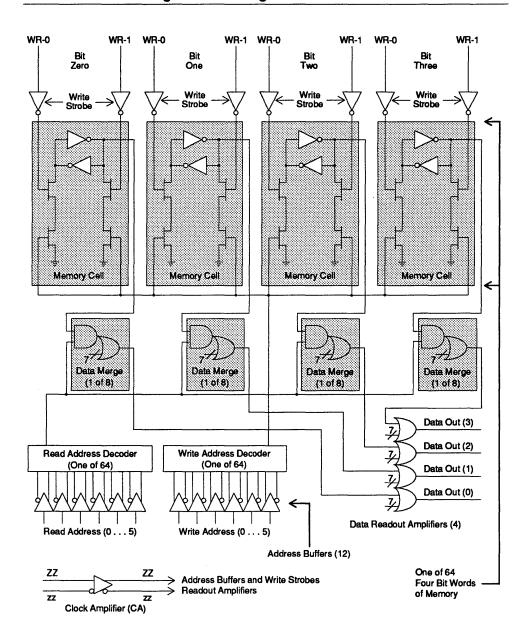

The ICs are the active circuits that actually perform the logical functions which enable the computer to perform its calculations. It should not be surprising then that there are a lot of ICs in a CRAY-3 computer system. The 16-processor machine contains over 266,000 ICs of which 147,456 are used for SD Common Memory. A two-processor machine has over 29,000 integrated circuit packages. Since there are only 498 unique types of ICs, many are used again and again throughout the machine to perform the necessary logical functions required. For example, the Vector Register integrated circuit package is used over 3,000 times in a 16-processor CRAY-3.

Nearly all other parts of the CRAY-3 are there simply to serve these tiny devices—to give them a safe place in which to reside, to keep them cool, to give them the right kind of power and to provide communication lines so they can talk to each other and communicate with the outside world.

The diagram in Figure 10 illustrates how the basic components of the CRAY-3, from the ICs to the Modules, fit together to make up a complete machine.

#### FIGURE 10. Basic Components of the CRAY-3.

## **1.2 Design Overview**

The CRAY-3 computer system represents a major enhancement over the CRAY-2 computer system, providing an order of magnitude performance improvement at a comparable cost. This performance gain is achieved through the use of three new design features 1) the use of gallium arsenide logic circuits in place of the silicon circuits previously used, 2) the use of innovative packaging and cooling technologies and 3) the implementation of a number of architectural changes, including more processors and enhanced memory access.

### 1.2.1 Performance Specifications

Each processor in the CRAY-3 system is slightly more than two times as fast as its CRAY-2 counterpart. With a four-fold increase in the number of total processors, this leads to an overall improvement range better than eight times that of a CRAY-2.

The CRAY-3 system is functionally equivalent to the CRAY-2 system. Logic enhancements to the system have enabled performance to be increased while providing an extension of the original CRAY-2 instruction set. The following table lists the major differences between the CRAY-2 and CRAY-3 systems:

| Parameter                     | CRAY-3                                                                                                                                                                             | CRAY-2                                                                                                                                          |

|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| Circuit Speed                 | 2 Nanosecond Clock (500 MHz)<br>Eight Levels of Logic per Clock                                                                                                                    | 4 Nanosecond Clock (250 MHz)<br>Four Levels of Logic per Clock                                                                                  |

| Processors                    | Up to 16 Background Processors<br>One Foreground Processor                                                                                                                         | Four Background Processors<br>One Foreground Processor                                                                                          |

| Instruction Issue<br>Rate     | Each Clock Period<br>Maximum Instruction Issue Rate<br>of 8000 MIPS (Million<br>Instructions<br>Per Second) for a 16 Processor<br>Configuration.                                   | Every Other Clock Period<br>Maximum Instruction Issue Rate<br>of 500 MIPS for a 4 Processor<br>Configuration.                                   |

| Common Memory                 | 512 Million Words of Static<br>Semiconductor Memory<br>or<br>1024 Million Words of SRAM<br>or<br>2048 Million Words of SRAM<br>(with memory enhancement now<br>under development). | 256 Million Words of Dynamic<br>Semiconductor Memory.                                                                                           |

| Memory Chip<br>Access Time    | 22 Nanoseconds                                                                                                                                                                     | 80 Nanoseconds                                                                                                                                  |

| Common Memory<br>Bandwidth    | 16 Gigawords Per Second                                                                                                                                                            | 1 Gigaword Per Second                                                                                                                           |

| Common Memory<br>Access Ports | Each Background Processor<br>has a Bi-Directional Access Port.<br>Reads and Writes may Proceed<br>Simultaneously.                                                                  | Each Background Processor<br>has One Access Port.<br>Read or Write but not both<br>Simultaneously.                                              |

| Floating Point<br>Computation | Maximum Burst Rate of 16<br>Gigaflops                                                                                                                                              | Maximum Burst Rate of 2<br>Gigaflops                                                                                                            |

| Vector Register<br>Structure  | Eight Vector Registers per<br>Background Processor.<br>Employs Tailgating:<br>writing may begin immediately<br>after previous data reading is<br>initiated.                        | Only two late versions of the<br>CRAY-2 employed Tailgating.<br>Both versions were transferred to<br>Cray Computer Corporation at<br>inception. |

#### TABLE 1. Performance Comparisons Between the CRAY-3 and the CRAY-2.

### 1.2.2 Common Memory

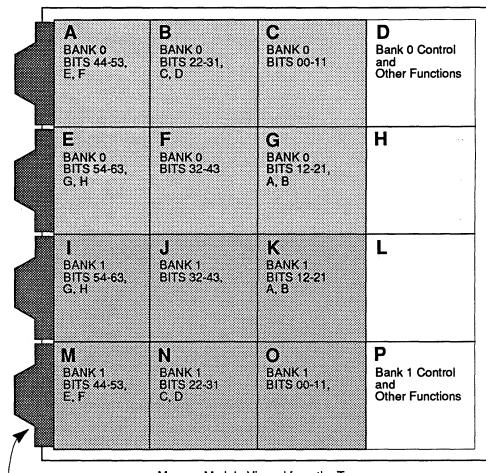

The CRAY-3 system Common Memory consists of 512 storage banks of up to four million words each. Each word consists of 64 data bits and eight error correction bits. This memory is shared by the Foreground Processor, Background Processors and peripheral equipment controllers. It contains program code for the Background Processors as well as data for problem solution. System tables are located here for the Foreground Processor but foreground program code is not. Data buffers for the disk files are also located in Common Memory.

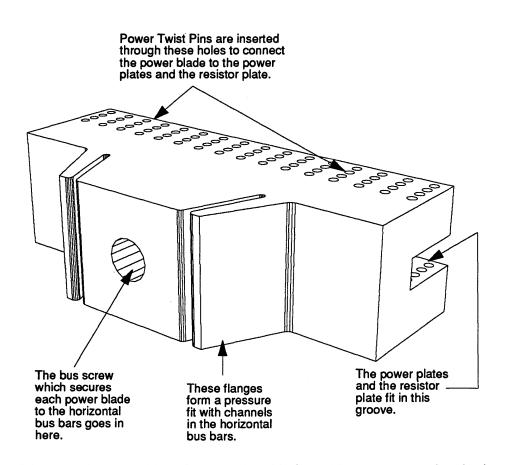

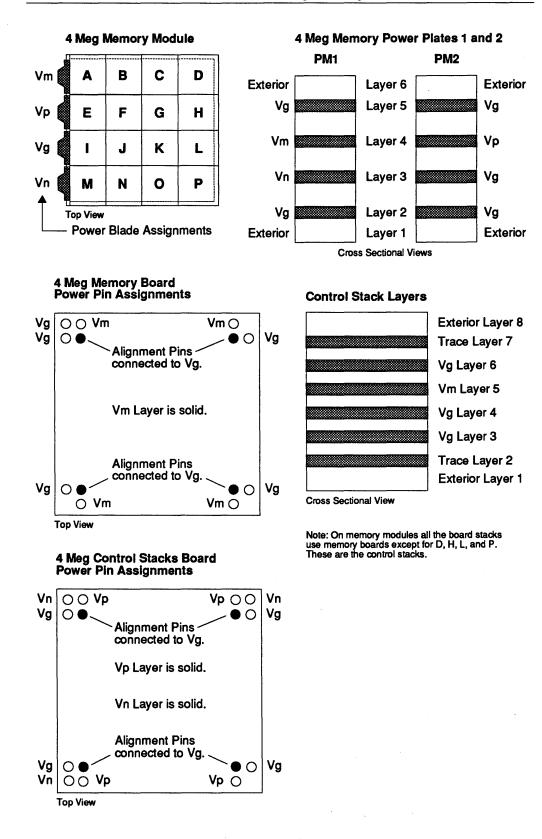

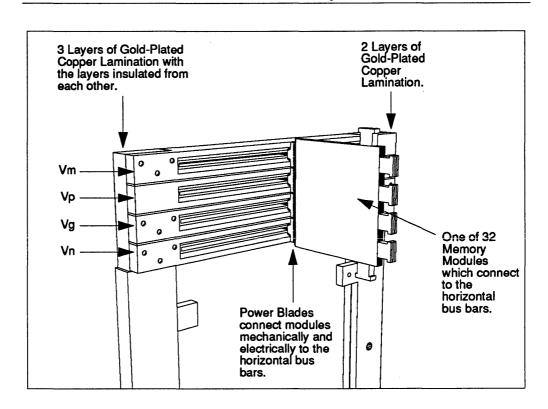

Power Blades

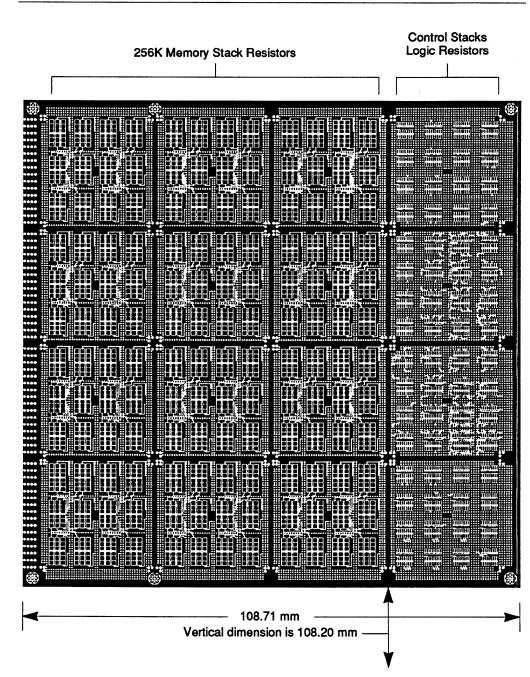

Memory Module Viewed from the Top

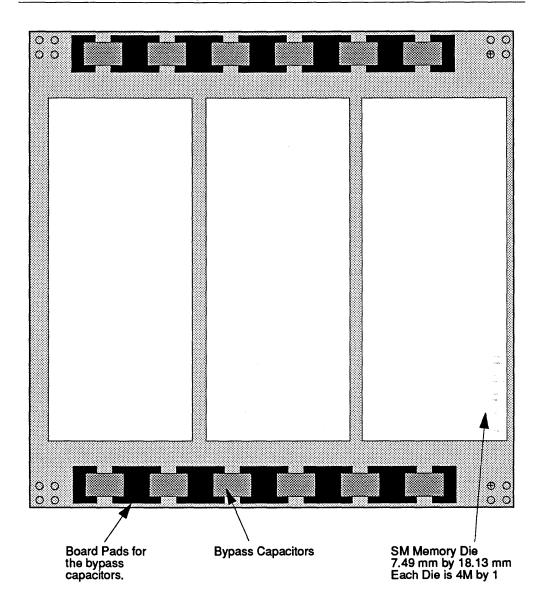

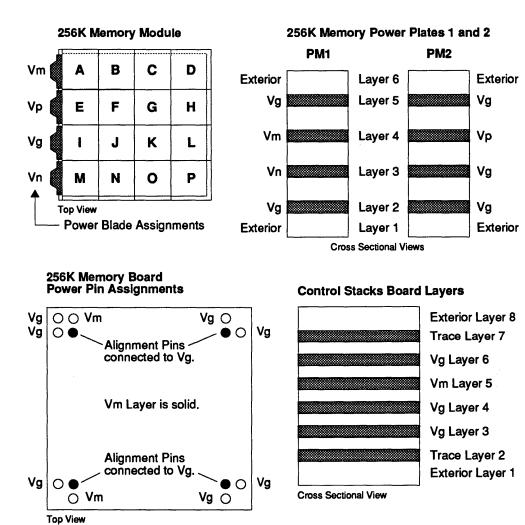

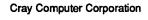

There are two memory banks on each Common Memory module. Each memory bank occupies six out of the sixteen stacks on a module. The remaining four stacks are control stacks (see Figure 11). A memory bank can utilize 16 background processor memory access ports. Total memory bandwidth is 128 gigabytes per second. Total memory capacity is eight gigabytes. Each Background Processor can read and write a word of data per clock period (two nanoseconds) in a vector mode.

The silicon Static Random Access Memory integrated circuits used in Common Memory each contain either 262,144 or 4,194,304 bits of data (with enhanced memory). A memory bank consists of 288 of the 256K-by-1 SRAM integrated circuits or 72 of the 4M-by-1 SRAM integrated circuits. A memory module then contains 576 x 256K or 72 x 4M bits of data plus logic circuits to support the memory access paths. Memory access time at the circuit level is 22 nanoseconds. Memory cycle time is 30 nanoseconds.

The memory enhancement for the CRAY-3, under development as this revision was published, would increase the Common Memory of the machine four times per octant of memory. With the 4 meg SRAM circuit enhancement a four-processor CRAY-3 (two octants) would contain 512 million words of Static Random Access Memory. A 16-processor machine would contain two gigawords of Common Memory.

The CRAY-3 GaAs integrated circuits are significantly faster than the memory circuits. This speed discrepancy is used to minimize the number of physical data paths that are necessary to connect the 512 memory bank modules to the 32 memory ports. Data is transferred by utilizing an 18-bit packet. The 64-bit data word and eight error correction bits require a four clock period transmission time—18 bits per clock period. There are independent read and write packets between the memory bank and access port. Memory bank address utilizes a 12 bit packet. The 24 bit internal bank address requires a two clock period transmission time between the access port and memory bank—12 bits per clock period.

An eight bit error correction code is generated at the memory access port as the write data is transmitted to the memory bank. This code is interpreted at a readout port for Single Error Correction and Double Error Detection, often abbreviated as SECDED. This allows the computer to continue to properly transfer data to and from common memory even if several single bit errors occur in the data during the transfer or storage process. Double bit errors are also detected but cannot be corrected.

### 1.2.3 Background Processing

The Background Processors in the CRAY-3 system are composed of processing elements similar to those in a CRAY-2 processor. The CRAY-3 instruction set includes similar registers and arithmetic functions, retaining all of the CRAY-2 instructions. Some of the instruction source and destination register designators have been changed to provide consistency and logical simplification.

Eight new instructions have been added as summarized in the following table:

| Machine<br>Code | CALI              | nstruction        | Description                                                                    |

|-----------------|-------------------|-------------------|--------------------------------------------------------------------------------|

| 001             | CMR               |                   | Complete memory references.                                                    |

| 023ij1          | Ai                | A <sub>j</sub> +1 | Enter Ai, increment Aj.                                                        |

| 035-j-          | RT                | Sj                | Copy S <sub>j</sub> to RT (Monitor Mode only).                                 |

| 074i            | Vi                | [im]              | Direct read V <sub>i</sub> from Local Memory.                                  |

| 075i            | [lm]              | Vi                | Direct write Vi to Local Memory.                                               |

| 134ijk          | Vi                | <aj, ak=""></aj,> | Two-port read V <sub>i</sub> from CM (A <sub>j</sub> ) stride A <sub>k</sub> . |

| 135ijk          | <aj, ak=""></aj,> | Vi                | Two-port write V <sub>i</sub> to CM (A <sub>j</sub> ) stride A <sub>k</sub> .  |

| 177             | PASS              |                   | No-op.                                                                         |

TABLE 2. New Instruction Codes for the CRAY-3.

Computation in a background mode implies a memory-to-memory computation. A job is initiated by the Foreground Processor. Data is moved from the disk files to the semiconductor memory under Foreground Processor supervision. The program code for the Background Processors is positioned in the Common Memory and the computation field is defined. The Foreground Processor then initiates the background computation using one or more Background Processors as required. The Background Processors may call for further peripheral activity through the Foreground Processor as the computation proceeds.

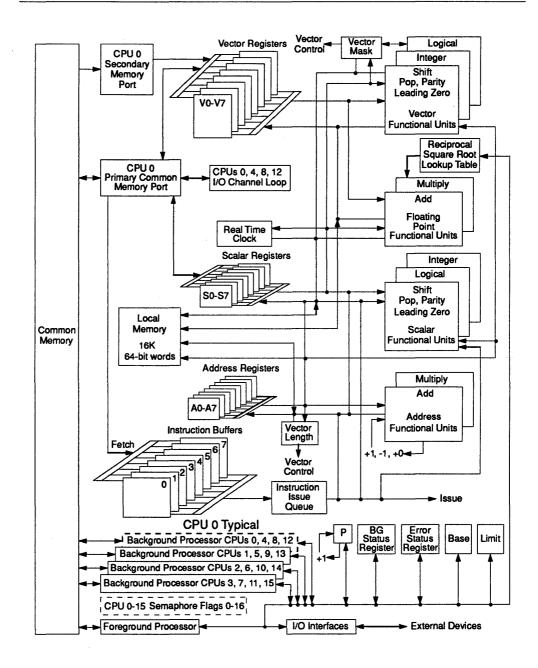

Figure 12 contains a diagram illustrating the architecture of a CRAY-3 Background Processor.

FIGURE 12. Block Diagram of a Background Processor.

Each background processor has a small high speed local memory to hold scalar or vector operands during a computation (16,384 words are available for each Background Processor). Data is moved from the Common Memory to the local memory and returned at the end of each computation. Arrays of data are addressed by the Background Processors directly in the Common Memory. The access to data common to multiple Background Processors is interlocked by the Background Processor semaphore flags. Resources of a Background Processor are summarized in the following table:

| Functional<br>Division             | Function<br>Performed                       | Specification                 |

|------------------------------------|---------------------------------------------|-------------------------------|

| Eight S Registers                  | Scalar operands                             | 64 bit length                 |

| Eight A Registers                  | Address and integer operands                | 32 bit length                 |

| Eight V Registers                  | Vector segments                             | 64 elements of 64 bits        |

| Instruction Buffer                 | Instruction loops                           | 512 parcels of 16 bit length  |

| Local Memory                       | Address, Scalar and Vector register backup  | 16,384 words of 64 bit length |

| Floating Point<br>Functional Units | Computation in 64 bit floating point mode   |                               |

| Integer Functional<br>Units        | Computation in 64 bit integer mode          |                               |

| Address<br>Functional Units        | Computation in 32 bit integer mode          |                               |

| Vector and Scalar<br>Logical Units | 64 bit logical computations                 |                               |

| Vector and Scalar<br>Shift Units   | Shifts, population, and leading zero counts |                               |

TABLE 3.

Resources of a CRAY-3 Background Processor.

Figure 13 shows how the different functions of each Background Processor are distributed among the four modules which comprise each Background Processor.

| ONE BACKGROUND PROCESSOR              |                                       |                                       |                                       |

|---------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|

| A Module                              | B Module                              | C Module                              | D Module                              |

| Scalar Registers<br>Bits 00-15        | Scalar Registers<br>Bits 16-31        | Scalar Registers<br>Bits 32-47        | Scalar Registers<br>Bits 48-63        |

| Vector Registers<br>Bits 00-15        | Vector Registers<br>Bits 16-31        | Vector Registers<br>Bits 32-47        | Vector Registers<br>Bits 48-63        |

| Local Memory<br>Bits 00-15            | Local Memory<br>Bits 16-31            | Local Memory<br>Bits 32-47            | Local Memory<br>Bits 48-63            |

| Integer Add,<br>Logical,<br>Mask, RTC | Integer Add,<br>Logical,<br>Mask, RTC | Integer Add,<br>Logical,<br>Mask, RTC | Integer Add,<br>Logical,<br>Mask, RTC |

| Bits 00-15                            | Bits 16-31                            | Bits 32-47                            | Bits 48-63                            |

| Address Registers                     | Branch Control                        | Floating Multiply                     | Instruction Issue<br>Control          |

| Address Multiply                      | Program Register                      | Reciprocal<br>Approximation           | Instruction Buffers                   |

| Address Add<br>Scalar Shift           | Floating Add                          |                                       | Foreground<br>Interface               |

| Vector Length<br>Register             |                                       |                                       | Vector Shift                          |

| Common Memory<br>Address              | Common Memory<br>Write                |                                       | Common Memory<br>Read                 |

FIGURE 13. Background Processor Functional Divisions Among the Modules.

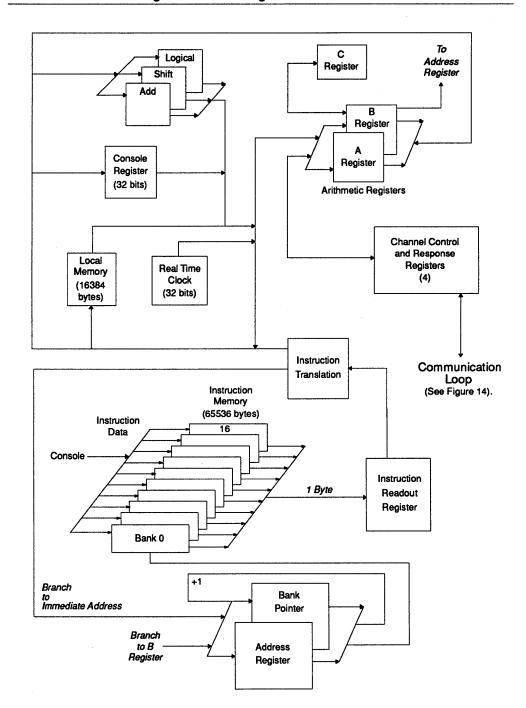

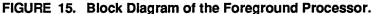

#### 1.2.4 Foreground Processing

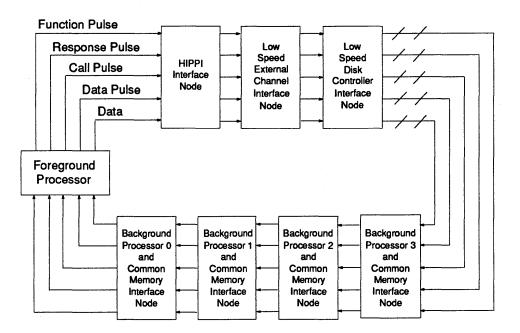

The Foreground Processor supervises overall system activity and responds to requests for interaction between the system members. System communication is accomplished through four, high-speed synchronous data channels. These channels interconnect the Background Processors, Foreground Processor, disk control units and host system interfaces. The Foreground Processor does not execute the system program code.

The Foreground Processor code is loaded at deadstart from a file on the maintenance console. This memory then becomes a read only memory. It cannot be altered during the operation of the system. Data for supervision of the system is maintained in the Common Memory and is moved to the Foreground Processor's local data memory as required.

#### FIGURE 14. Data Channels (One of Four).

The primary function of the Foreground Processor program is to poll the four communication channel loops for requests from the Background Processors and control the communications on the four channel loops to facilitate data transfers between controllers on the channels. Many of the requests that will be recognized by the Foreground Processor require responses within a microsecond or less.

Since the majority of Foreground Processor activity involves data transfer between the disk file storage units and the common semiconductor memory, the system provides for a mixture of 12 megabytes per second disk file storage unit interfaces and 100 megabytes per second interfaces to main storage sub-systems such as disk arrays.

The Foreground Processor is divided into seven operational sections: 1) deadstart circuits, 2) instruction issue mechanism, 3) local data memory, 4) channel communication, 5) functional units, 6) console communications and

7) real time clock. Resources of the Foreground Processor are summarized in the table below:

| Functional<br>Division            | Functional<br>Purpose               | Specification                                      |

|-----------------------------------|-------------------------------------|----------------------------------------------------|

| Local Data Memory                 | Temporary storage                   | 4096 words of 32 bit length.                       |

| Instruction Memory                |                                     | 65,536 bytes of 8 bit length arranged in 16 banks. |

| Integer Functional<br>Units       | Computation in 32 bit integer mode. |                                                    |

| Four<br>Communication<br>Channels |                                     | One gigabyte per second each.                      |

TABLE 4.

Resources of the Foreground Processor.

## 1.3 CRAY-3 Product Description

We will conclude Chapter 1 by giving a brief product description of the CRAY-3 supercomputer system. This description will summarize the basic features of the CRAY-3 in terms of hardware, software, processor capabilities and peripheral and network interfaces. This summary of the CRAY-3 is given in Table 5, below:

| Hardware                     |                                                                                                             |  |

|------------------------------|-------------------------------------------------------------------------------------------------------------|--|

| Feature                      | Specification                                                                                               |  |

| Background Processors (CPUs) | 1, 2, 4, 8 or 16                                                                                            |  |

| Memory Size                  | 128, 256, 512, 1024 or 2048 Million Words<br>1 Bank per Million Words up to 512<br>64 Bit Words with SECDED |  |

| Foreground Processor         | 1 (I/O and System Control Processor)                                                                        |  |

| External I/O Channels        | 8 to 60                                                                                                     |  |

| I/O Transfer Rate            | Up to 4 Gigabytes per Second                                                                                |  |

| Clock                        | 2 Nanosecond (500 Megahertz)                                                                                |  |

| Memory Transfer Rate         | 1 Gigaword per Processor per Second<br>16 Gigawords per second for a full system                            |  |

| Peak Performance             | 1 Gigaflop per Processor<br>16 Gigaflops for a full system                                                  |  |

#### TABLE 5. CRAY-3 Features Summarized.

| Software              |                                                                                    |

|-----------------------|------------------------------------------------------------------------------------|

| Feature Specification |                                                                                    |

| Operating System      | Extended UNIX                                                                      |

| Compilers             | Fortran 77<br>Standard C<br>Both have extensions for Vectors and<br>Multi-tasking. |

| Networks              | TCP/IP                                                                             |

| User Tools            | Editors<br>Debugger                                                                |

| Background Processor |                                                                                                         |  |  |

|----------------------|---------------------------------------------------------------------------------------------------------|--|--|

| Feature              | Specification                                                                                           |  |  |

| Functional Units     | 3 Vector<br>3 Scalar<br>2 Floating Point (Shared Vector/Scalar)<br>1 Address                            |  |  |

| Registers            | 8 Vector<br>1 Vector Mask<br>1 Vector Length<br>8 Scalar<br>8 Address<br>1 Program<br>1 Base<br>1 Limit |  |  |

| Instruction Stack    | 128 64-Bit Words                                                                                        |  |  |

| Real Time Clock      | 64 Bits                                                                                                 |  |  |

| Local Memory         | 16,384 Words                                                                                            |  |  |

| Semaphore Flags      | 17                                                                                                      |  |  |

| Ports to Memory      | 2 (1 Input and 1 Output)                                                                                |  |  |

| Peripheral and Network Interfaces |                                                                                                                                                |  |  |

|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Feature                           | Specification                                                                                                                                  |  |  |

| Networks                          | HIPPI (100 MBytes per Second)<br>HYPERchannel by Network Systems<br>Corp.<br>VME via Cray Research, Inc. FEI-3<br>Ultra Technologies via HIPPI |  |  |

| Disk Storage                      | RAID Disks via HIPPI<br>Cray Research, Inc. DD-49 and DD-40                                                                                    |  |  |

To enable a machine to perform billions of operations every second you must have thousands upon thousands of switching circuits that are very fast and very close together. The design and packaging of the CRAY-3 is certainly a case of form following function with a logic gate density of 96,000 per cubic inch. In the next chapter we turn our attention to the smallest building blocks that make up the CRAY-3: the components inside the CRAY-3 GaAs integrated circuit packages.

This chapter first presents a summary of some of the principles involved in designing the very small electronic components that make up the Gallium Arsenide integrated circuits used in the CRAY-3. It continues with a discussion of the basic logic cells used to construct a CRAY-3 integrated circuit. The chapter concludes with a discussion of the CRAY-3 Cell Library.

# 2.1 GaAs Component Design

Circuit component design in GaAs is a relatively open affair. In the silicon world, circuit design usually involves an array of gates in which the diffusion set is a constant over a large number of circuit types (gate array based). A metallization variation provides the unique combination of logic functions required. In our use of gallium arsenide, the design begins with the basic substrate for each unique circuit package (standard cell based).

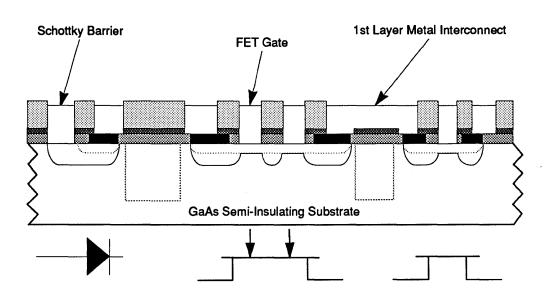

The field effect transistors used in GaAs circuits are slightly different from the equivalent transistors in silicon circuits. The reason for this difference is that in silicon a metal oxide is formed over the substrate. In GaAs this is not the case since it is difficult to grow a stable oxide. Hence, field effect transistors in silicon are Metal Oxide Semiconductors (MOSFETs) while FETs in GaAs are Metal Semiconductors (MESFETs). The gate metal, which causes the field effect, is also a Schottky diode in GaAs circuits. This means that gate current will occur as the gate voltage becomes positive with respect to the source by

about 600 millivolts. In the case of silicon, the gate metal is not a diode and no current flows.

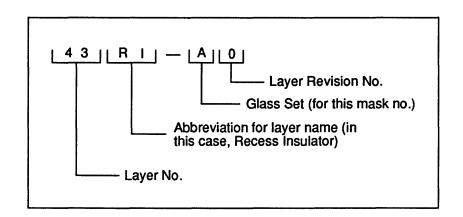

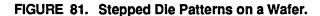

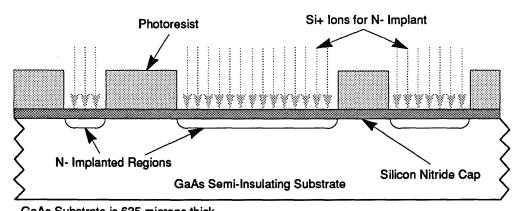

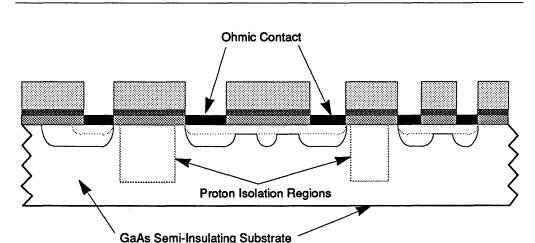

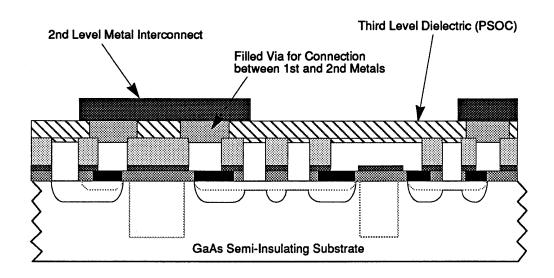

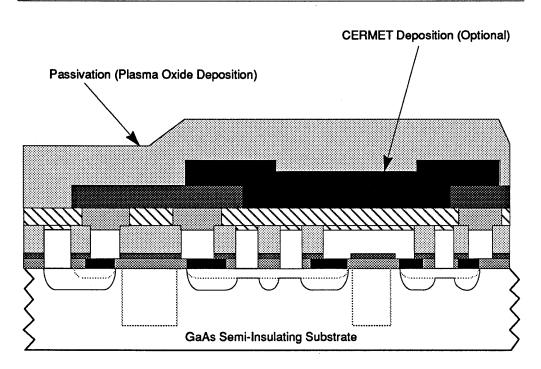

Circuit design for the CRAY-3 logic circuits involves eight levels of masks. There are actually a total of ten masks used in the GaAs foundry process. However, the first mask (alignment marks) and the last mask (passivation openings) are not unique to the individual circuits and are reused over the entire logic family. The fifth mask (proton isolation) is derived from the second and third mask and requires no additional design. The masks which are unique to the individual circuit design are assigned a letter designation for each mask level. These letter designations and their meaning are shown in the following table:

| Mask Level | Process and Function                                                                                                                                                                | CrayDraw<br>Layer | Standard<br>CrayDraw<br>Color |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------------------------------|

| Level A    | N- Implant. Semiconducting<br>Channel.                                                                                                                                              | Layer 1           | Red                           |

| Level B    | N+ Implant. Essentially<br>terminates the semiconducting<br>channel.                                                                                                                | Layer 2           | Green                         |

| Level C    | Ohmic Metal. Metal terminals for the elements of a device.                                                                                                                          | Layer 3           | Yellow                        |

| Level D    | First Layer Metal. Used for<br>connections between devices.<br>Forms a Schottky Diode without<br>Ohmic Metal.                                                                       | Layer 4           | Blue                          |

| Level E    | Via Windows. Used to make<br>openings in the dielectric between<br>First Layer Metal and Second<br>Layer Metal so the two layers can<br>be connected electrically at that<br>point. | Layer 5           | Magenta                       |

| Level F    | Second Layer Metal. Used for connections between devices.                                                                                                                           | Layer 6           | Cyan                          |

| Level H    | Recess Insulator. Makes an<br>opening in the dielectric (insulator)<br>so the gate metal can be lowered<br>to the semiconducting channel.                                           | Layer 8           | Tan                           |

#### TABLE 6. Layers Used in the Design of CRAY-3 IC Components.

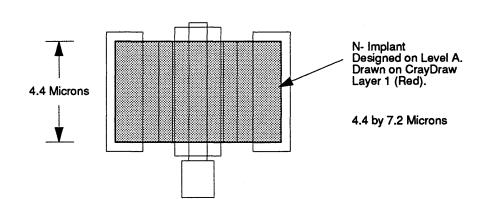

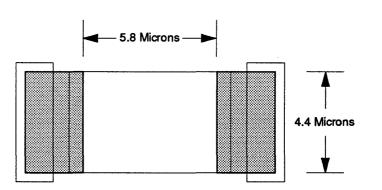

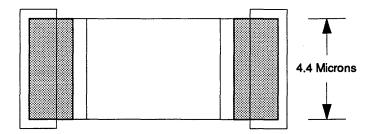

Figures 16 through 20 illustrate the design of a 4.0 micron wide transistor with an individual level shaded in each of the five drawings. A 4.4 micron field effect transistor will represent the smallest FET used in the CRAY-3. All

devices are drawn 0.4 microns wider than needed to compensate for the shrinking of 0.4 microns during the fabrication process. All drawings of CRAY-3 ICs are made on a 0.1 micron grid using CrayDraw (an in-house custom designed Computer Aided Design program) or Cadence (a commercial CAD program). Only objects which can be made of rectangular structures with edges on the grid are allowed.

# 2.2 Transistor Design

A field effect transistor consists of a source element, a gate element and a drain element. Electrons flow through a semiconducting channel from the source to the drain. The gate controls the amount of current which flows through the semiconducting channel. The design of a 4.0 micron wide transistor is illustrated in Figures 16 through 20. The source and drain elements are symmetrical and the drain is determined by whichever element has the higher external voltage applied.

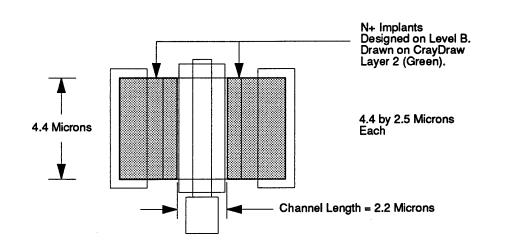

The semiconducting channel is illustrated in Figure 16. The width of the channel is the vertical dimension of the shaded area as drawn. This is by definition the width of the transistor. In this case the channel is drawn 4.4 microns wide. The length of the channel is the space from the N+ implant on the source side of the gate to the N+ implant on the drain side of the gate. All transistors used in CRAY-3 circuit designs have a channel length of 2.2 microns (see Figure 17).

FIGURE 16. 4.0 Micron Transistor—Semiconducting Channel.

Figure 17 has the areas of N+ implant shaded. The sheet resistance of the N+ implant is approximately 400 ohms per square and the sheet resistance of the N- implant is approximately 440 ohms per square. The double implanted area essentially terminates the effective transistor channel. The N- implant continues the length of the N+ implant and overlaps it. This makes the implant under the ohmic metal as highly doped as possible.

FIGURE 17. 4.0 Micron Transistor—N+ Implants.

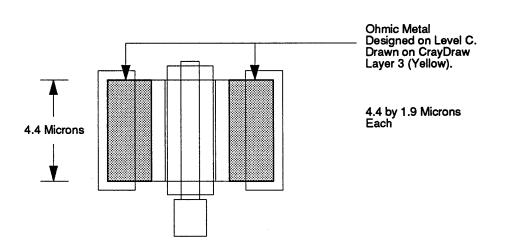

Figure 18 shades the areas of the transistor design which have ohmic metal. The ohmic metal breaks down the substrate surface barrier which would otherwise result in a Schottky diode. These two areas of ohmic metal are essentially the metal terminals of the transistor for the source and the drain elements.

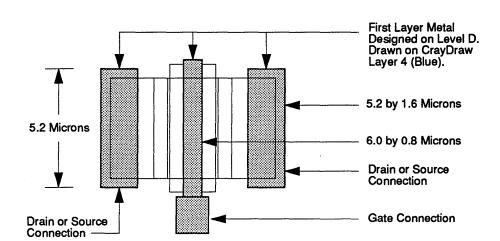

Those areas of the transistor design which have first layer metal are illustrated in Figure 19. These metal paths on the source and drain connections of the transistor are 16 grid units wide, or 1.6 microns in width, and are used to connect the device to other portions of an integrated circuit package. The gate metal is narrowed to 0.8 microns as it passes over the N- implant channel to reduce the electrical capacitance of the gate metal to the channel. This capacitance is one of the components which determines the speed of the transistor.

FIGURE 19. 4.0 Micron Transistor—First Layer Metal.

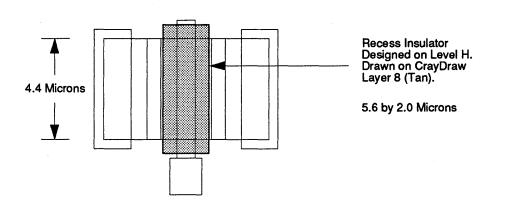

A recess opening, which is shown in Figure 20, is made through the dielectric over the channel. The gate metal is lowered to the channel implant through this opening to make the device. All other metals except ohmic metal stay on top of the dielectric to reduce current leakage paths to the GaAs substrate.

The electrical characteristics of a transistor are shown in the graph in Figure 21. The horizontal coordinate is the drain voltage with respect to the source voltage. The vertical coordinate is the amount of current that flows in the drain as a function of drain voltage and gate voltage.

FIGURE 21. Electrical Characteristics of a Transistor.

The graph shows five curves of drain current versus drain voltage for five constant gate voltages. The curve labeled Vgs = 0 volts has special significance because this is the curve applicable to transistors used as current sources. The point on this curve where the drain voltage is 2.5 volts has additional significance. The current at this point is chosen as a parametric reference for the amount of current capacity in the transistor. This current value has a special label (Idss). Idss stands for the drain current (Id) with the gate voltage at the source supply voltage (ss).

The gate voltage which causes the drain current to become zero also has a special name. This is called the transistor pinch-off voltage. Gate voltages more negative than the pinch-off voltage have no additional effect. There is a

relationship between the pinch-off voltage as defined above and the drain voltage which causes the curves in the graph to break and become more or less flat. This is approximately the same voltage value. The design pinch-off voltage for the CRAY-3 transistors is -0.55 volt. Actual values range from -0.48 volt to -0.62 volt.

## 2.3 Current Source Design

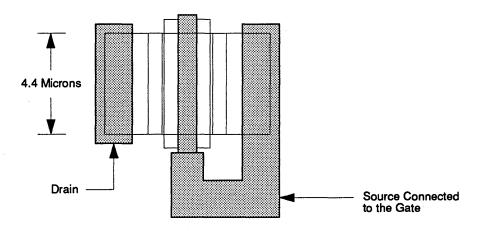

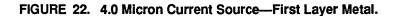

Current sources can be used instead of resistors in many design applications. The current sources give a sharper transition to the electrical signals than a resistor and usually take less space. A current source is essentially a transistor with the gate element tied electrically to the source element. The electrical characteristic of the current source is therefore limited to one of the curves in the graph in Figure 21. This is the drain current versus the drain voltage curve with the gate voltage zero.

The design of a 4.0 micron wide current source is illustrated in Figure 22. Most of the description of transistor design applies to this device as well. The same five drawing types illustrated in Figures 16 through 20 would illustrate the five levels of process masks used in a current source design. The only difference between the current source design illustrated and the 4.0 micron transistor design previously described is the connection of the gate metal to the source metal. This is best shown when the first layer metal is shaded, as in Figure 22.

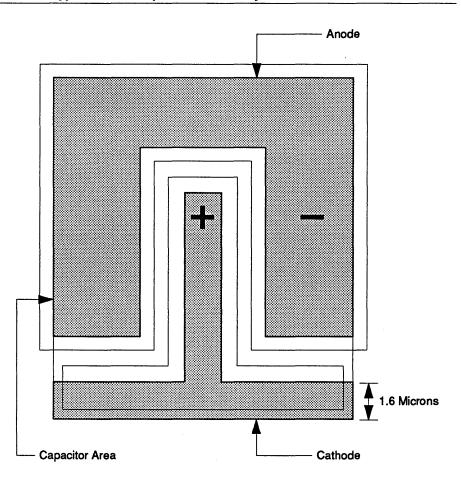

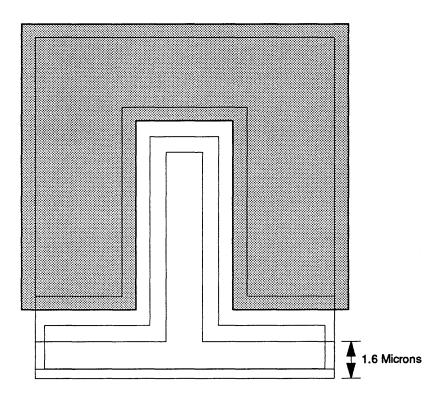

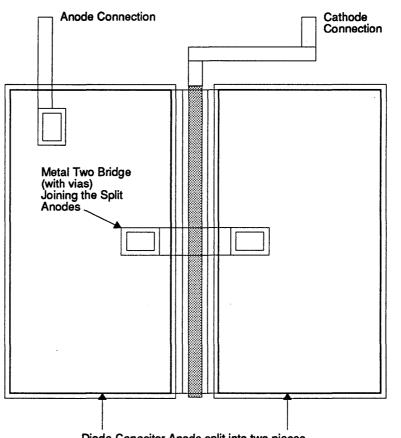

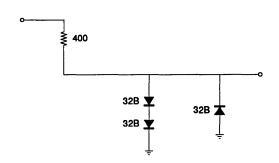

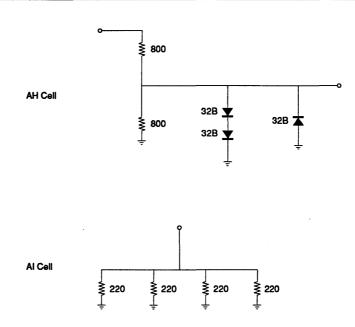

### 2.4 Diode Design

Diodes are easy to come by in gallium arsenide circuit design. Whenever first layer metal passes over an implanted area of the substrate a Schottky diode is formed. The electrical characteristics of the diode depend on the size of the metal overlapping the implant area and the resistance of the implant path to an ohmic contact.

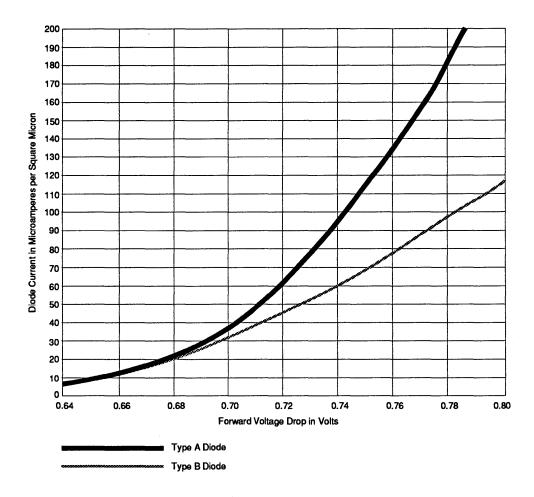

There are two styles of N+ only diode configurations used in CRAY-3 circuit design. These are labeled type A diodes and type B diodes. The type A diode has a path resistance of 200 ohms per square micron of diode area. The type B diode has a path resistance of 650 ohms per square micron of diode area. The type A diode is used exclusively as the logic forming input device for cell structures (the logic gates). The type B diode is used for level shifting and clamping functions.

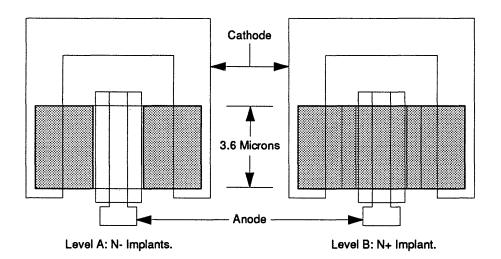

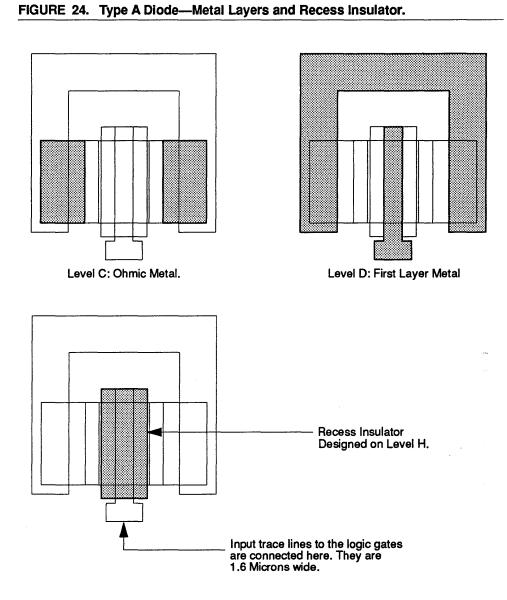

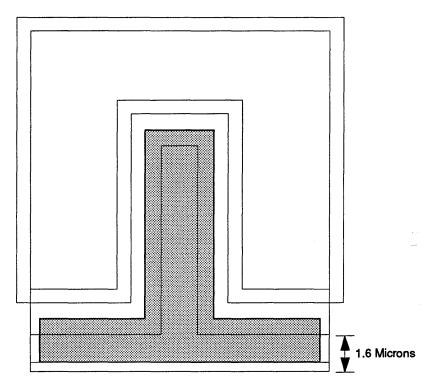

The design of a type A diode is illustrated in the five drawings in Figures 23 and 24. These drawings are the same except for the shading used to illustrate the contribution of the five levels of process masks used in diode fabrication. The anode of the diode is the small metal finger with an external connection in the center of the drawing for level D. The cathode is the larger surrounding metal.

#### FIGURE 23. Type A Diode (3 Square Micron)-N- and N+ Implants.

The contact area of the diode is that portion of the anode finger which is over the implant field. This is a rectangular area 0.8 microns by 3.6 microns in size. Total area is approximately 3 square microns. There is an ohmic contact on each side of the anode finger. This design is aimed at a configuration with minimum diode resistance per unit area.

3207 - CRAY-3 Hardware Description Manual

37

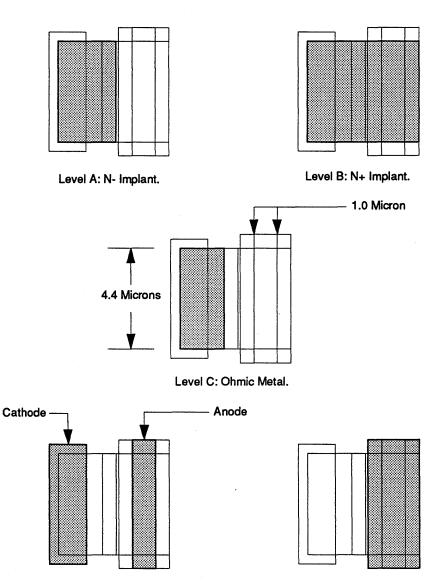

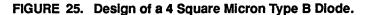

A type B diode with a 4.0 square micron diode contact area is illustrated in Figure 25. These dimensions are considerably more relaxed than the dimensions for the type A diode. The anode finger for this configuration is the right metal path in the drawing for level D. The cathode is the left metal path. The area of the diode in this configuration is 4.0 microns by 1.0 micron.

Level D: First Layer Metal.

The implant areas are identical in this design as they were in the design of the type A diode. The advantage of the type B diode is the better process yield and the greater diode area in a given amount of package real estate.

The type A and type B diodes have differing electrical characteristics as a result of the difference in resistance to the ohmic contact. Plots of the forward voltage drop versus forward current are shown in the graph in Figure 26. The type B diode curve is approaching a straight line toward the right of the graph. This is because the 650 ohm forward resistance of the diode is dominating the electrical characteristics in this current range.

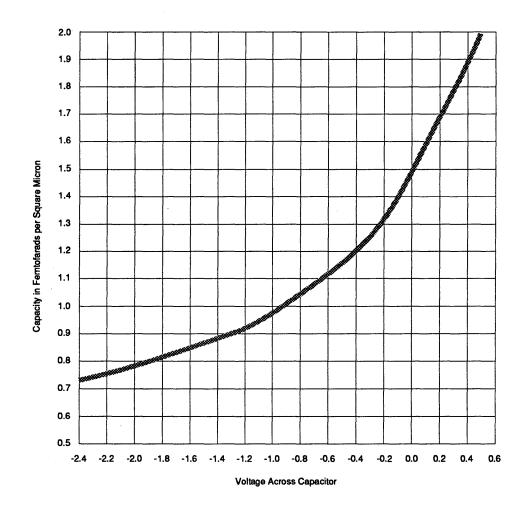

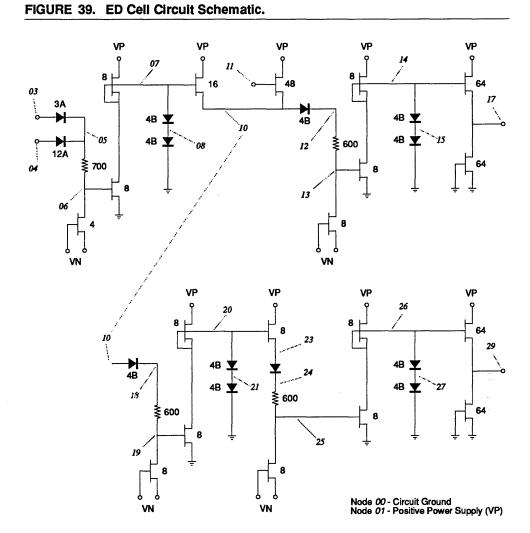

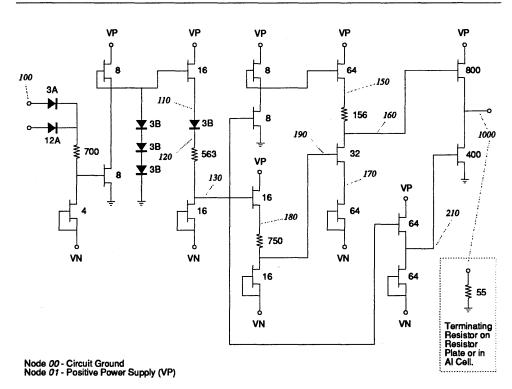

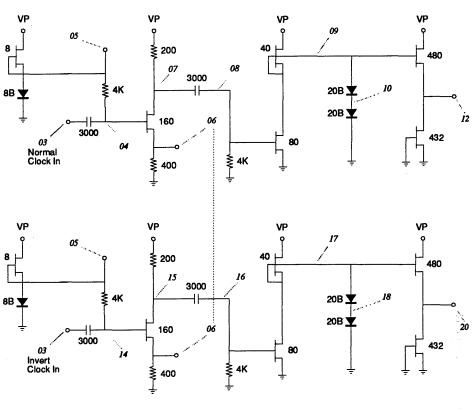

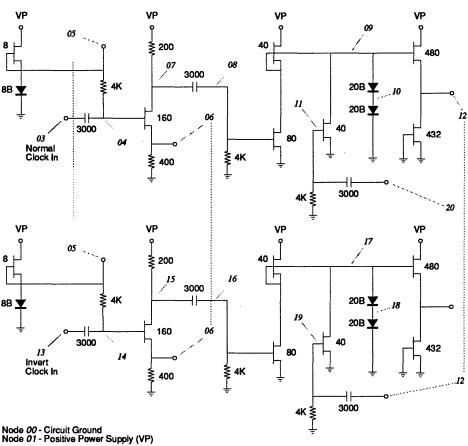

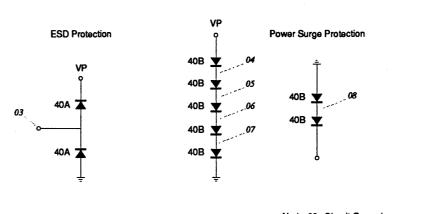

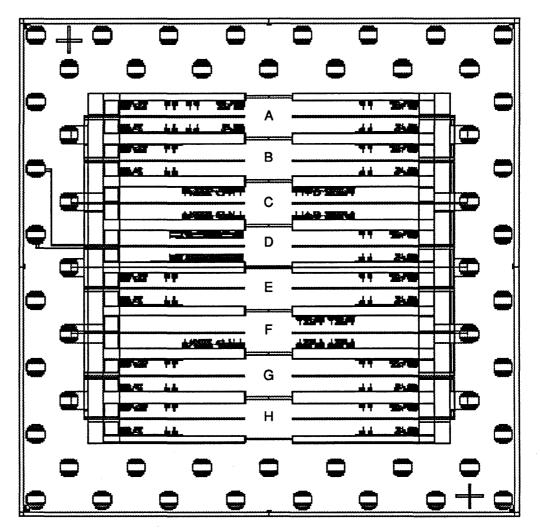

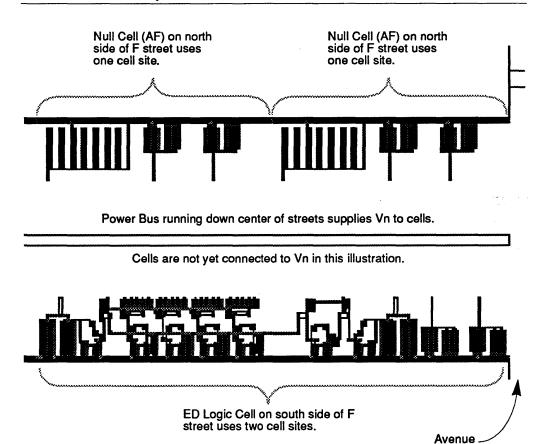

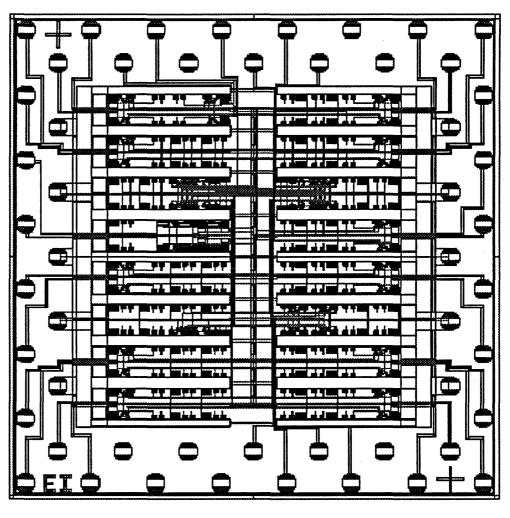

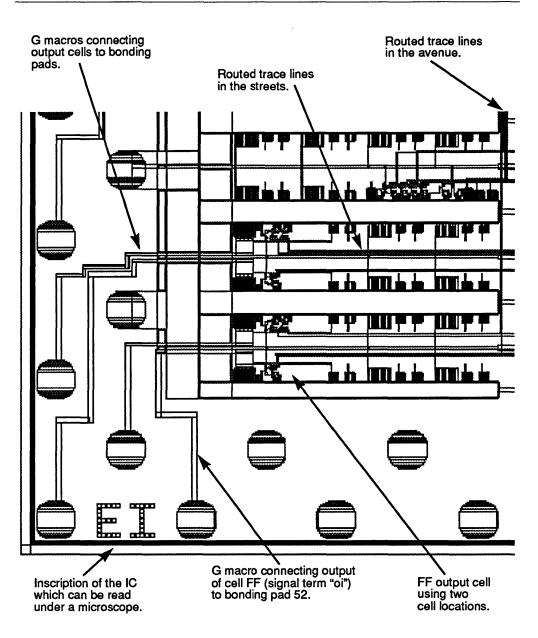

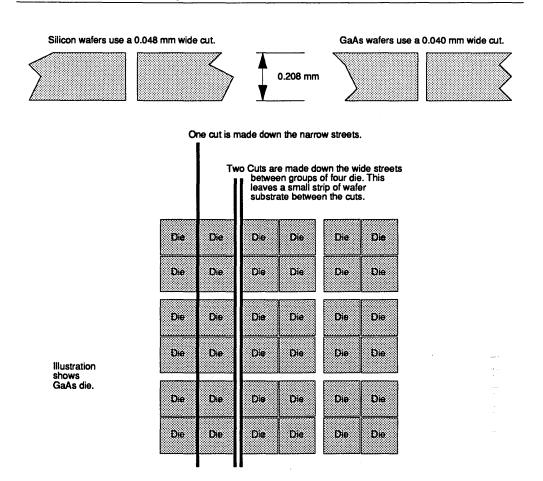

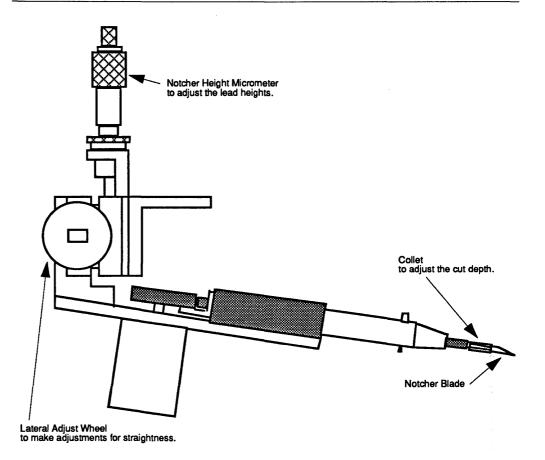

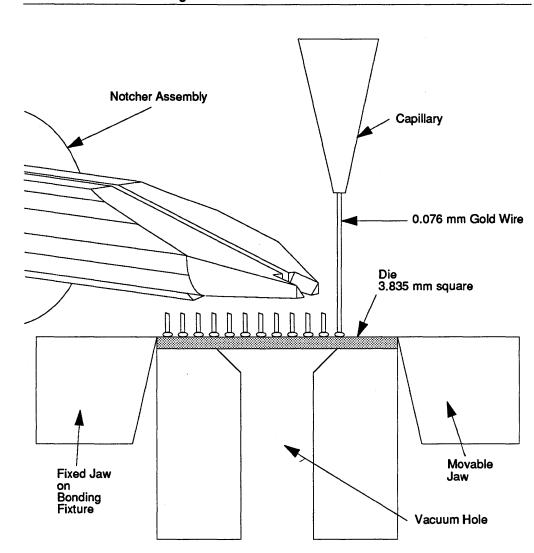

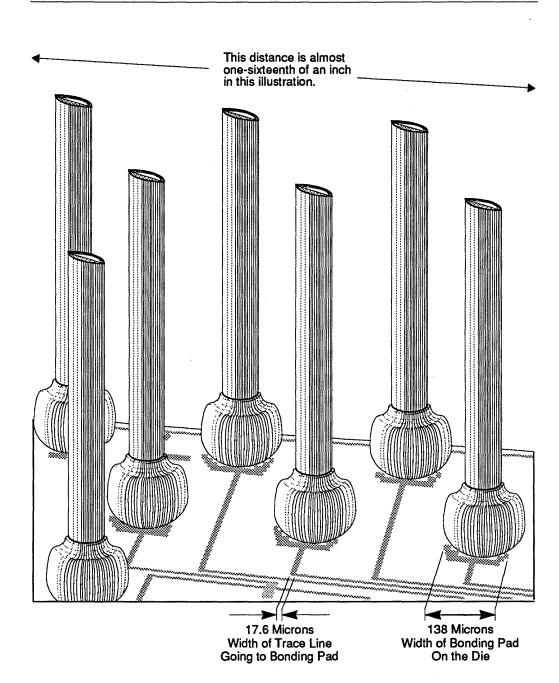

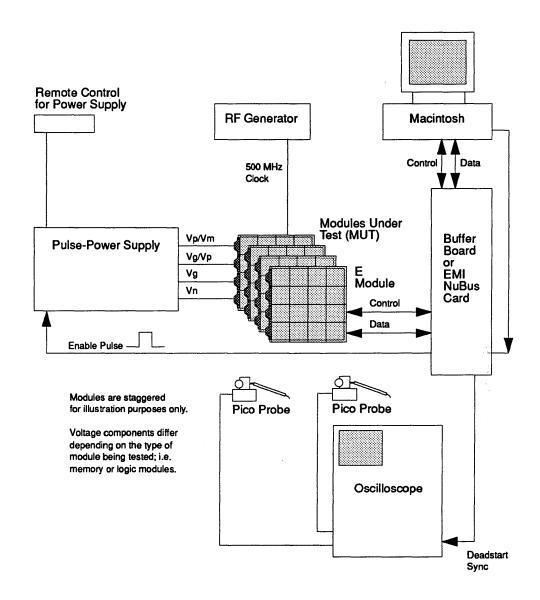

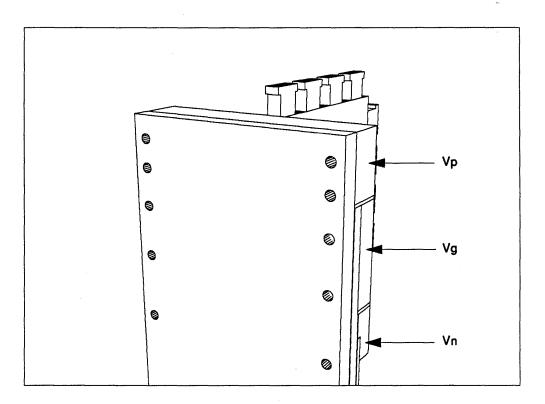

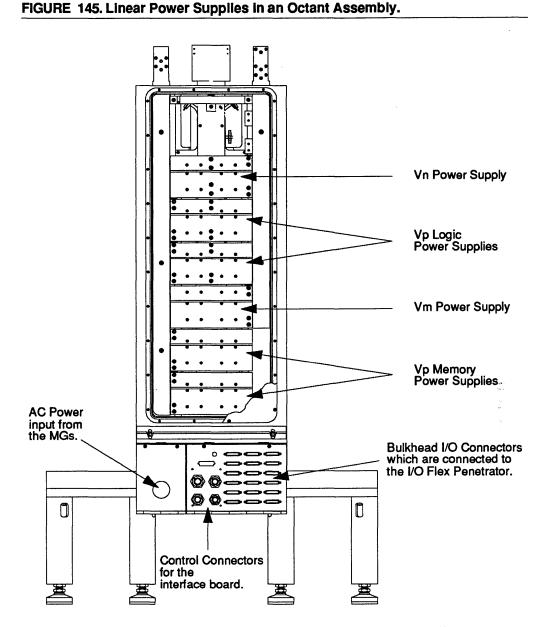

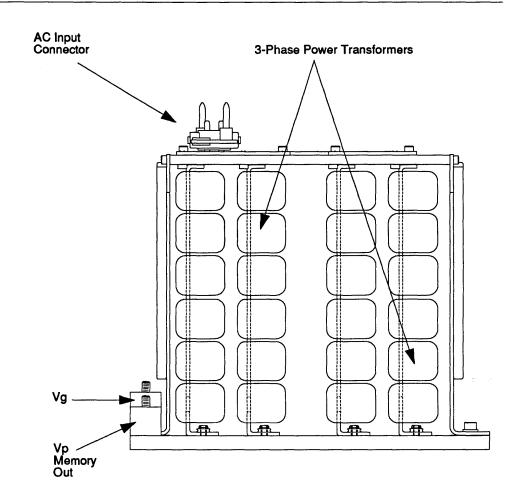

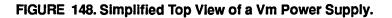

The type A diode has a much steeper curve in the voltage and current ranges shown. The type A diode curve is just beginning to straighten at the top of the graph. This slope represents the forward resistance of 200 ohms. Both curves reflect an underlying exponential component which becomes resistive when the current is high enough.