# **CRAY-2<sup>®</sup> Computer Systems** Functional Description Manual

HR-02000-0D

Cray Research, Inc.

RD-9248-00-N04

(

## **Record of Revision**

Each time this manual is revised and reprinted, all changes issued against the previous version are incorporated into the new version and the new version is assigned an alphabetic level which is indicated in the publication number on each page of the manual.

Changes to part of a page are indicated by a change bar in the margin directly opposite the change. A change bar in the footer indicates that most, if not all, of the page is new. If the manual is rewritten, the revision level changes but the manual does not contain change bars.

| REVISION | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | May 1985 - Original printing.                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Α        | October 1986 - This reprint with revision corrects various errata and improves the format of the manual. New instructions and CAL examples were added to section 3. A reference to pseudobanking was added to section 4. The name of a controller was changed to External I/O controller from Front-end Interface due to confusion with another device. All previous versions are obsolete. All trademarks are now documented on the back of the title page. |

| B        | February 1987 - This reprint with revision incorporates the HSX channel and the 128-<br>Mword Common Memory four-processor and two-processor versions of the CRAY-2<br>computer system.                                                                                                                                                                                                                                                                      |

| С        | July 1987 - This reprint with revision incorporates the 64-Mword static Common<br>Memory two-processor and the 128-Mword static Common Memory four-processor<br>versions of the CRAY-2 computer system. It also removes reference to the 128-Mword<br>dynamic Common Memory two- and four-processor CRAY-2 computer systems.                                                                                                                                 |

| 01       | November 1988 - This change packet incorporates the 512-Mword dynamic Common<br>Memory four-processor version of the CRAY-2 computer system. It also contains<br>information on the increased buffer size for the CRAY-2 computer system.                                                                                                                                                                                                                    |

| D        | June 1989 - This reprint with revision adds information on vector tailgating and Shared<br>registers now offered on the CRAY-2 computer system. It also incorporates various<br>technical corrections and change packet 01. The publication number has been changed<br>from HR-2000 C to HR-02000-0D.                                                                                                                                                        |

## PREFACE

This manual describes the functions of the CRAY-2 computer system and the Cray Assembly Language (CAL) version 2 symbolic machine instructions specifically used with this machine. It is written to assist programmers and engineers, and the manual assumes the readers have a familiarity with digital computers and assemblers.

The manual describes the overall computer system including its configuration and characteristics. It also describes the operation of the Common Memory, Foreground Processor, and Background Processors. This manual explains both the machine code and the associated symbolic machine instructions.

Site planning information for the CRAY-2 computer system is available in the CRAY-2 Site Planning Reference Manual, publication number HR-2001.

Additional information on the Cray Assembly Language (CAL) Version 2 is available in the CAL Version 2 Reference Manual, publication SR-2003.

## CONTENTS

| PREE | ACE . | · · · · · · · · · · · · · · · · · · ·              |

|------|-------|----------------------------------------------------|

| 1.   | INTRO | $\underline{DUCTION}$                              |

|      | 1.1   | CRAY-2 COMPUTER SYSTEM FEATURES                    |

|      |       | 1.1.1 Physical characteristics 1-2                 |

|      |       | 1.1.2 Architecture and design 1-4                  |

|      | 1.2   | CONVENTIONS                                        |

|      |       | 1.2.1 Examples                                     |

|      | 1.3   | ORGANIZATION                                       |

| 2.   | BACKG | ROUND PROCESSOR                                    |

|      | 2.1   | CONTROL SECTION                                    |

|      |       | 2.1.1 Instruction issue and control                |

|      |       | Program Address r <b>egis</b> ter                  |

|      |       | Instruction buffers                                |

|      |       | Instruction issue                                  |

|      |       | 2.1.2 Real-time clock                              |

|      |       | 2.1.3 Semaphore flags                              |

|      |       | 2.1.4 Common Memory field protection               |

|      |       | Base Address register 2-4                          |

|      |       | Limit Address register                             |

|      |       | Memory range error                                 |

|      | 2.2   | OPERATING REGISTERS                                |

|      |       | 2.2.1 Address registers                            |

|      |       | Shared registers                                   |

|      |       | 2.2.2 Scalar registers                             |

|      |       | 2.2.3 Vector registers                             |

|      | 2.3   | VECTOR CONTROL REGISTERS                           |

|      |       | 2.3.1 Vector Length register                       |

|      | 2.4   | 2.3.2 Vector Mask register                         |

|      | 4.4   | 2.4.1 Address Add functional unit                  |

|      |       | 2.4.2 Address Multiply functional unit             |

|      |       | 2.4.3 Scalar Integer functional unit               |

|      |       | 2.4.4 Scalar Shift functional unit                 |

|      |       | 2.4.5 Scalar Logical functional unit               |

|      |       | 2.4.6 Vector Integer functional unit               |

|      |       | 2.4.7 Vector Logical functional unit               |

|      |       | 2.4.8 Vector Shift Functional Unit                 |

|      |       | 2.4.9 Floating-point Add functional unit           |

|      |       | 2.4.10 Floating-point Multiply functional unit 2-1 |

|      |       | 2.4.11 Local Memory                                |

|      | 2.5   | ARITHMETIC OPERATIONS                              |

|      |       | 2.5.1 Integer arithmetic                           |

|     | 2.5  | ARITHMETIC OPERATIONS (continued)              |     |

|-----|------|------------------------------------------------|-----|

|     |      | 2.5.2 Floating-point arithmetic                | -12 |

|     |      |                                                | -13 |

|     |      |                                                | -13 |

|     |      | Floating-point addition                        | -14 |

|     |      |                                                | -14 |

|     |      | Floating-point to integer conversion 24        | -14 |

|     |      |                                                | -15 |

|     |      | Floating-point product                         | -15 |

|     |      |                                                | -15 |

|     |      |                                                | -16 |

|     |      |                                                | -18 |

|     |      |                                                | -19 |

|     |      |                                                |     |

| 3.  | BACK | GROUND PROCESSOR SYMBOLIC MACHINE INSTRUCTIONS | -1  |

|     | 3.1  | SYMBOLIC INSTRUCTION FORMAT                    | -1  |

|     | 3.2  |                                                | -2  |

|     | 3.3  |                                                | -3  |

| 4.  | COMM | <u>ON MEMORY</u>                               | -1  |

|     | 4.1  | MEMORY ADDRESSING                              | -1  |

|     | 4.2  | MEMORY ACCESS                                  | -1  |

|     | 4.3  | MEMORY CONFLICTS                               | -2  |

|     | 4.4  | MEMORY BACKUP                                  | -2  |

|     | 4.5  | MEMORY ERROR CORRECTION                        | -3  |

| 5.  | FORE | GROUND SYSTEM                                  | -1  |

| ~ • |      |                                                | -   |

|     | 5.1  | FOREGROUND COMMUNICATION CHANNELS              | -1  |

|     | 5.2  |                                                | -2  |

|     |      |                                                | -3  |

|     |      |                                                | -3  |

|     | 5.3  |                                                | -3  |

|     |      |                                                | -3  |

|     | 5.4  |                                                | -4  |

|     | 5.5  |                                                | -5  |

|     | 5.6  |                                                | -5  |

|     | 5.7  |                                                | -6  |

|     |      |                                                | -   |

|     |      |                                                |     |

### APPENDIX SECTION

| Α. | SYMBO | LIC | MACHI | NE | INSTRUC | TIC | ONS | 5 1 | 11 | STI | D | BY | F | UN | ICI | 'IC | )NA | LI | TY |   | • | • | ٠ | • | A-1 |

|----|-------|-----|-------|----|---------|-----|-----|-----|----|-----|---|----|---|----|-----|-----|-----|----|----|---|---|---|---|---|-----|

|    | A.1   | SYM | BOLIC | NO | TATION  | •   | •   | •   | •  | •   | • | •  | • | •  | •   | •   | •   | •  | •  | • | • | • | • | • | A-1 |

HR-02000-0D

l

viii

### A. <u>SYMBOLIC MACHINE INSTRUCTIONS LISTED BY FUNCTIONALITY</u> (continued)

| <b>.</b> - |                                             |     |   |   |   |        |

|------------|---------------------------------------------|-----|---|---|---|--------|

| A.2        | BRANCH INSTRUCTIONS                         |     |   |   |   |        |

|            | A.2.1 Conditional branches                  |     |   |   |   |        |

|            | A.2.2 Unconditional jumps                   |     |   |   |   |        |

|            | A.2.3 Exits                                 |     |   |   |   |        |

| A.3        | PASS INSTRUCTIONS                           |     |   |   |   |        |

| A.4        | SEMAPHORE INSTRUCTIONS                      |     |   |   |   |        |

| A.5        | REGISTER ENTRY INSTRUCTIONS                 |     |   |   |   |        |

|            | A.5.1 Entries into A registers              |     |   |   |   |        |

|            | A.5.2 Entries into S registers              |     |   |   |   |        |

|            | A.5.3 Entries into V registers              |     |   |   |   |        |

| A.6        | INTER-REGISTER TRANSFER INSTRUCTIONS        | • • | • | • | • | . A-7  |

|            | A.6.1 Transfers to A registers              | • • | • | • | • | . A-7  |

|            | A.6.2 Transfers to S registers              | • • | • | • | • | . A-8  |

|            | A.6.3 Transfers to V registers              |     | • | • | • | . A-8  |

|            | A.6.4 Transfer to Vector Mask register      |     |   |   |   |        |

|            | A.6.5 Transfer to Vector Length register .  |     |   |   |   |        |

| A.7        | MEMORY TRANSFER INSTRUCTIONS                |     |   |   |   |        |

|            | A.7.1 Stores                                |     |   |   |   |        |

|            | Local Memory writes                         |     |   |   |   |        |

|            | Common Memory writes                        |     |   |   |   |        |

|            | A.7.2 Loads                                 |     |   |   |   |        |

|            | Local Memory reads                          |     |   |   |   |        |

|            | Complete Memory references                  |     |   |   |   |        |

|            | Common Memory reads                         |     |   |   |   |        |

|            | Memory Range Error flags                    |     |   |   |   |        |

| A.8        | INTEGER ARITHMETIC OPERATION INSTRUCTIONS . |     |   |   |   |        |

| A.O        |                                             |     |   |   |   |        |

|            | 5                                           |     |   |   |   |        |

|            | A.8.2 Integer differences                   |     |   |   |   |        |

|            | A.8.3 Integer products                      |     |   |   |   |        |

| A.9        | FLOATING-POINT ARITHMETIC INSTRUCTIONS      |     |   |   |   |        |

|            | A.9.1 Floating-point sums                   |     |   |   |   |        |

|            | A.9.2 Reciprocal iterations                 |     |   |   |   |        |

|            | A.9.3 Reciprocal approximations             |     |   |   |   |        |

|            | A.9.4 Floating-point differences            |     |   |   |   |        |

|            | A.9.5 Integer to floating-point conversions |     |   |   |   |        |

|            | A.9.6 Floating-point to integer conversions |     |   |   |   |        |

|            | A.9.7 Floating-point products               |     |   |   |   |        |

|            | A.9.8 Square root iterations                |     |   |   |   |        |

|            | A.9.9 Square root approximations            | ••• | • | ٠ | • |        |

|            | A.9.10 Floating-point errors                | • • | • | • | • | . A-18 |

| A.10       | LOGICAL OPERATION INSTRUCTIONS              |     | • | ٠ | • | . A-19 |

|            | A.10.1 Logical products                     |     | • | • | • | . A-19 |

|            | A.10.2 Logical sums                         |     | • | • | • | . A-19 |

|            | A.10.3 Vector streaming                     |     | • | • | • | . A-20 |

|            | A.10.4 Logical differences                  |     | • | • |   | . A-20 |

|            |                                             |     | • | • | • | . A-21 |

|            | A.10.6 Compressed iota                      |     | • |   | • | . A-21 |

| A.11       | BIT COUNT INSTRUCTIONS                      |     |   | • | • | . A-22 |

| A.12       |                                             |     |   | • | • | A-23   |

|            | A.12.1 Left shifts                          |     |   |   |   | A-23   |

|            | A.12.2 Right shifts                         |     | - | - |   |        |

|            |                                             | •   | - | - |   |        |

HR-02000-0D

ix

B. CRAY-2 SYSTEM CONFIGURATIONS . . . . .

FIGURES

| 1-1 | CRAY-2 Computer System Mainframe                      |   | • | • | • | 1-3  |

|-----|-------------------------------------------------------|---|---|---|---|------|

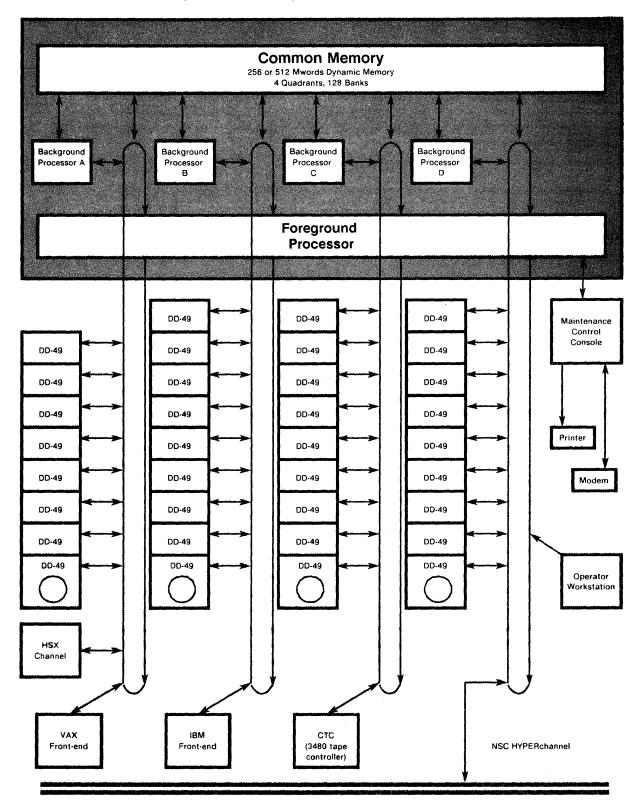

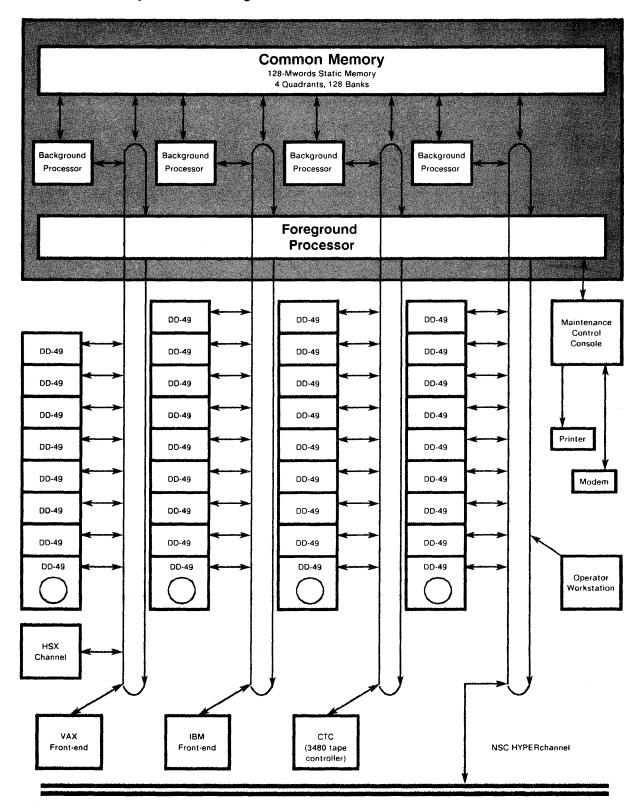

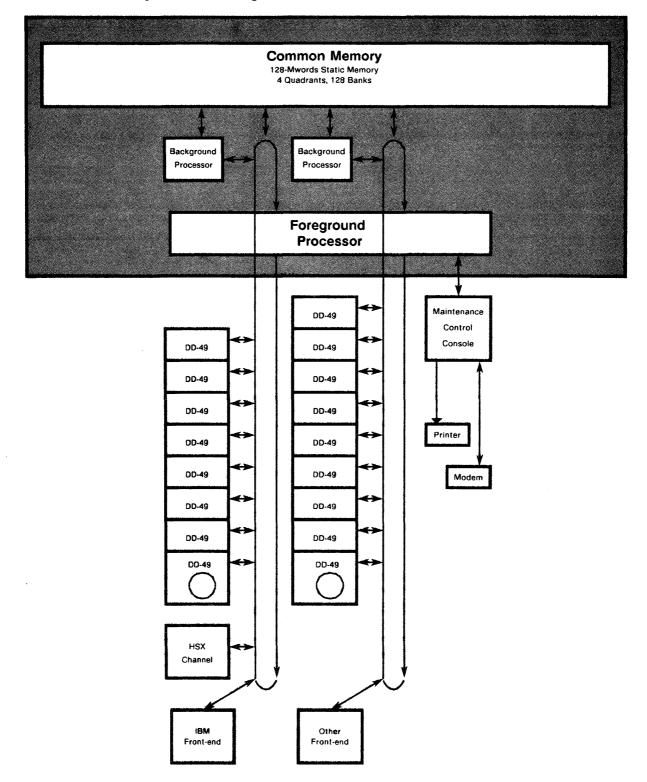

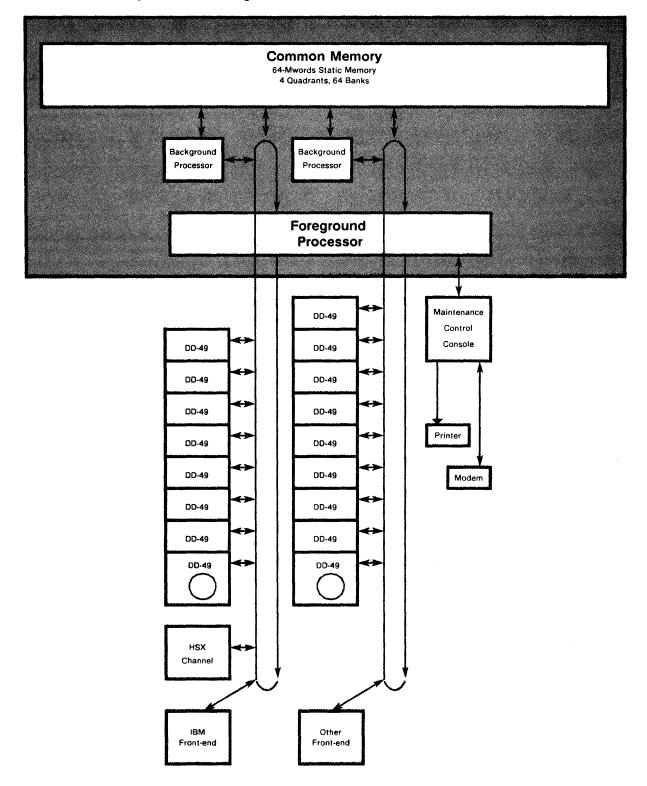

| 1-2 | CRAY-2 Four Background Processor Computer System      |   |   |   |   |      |

|     | Mainframe Configuration                               | • | • | • | • | 1-5  |

| 2-1 | Control and Data Paths in One Background Processor .  | • | • | • | • | 2-2  |

| 2-2 | Floating-point Data Format                            | • | • |   | • | 2-12 |

| 2-3 | 48-by-48 Bit Matrix Used for Floating-point Product . | • | • | • | • | 2-17 |

| 2-4 | 48-by-48 Bit Matrix Used for Reciprocal Iteration     | • | • | • | • | 2-20 |

| 2-5 | 48-by-48 Bit Matrix Used for Square Root Iteration .  | • | • | ÷ | • | 2-21 |

| 3-1 | Instruction Parcel Format                             | • | • |   | • | 3-2  |

| 4-1 | Memory Address for Common Memory                      | • | • | • | • | 4-1  |

| 4-2 | Error Correction Matrix                               | • | • | • | • | 4-4  |

| 5-1 | Channel Loop                                          | • | • | • | • | 5-2  |

| A-1 | CRAY-2 Computer System Symbolic Machine Instructions  |   |   | • | • | A-2  |

### TABLE

### SPECIFICATION SHEETS

| CRAY-2 MODEL NUMBER  | 4-256 or 4-512 SPECIFICATION SHEET | B-3  |

|----------------------|------------------------------------|------|

| CRAY-2S MODEL NUMBER | 4-128 SPECIFICATION SHEET          | B-7  |

| CRAY-2S MODEL NUMBER | 2-128 SPECIFICATION SHEET          | B-11 |

| CRAY-2S MODEL NUMBER | 2-64 SPECIFICATION SHEET           | B-15 |

B-1

. .

. . . . . . . . .

## **1. INTRODUCTION**

The CRAY-2 computer system is a powerful, general-purpose computer system with extremely high processing rates. Scalar and vector capabilities in a multiprocessing environment combined with integrated foreground processing achieve these high rates.

#### 1.1 CRAY-2 COMPUTER SYSTEM FEATURES

The CRAY-2 computer system mainframe contains either two or four independent Background Processors, each more powerful than a CRAY-1 computer system processor. Featuring a clock-cycle time faster than any other computer system available, each of these processors offers exceptional scalar and vector processing capabilities. The Background Processors can operate independently on separate jobs or concurrently on a single problem. The very high speed Local Memory integral to each Background Processor is available for temporary storage of vector and scalar data.

Common Memory is one of the most important features of the CRAY-2 computer system. It consists of 256 or 512 Mwords in dynamic memory, or 64 or 128 Mwords in static memory, 64-bits long, randomly accessible from any of the Background Processors and from any of the data channels. The memory is arranged in quadrants with either 64 or 128 interleaved banks. All memory access is performed automatically by the hardware. Any user may use all or part of the memory not being used by the operating system.

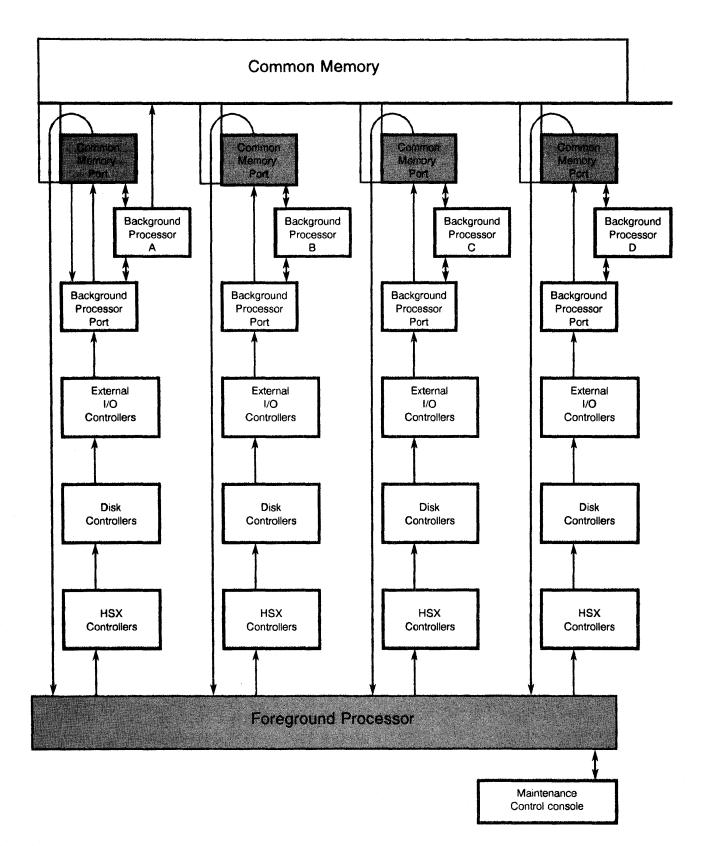

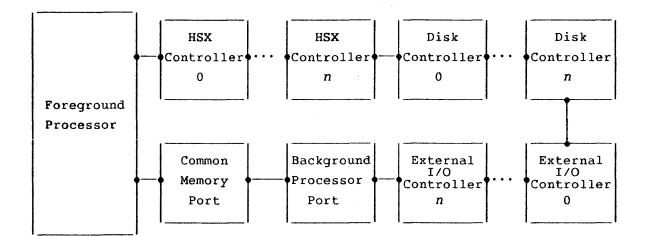

Control of network access equipment and the high-speed disk drives is integral to the CRAY-2 computer system mainframe hardware. A single Foreground Processor coordinates the data flow between the system's Common Memory and all the external devices across either two or four high-speed I/O channels. The synchronous operation of the Foreground Processor with the Background Processors and the external devices provides a significant increase in data throughput.

The most important CRAY-2 computer system features are:

- Extremely large directly addressable Common Memory

- Fastest cycle time available in a computer system

- Scalar, vector, and multiprocessing combined in one system

- Integral Foreground Processor

HR-02000-0D

- Elegant architecture

- Extremely high reliability

- High density memory chips and extremely fast silicon logic chips

- Liquid immersion cooling

#### 1.1.1 PHYSICAL CHARACTERISTICS

The CRAY-2 computer system mainframe is elegant in appearance as well as in architecture (see figure 1-1). The memory, computer logic, and DC power supplies are integrated into a compact mainframe composed of 14 vertical columns arranged in a 300° arc.

The upper part of each column contains a stack of logic modules and the lower part contains power supplies for the system. Total cabinet height, including the power supplies, is 45 in. (114.3 cm); the diameter of the mainframe is 53 in. (134.6 cm). Thus, the "footprint" of the mainframe is a mere 16 ft<sup>2</sup> (1.49 m<sup>2</sup>).

An inert fluorocarbon liquid circulates in the mainframe cabinet in direct contact with the integrated circuit packages. This liquid immersion cooling technology allows for the small size of the CRAY-2 computer system mainframe and is thus largely responsible for the high computation rates.

Significant CRAY-2 computer system physical characteristics are:

- Occupies only 16 ft<sup>2</sup> (1.49 m<sup>2</sup>) of floor space

- Stands 45 in. (114.3) high, diameter is 53 in. (134.6 cm)

- Contains 14 columns arranged in a 300° arc

- Contains 3-dimensional modules

- Contains liquid immersion cooling

- Contains cooling water heat exchange

Figure 1-1. CRAY-2 Computer System Mainframe

HR-2000 C

#### 1.1.2 ARCHITECTURE AND DESIGN

In addition to the cooling technology, the extremely high processing rates are achieved by a balanced integration of scalar and vector capabilities and a large Common Memory in a multiprocessing environment.

Significant architectural components of the CRAY-2 computer system include the following:

- Two or four independent Background Processors capable of vector and scalar operation. Synchronization of the Background Processors is achieved through the Foreground Processor and semaphore flags in the Background Processors.

- 256 or 512 Mwords of dynamic Common Memory, or 64 or 128 Mwords of static Common Memory

- A foreground system that controls and monitors system operation, including:

- A Foreground Processor for system supervision

- Two or four high-speed synchronous communication channels

- Up to 40 I/O devices

- Disk controllers to control up to 36 disk storage units (DSUs)

- Two or four Common Memory ports for data transfer

- Two or four Background Processor ports to allow Foreground Processor control

- External I/O controllers (from one to as many as four per channel)

- HSX controllers (two maximum per channel)

The identical Background Processors each contain registers and functional units to perform both vector and scalar operations. The single Foreground Processor supervises the Background Processors. The large Common Memory complements the processors and provides architectural balance, thus assuring extremely high throughput rates (see figure 1-2).

Shown in figure 1-2 is the four-processor model. The two-processor versions have two high-speed synchronous communication channels. The contents of a channel are the same in each version of the system.

On-site maintenance is possible through the maintenance control console.

Figure 1-2. CRAY-2 Four Background Processor Computer System Mainframe Configuration

HR-02000-0D

1-5

#### 1.2 CONVENTIONS

This manual uses the following conventions:

| <u>Convention</u>           | Description                                                  |

|-----------------------------|--------------------------------------------------------------|

| lowercase<br>italics        | Variable information                                         |

| X or x or X                 | An ignored value                                             |

| n                           | An unknown variable value                                    |

| (XX)                        | The contents of a register designated by the XX value        |

| Register bit<br>designators | Numbered right to left as powers of 2, starting with $2^0$ . |

Unless otherwise indicated, numbers in this manual are decimal numbers. Octal numbers are indicated with an 8 subscript. Exceptions are instruction parcels in instruction buffers and instruction forms which are given in octal without the subscript.

#### 1.2.1 EXAMPLES

Illustrations of the above conventions.

| Example                                      | Description                                                                                                                                                |

|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Transmit (Ak) to S <i>i</i>                  | Transmit the contents of the A register<br>specified by the <i>k</i> designator to the<br>S register specified by the <i>i</i><br>designator               |

| 167 <i>ixk</i>                               | Machine instruction 167 where the j<br>register designator is not used and is<br>an ignored value                                                          |

| Read <i>n</i> words from memory              | Read an unknown variable number of<br>words from memory. You can read,<br>within the stated restrictions, as few<br>or many words from memory as you wish. |

| Bit 2 <sup>63</sup> of an S or V<br>register | Value represents the most significant bit                                                                                                                  |

#### Example

#### Description

Bit 2<sup>31</sup> of an A register

Value represents the most significant bit

VM register element The VM register contains 64 bits, each corresponding to a word element in a Vector register. Bit 2<sup>63</sup> corresponds to element 0, bit 2<sup>0</sup> corresponds to element 63.

#### 1.3 ORGANIZATION

This manual is organized into the following sections:

| Section | Description                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | Contains the introduction to this manual                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2       | Describes the CRAY-2 computer system Background<br>Processor. The registers, functional units, and<br>algorithms used are described.                                                                                                                                                                                                                                                                                                                 |

| 3       | Provides detailed information on the CAL instructions<br>that operate on the CRAY-2 computer system. Each machine<br>instruction can be represented symbolically in Cray<br>Assembly Language (CAL) Version 2. The instructions are<br>listed octally in a box format that provides the Cray<br>Assembly Language (CAL) Version 2 syntax format, an<br>operand if required, a brief description of each<br>instruction, and the machine instruction. |

Following the boxed information is a detailed description of the instruction and an example using the instruction.

- 4 Describes the CRAY-2 Common Memory, phased memory access, and single-error correction/double-error detection (SECDED)

- 5 Describes the CRAY-2 Foreground System, which handles the I/O

- Appendix A Lists the symbolic machine instructions by function. The octal machine code can be used as an index when referring to section 3 for a detailed description of the instruction.

- Appendix B Contains the CRAY-2 system configuration specification sheets

HR-02000-0D

1-7

## 2. BACKGROUND PROCESSOR

The CRAY-2 computer system has either two or four identical Background Processors each containing operating and vector control registers, and functional units to perform both vector and scalar operations. The Foreground Processor supervises the Background Processors.

A Background Processor performs arithmetic and logical calculations. These operations, and the other functions of a Background Processor are coordinated through the control section.

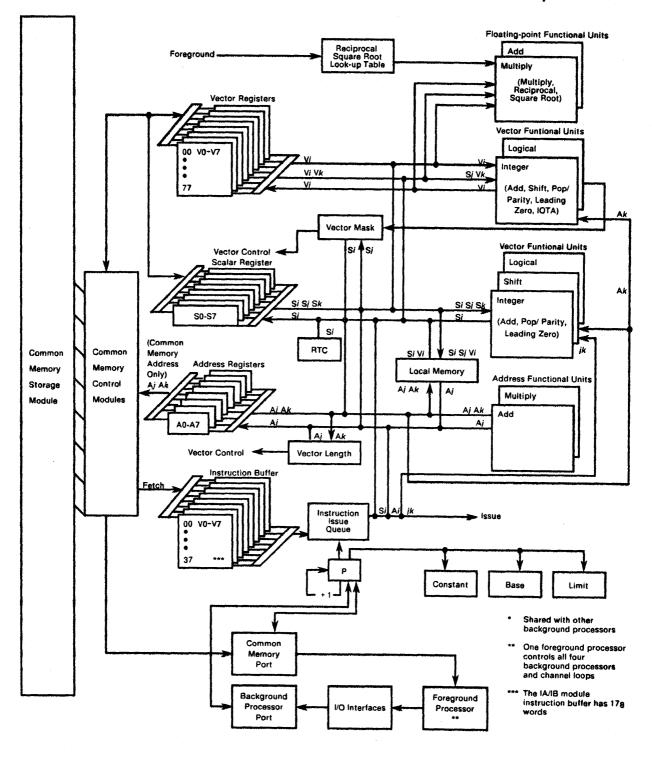

Figure 2-1 shows the control and datapaths for one Background Processor.

#### 2.1 CONTROL SECTION

Each Background Processor contains an identical, independent control section of registers and instruction buffers for instruction issue and control. This section describes the following control mechanisms:

- Instruction issue and control

- Real-time clock

- Semaphore flags

- Common Memory field protection

#### 2.1.1 INSTRUCTION ISSUE AND CONTROL

Each Background Processor contains a Program Address register, an instruction buffer with eight fields, and an instruction issue control mechanism to implement instruction issue and control.

#### Program Address register

Each Background Processor has a 32-bit Program Address (P) register indicating the address of the program instruction parcel currently in the issue position during normal operation. The Foreground Processor loads the P register with data at the beginning of a computation period. As each parcel issues from the instruction queue, the contents of the P register advance by 1.

The P register contents are reset to the branch destination address when a jump instruction is executed.

HR-02000-0D

1

## CRAY-2 BLOCK DIAGRAM (1 OF 4 BACKGROUND PROCESSORS)

Figure 2-1. Control and Data Paths in One Background Processor.

HR-02000-0D

#### Instruction buffers

Each Background Processor has a buffer with eight independent fields to allow program loops to execute without additional Common Memory references. Programs can loop within the instruction buffer using any of the branch instructions.

Each independent field contains 16 or 32 words. The total instruction buffer size is 128 or 256 words.

The next sequential instruction out of the instruction buffer or a branch out of the instruction buffer discards the oldest data field and replaces it with 16 or 32 words of new data.

#### Instruction issue

Background instructions are translated in several steps and are allowed to issue sequentially by an instruction issue control mechanism. The words are disassembled into 16-bit parcels that are placed in a queue where the translation occurs. The instruction issue process involves checking the reservation flags for the registers and functional unit involved in the instruction sequence. The parcel waits in issue position in the instruction queue until all required resources are free.

Instruction parcels and 16-bit constants are intermixed in the instruction queue. The constant parcels are passed through the instruction queue without test.

#### 2.1.2 REAL-TIME CLOCK

Each Background Processor has a 64-bit register that counts continuously at the clock period rate. This count value determines the passage of real time to an accuracy of 1 clock period (CP). The real-time clocks in the Background Processors are synchronized at deadstart. Instruction 115 reads the real-time clock.

#### 2.1.3 SEMAPHORE FLAGS

To synchronize Common Memory references, eight semaphore flags in the background system interlock Common Memory references when multiple Background Processors are executing a single job. One semaphore flag is assigned to each currently active job in the background system. A Background Processor also assigned to a job is assigned a semaphore flag at the same time.

b

The Background Processor uses four instructions in synchronizing its Common Memory references: 004, 005, 006, and 007. A 004 or 005 instruction requests the semaphore flag when the Background Processor program is accessing a Common Memory area that can interfere with other processors assigned to the job. The branch instruction results determine when the processor has exclusive access to this Common Memory area. The program must clear the semaphore flag to release the Common Memory area to another processor assigned to the same job.

#### 2.1.4 COMMON MEMORY FIELD PROTECTION

At execution time each object program has a designated field of Common Memory holding instructions and data. The foreground functions specify the field limits when the object program is loaded and initiated. Field limits are contained in the Base Address (BA) register and the Limit Address (LA) register.

All memory addresses contained in the object program code are relative to the base address beginning the defined field. An object program cannot read or alter any Common Memory location with an absolute address lower than the base address. Each object program reference to Common Memory is checked against the limit and base addresses to determine if the address is within the assigned bounds.

#### Base Address register

Each Background Processor has a 32-bit BA register. The BA register defines the lower boundary of the Common Memory address field. The Foreground Processor enters data into this register while the Background Processor is in idle mode. The data remains in the register for the duration of the Background Processor computation period.

Each Common Memory reference from the Background Processor includes the addition of the BA register contents to the other parts of the memory reference base address. All Background Processor references to Common Memory are relative to the base address boundary.

#### Limit Address register

Each Background Processor has a 32-bit LA register. The LA register defines the upper boundary of the Common Memory address field. The Foreground Processor enters data into this register while the Background Processor is in idle mode. The data remains in this register for the duration of the Background Processor computation period.

### Memory range error

When a memory reference exceeds the range limits, a memory range error occurs. Each Common Memory reference from the Background Processor includes a test of the resulting absolute Common Memory address against the contents of the BA and LA registers. An error signal is sent to the status register if the resulting absolute Common Memory address is less than the base address or equal to, or greater than, the limit address. A read reference results in zero data for this case. A write reference is aborted.

#### 2.2 OPERATING REGISTERS

Each Background Processor contains the following independent set of operating registers:

- Address

- Scalar

- Vector

Operating registers, a primary programmable resource of the Background Processor, enhance the speed of the system by satisfying heavy demands for data made by functional units. Different functional units can be used concurrently.

#### 2.2.1 ADDRESS REGISTERS

Eight 32-bit Address (A) registers are used primarily to hold memory address for Local Memory and Common Memory references. A registers are used for 32-bit integer calculations and to move data directly from Local Memory. Data is also transferred between Address and Scalar registers.

#### Shared registers

Eight 32-bit Shared registers prove a way to transfer data between Address registers in different CPUs. The Shared registers can be accessed by any of the four background processors, and are written into and read out of the Address registers. Data paths between the Shared registers and the background processors issuing the request are eight bits wide. The data transfer is organized into a 4-packet/4-clock period design scheme. The Shared registers are only available with S/N 2025.

#### 2.2.2 SCALAR REGISTERS

Eight 64-bit Scalar (S) registers serve as source and destination for operands executing scalar arithmetic and logical instructions. S registers can furnish one operand in vector instructions.

The eight 64-bit S registers in a Background Processor support Vector (V) registers in operations when one element of the computation is a constant value. The S registers function as computational way stations between Common Memory and the functional units where vector implementation of the work is not possible.

#### 2.2.3 VECTOR REGISTERS

The major computational registers of the Background Processor are eight Vector (V) registers, each having 64 elements. Each V register element has 64 bits. When associated data is grouped into successive elements of a V register, the register quantity is treated as a vector. Examples of vector quantities are rows or columns of a matrix, and elements of a table.

Computational efficiency is achieved by identically processing each element of a vector. Vector instructions provide for the iterative processing of successive V register elements. A vector operation begins by obtaining operands from the first element of one or more V registers and delivering the result to the first element of a V register. Successive elements are provided during each CP, and as each operation is performed, the result is delivered to successive elements of the result V register. Vector operation continues until the number of operations performed by the instruction equals a count specified by the contents of the Vector Length register (described in subsection 2.3).

Since many vectors exceed 64 elements, longer vectors are processed as one or more 64-element segments and a possible remainder of less than 64 elements.

The instruction issue control mechanism reserves the V registers that are involved in a functional unit operation. One, two, or three V registers can be involved, depending on the specific instruction. The functional unit is reserved at the same time as the V registers. The instruction sequence can then proceed to the next instruction and initiate concurrent activity as long as the resources reserved are not required.

The i, j, and k designators in a vector instruction can have the same value; it is advised, however, that the i designator always has a unique value. In the case of identical source operands, the data is streamed from the same V register to both data paths. In the case of a destination register that is the same as a source register, the V

#### 2.3 VECTOR CONTROL REGISTERS

The Vector Length (VL) register and the Vector Mask (VM) register provide control information needed in the performance of vector operations.

#### 2.3.1 VECTOR LENGTH REGISTER

The Vector Length (VL) register is a 6-bit special purpose register explicitly referenced in the Background Processor instructions. The VL register holds the vector length during a portion of the background computation. All vector operations capture the vector length at the time of instruction issue from the VL register.

Vector registers always begin a read or write operation at the zero element position in the V register. Elements are read or written sequentially for the length of the current vector data. A short vector after a long vector leaves the old vector data in those positions not replaced with new data.

Values allowed in the VL register are 0 through 63. A zero value is interpreted as 64. Background instructions 025 and 036 communicate explicitly with the VL register.

#### 2.3.2 VECTOR MASK REGISTER

The Vector Mask (VM) register is a 64-bit special purpose register explicitly referenced by the Background Processor instructions. The VM register merges vector data according to a set of precomputed Element flags. In effect, it provides a vehicle for implementing vector branch operations.

One bit of the VM register is associated with each element in the 64-element vector registers. The high-order bit  $(2^{63})$  of the vector mask corresponds to element 0 of the vector data. The bits of the mask then proceed in order to represent the following vector elements.

The vector mask data can be formed by a vector operation in which each element is evaluated for a specific criterion. Instructions 030 through 033 perform these tests. The VM register is cleared at the beginning of these instruction sequences and then bits are entered one at a time as the vector stream passes the test station.

The vector mask data can be used to merge two vector streams into a single result stream. Instructions 146 and 147 are used for this purpose. Elements of the j operand are selected when the mask contains 1 bits. Elements of the k operand are selected when the mask contains 0 bits.

HR-02000-0D

Instructions 034 and 114 move data between the VM register and an S register.

#### 2.4 FUNCTIONAL UNITS

Each Background Processor has a set of functional units to implement algorithms for the instruction set. A number of functional units can operate simultaneously. Each functional unit produces one result per CP. No information is retained in a functional unit for reference by subsequent instructions.

A functional unit receives operands from registers and delivers the result to a register when the function has been performed. Functional units operate essentially in three-address mode. Nonvector functional units can accept operands as fast as the instructions can issue.

A functional unit engaged in a vector operation remains busy for the duration and cannot participate in other operations. In this state, the functional unit is reserved. Other instructions requiring the same functional unit do not issue until the previous operation is completed. Only one functional unit of each type is available to the vector instruction hardware. When the vector operation completes, the reservation is dropped and the functional unit is then available for another operation.

Vector tailgating provides a means of using a vector operand register of one instruction as a destination register for a subsequent vector instruction before the first instruction has completed. Vector tailgating is only available on S/N 2025, 2027, and above.

Any two vector instructions, except for the vector instructions involving common memory or compress iota, can be tailgated. The tailgated instruction does not have to immediately follow the instruction to which it is tailgated.

Each Background Processor has the following set of functional units:

- Address Add

- Address Multiply

- Scalar Integer

- Scalar Shift

- Scalar Logical

- Vector Integer

- Vector Logical

- Vector Shift

- Floating-point Add

- Floating-point Multiply

In addition, a Background Processor contains a Local Memory which is a buffer for the A, S, and V register data.

#### 2.4.1 ADDRESS ADD FUNCTIONAL UNIT

The Address Add unit performs 32-bit integer addition and subtraction of two A register operands. (Instruction 020 performs integer sums and 021 performs integer differences.) This unit can accept address operands as fast as the instructions can issue.

#### 2.4.2 ADDRESS MULTIPLY FUNCTIONAL UNIT

The Address Multiply unit performs 32-bit integer multiplication of two A register operands. (Instructions 022 and 023 perform integer products.) This unit can accept address operands as fast as the instructions can issue.

#### 2.4.3 SCALAR INTEGER FUNCTIONAL UNIT

The Scalar Integer unit performs 64-bit integer addition and subtraction of S register operands. (Instruction 104 performs integer sums and instruction 105 performs integer differences.) It also performs population count (instruction 106ij0), population count parity (instruction 106ij1), and leading zero (instruction 107). This unit can accept scalar operands as fast as the instructions can issue.

#### 2.4.4 SCALAR SHIFT FUNCTIONAL UNIT

The Scalar Shift unit shifts the entire 64-bit contents of an S register (instruction 110 left or 111 right) or the double 128-bit contents of two concatenated S registers (instruction 112 left or 113 right). This unit can accept scalar operands as fast as the instructions can issue.

#### 2.4.5 SCALAR LOGICAL FUNCTIONAL UNIT

The Scalar Logical unit manipulates bit-by-bit the 64-bit quantities obtained from S registers. (Instruction 100 performs logical products, instruction 101 performs logical products complemented, instruction 102 performs logical differences, and instruction 103 performs logical sums.) This unit can accept scalar operands as fast as the instructions can issue.

HR-02000-0D

#### 2.4.6 VECTOR INTEGER FUNCTIONAL UNIT

The Vector Integer unit performs vector shifts (instruction 150 for left single, instruction 151 for right single, instruction 152 for left double, and instruction 153 for right double), vector integer arithmetic (instructions 160 and 161 for integer sums and instructions 162 and 163 for integer differences), vector population count (instruction 164*ij*0 for population count and instruction 164*ij*1 for population parity), vector leading zero count (instruction 165), and compressed iota (instruction 176). The unit can accept operand data each CP, and after a transit time delay, can deliver a result each CP.

For those CRAY-2 computer systems featuring vector tailgating (S/N 2025, 2-27, and above), the Vector Integer unit performs vector integer arithmetic, compressed iota, and operations involving the vector mask register.

#### 2.4.7 VECTOR LOGICAL FUNCTIONAL UNIT

The Vector Logical unit manipulates bit-by-bit the 64-bit quantities from two V registers or from V registers and S registers (instructions 140 and 141 perform logical products, instructions 142 and 143 perform logical differences, and instructions 144 and 145 perform logical sums). The unit can accept operand data each CP, and after a transit time delay, can deliver a result each CP.

#### 2.4.8 VECTOR SHIFT FUNCTIONAL UNIT

Those systems with vector tailgating contain the Vector Shift functional unit which performs vector shifts (instruction 150 for left single, instruction 151 for right single, instruction 152 for left double, and instruction 153 for right double), vector population count (instruction 164*ij*0 for population count and instruction 164*ij*1 for population parity), and vector leading-zero count (instruction 165).

#### 2.4.9 FLOATING-POINT ADD FUNCTIONAL UNIT

The Floating-Point Add unit performs addition or subtraction of 64-bit operands in floating-point format for both scalar and vector operations. It also performs the conversion between integer and floating-point. See subsection 2.5.2, Floating-point Arithmetic, for a description of the instructions that use this unit. The unit is reserved for the time of a vector stream during execution of vector addition instructions. The unit can accept vector operand data each CP, and after a transit time delay, can deliver a result each CP. The unit can accept scalar references as fast as they issue if the unit is not processing vector data.

#### 2.4.10 FLOATING-POINT MULTIPLY FUNCTIONAL UNIT

The Floating-Point Multiply unit performs full multiplication of 64-bit operands in floating-point format for both scalar and vector operations. It also performs reciprocal approximation, reciprocal square root approximation, reciprocal iteration, and reciprocal square root iteration. See subsection 2.5.2, Floating-point Arithmetic, for a description of the instructions that use this unit.

The unit is reserved for the time of a vector stream during execution of vector Floating-Point Multiply unit instructions. The unit can accept vector operand data each CP, and after a transit time delay, can deliver a result each CP. The unit can accept scalar multiply, reciprocal iteration, reciprocal square root iteration references as fast as they issue if the unit is not processing vector data. Scalar reciprocal approximation and reciprocal square root approximation references place a 4 CP reservation on the functional unit.

#### 2.4.11 LOCAL MEMORY

Each Background Processor contains 16,384 64-bit words of Local Memory. This memory holds scalar operands during a computation period. The Local Memory also can be used for temporary storage of vector elements when these elements are used more than once in a computation in the V registers. Instructions that use Local Memory are:

- 044 and 046 read from Local Memory to A register

- 045 and 047 write to Local Memory from A register

- 054 and 056 read from Local Memory to S register

- 055 and 057 write to Local Memory from S register

- 074 read from Local Memory to V register

- 075 write to Local Memory from V register

#### 2.5 ARITHMETIC OPERATIONS

Functional units in the Background Processor perform either twos complement integer arithmetic or floating-point arithmetic.

#### 2.5.1 INTEGER ARITHMETIC

All integer arithmetic, whether 32 bits or 64 bits, is twos complement. The Address Add and Address Multiply units perform 32-bit arithmetic. The Scalar Integer unit performs scalar 64-bit arithmetic and the Vector Integer unit performs vector 64-bit arithmetic.

Integer representations of the integers 0, +1, and -1 in 32-bit and 64-bit format are shown using octal notation.

| Integer | <u>32-bit Format</u> | <u>64-bit Format</u>                    |

|---------|----------------------|-----------------------------------------|

| 0       | 0000000000           | 000000000000000000000000000000000000000 |

| +1      | 0000000001           | 000000000000000000000000000000000000000 |

| -1      | 3777777777           | 177777777777777777777777777777777777777 |

Multiplication of two scalar integer operands is accomplished by using the floating-point multiply instruction. Division is done by using an algorithm; the particular algorithm used depends on the number of bits in the quotient.

#### 2.5.2 FLOATING-POINT ARITHMETIC

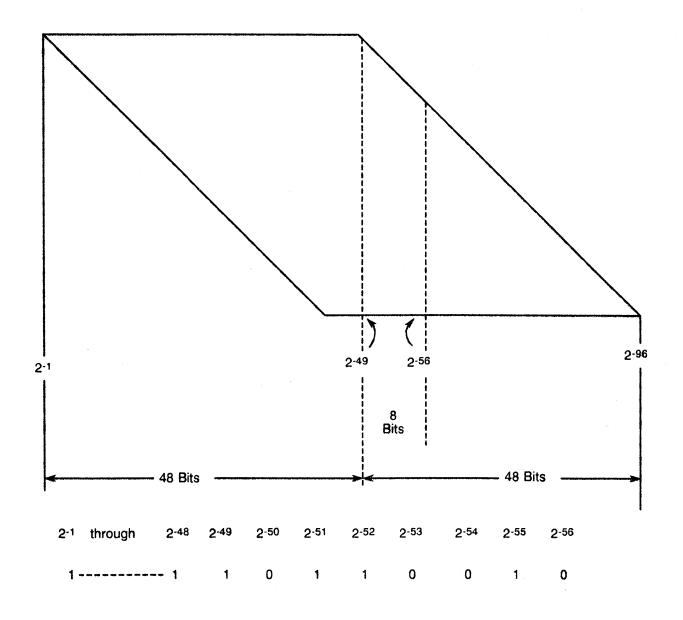

Floating-point numbers are represented in a standard format throughout the Background Processor. This format is a packed representation of a binary coefficient and an exponent. The coefficient is a 48-bit signed fraction. Figure 2-2 shows the sign of the coefficient is separated from the rest of the coefficient. Since the coefficient is signed magnitude, it is not complemented for negative values.

#### Binary point

| 2 <sup>63</sup> | 262  | 2 <sup>48</sup> | 247      | 2 <sup>0</sup> |

|-----------------|------|-----------------|----------|----------------|

| Sign            | Ежро | onent           | Coeffici | ent            |

Figure 2-2. Floating-point Data Format

The exponent portion of the floating-point format is represented as a biased integer in bits  $2^{62}$  through  $2^{48}$ . The bias that is added to the exponents is  $40000_8$ . The positive range of exponents is  $40000_8$  through  $57777_8$ . The negative range of exponents is  $37777_8$  through  $20000_8$ . Thus, the unbiased range of exponents is the following (the negative range is one larger):

2-200008 through 2+177778

In terms of decimal values, the floating-point format of the Background Processor allows the accurate expression of numbers to about 15 decimal digits in the approximate decimal range of  $10^{-2466}$  through  $10^{+2466}$ .

A floating-point representation of the integers 0, +1, and -1 in normalized form is shown using octal notation for each of the three fields.

#### Normalizing

A nonzero floating-point number is normalized if the most significant bit of the coefficient is nonzero. This condition implies the coefficient has been shifted as far left as possible and the exponent adjusted accordingly. Therefore, the floating-point number has no leading zeros in the coefficient. The exception is that a normalized floating-point zero is all zeros.

When a floating-point number is created by inserting an exponent of 400608 into a 48-bit integer word, the result should be normalized before being used in a floating-point operation. Normalization can be accomplished by adding the unnormalized floating-point operand to 0 (see subsection Integer to Floating-point Conversion, later in this section).

#### Range errors

Exponent values of  $60000_8$  and greater are considered to have overflowed the exponent range. Hardware tests are performed for these values to indicate floating-point range error. Exponent values less than  $20000_8$ are considered to have underflowed the floating-point range. Such values are treated as if they had a zero value. The hardware does not indicate when a computation underflows the floating-point range.

Whether or not range errors are enabled, when an overflow condition is detected by the hardware the result exponent is forced to an overflow value. Each floating-point operation forces a signature exponent as follows:

| Floating-point add/subtract              | 60000g             |

|------------------------------------------|--------------------|

| Floating-point multiply                  | 60001 <sub>8</sub> |

| Floating-point reciprocal approximation  | 600028             |

| Floating-point square root approximation | 60004 <sub>8</sub> |

#### Floating-point addition

The Floating-point Add unit forms the sum of two operands in floating-point format and delivers a result in floating-point format. The result is always normalized regardless of source operand status. Instructions 120, 170, and 171 use the Floating-point Add sequence.

In the process of adding two floating-point operands, one operand coefficient is shifted right for exponent matching. The coefficient from this shifting operation is rounded up.

A special test is made for all 0 bits in the result coefficient. When this occurs, the exponent field in the result is also cleared. A word of all zeros is delivered to the destination register.

A special test is made for one or both operands with an overflow exponent. An error signal is sent to the Background Port Status register (see section 5) if range errors are enabled, and an overflow exponent ( $60000_8$ ) is forced in the result delivered to the destination register.

#### Floating-point subtraction

The Floating-point Add unit forms the difference of two operands in floating-point format and delivers a result in floating-point format. Instructions 121, 172, and 173 use the floating-point subtraction sequence.

#### Floating-point to integer conversion

The Floating-point Add unit forms an integer representation of a floating-point operand. This process is accomplished by adding the operand to a constant integer. Instructions 122 and 174 use this form of the floating-point add sequence.

The maximum size of the resulting integer value is 48 bits. A positive or negative result is sign extended to form a 64-bit integer result.

An operand with a floating-point value greater than a 48-bit integer is an error condition. An error signal is sent to the Background Port Status register if floating-point range errors are enabled, and a zero result is delivered to the destination register.

#### Integer to floating-point conversion

The Floating-point Add unit forms a floating-point representation of an integer operand. This process is accomplished by adding the operand to a constant and using the floating-point normalize hardware to form the proper floating-point result. Instructions 123 and 175 use this form of the floating-point add sequence.

The maximum allowable size of the integer operand is 48 bits, if greater no error is flagged. The bits above 48 bits are discarded during the operation.

#### Floating-point product

The Floating-point Multiply unit forms the product of two operands in floating-point format and delivers a result in floating-point format. If both operands are normalized, the result is also normalized. Instructions 124, 154, and 155 use this sequence.

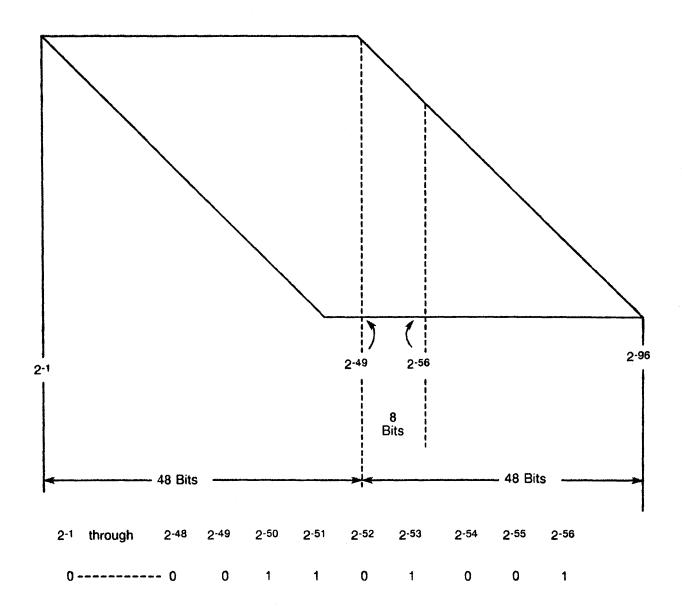

The 48 by 48 matrix of logical product bits is truncated 8 bit positions below the low-order result coefficient bit (see figure 2-3). Round bits are added to this lower field to give an equal population of high and low round errors for random operands. A round bias exists over narrow ranges of operands because of the 1-bit correction shift after the round operation.

The following special cases are treated in floating-point multiplication for operands out of range:

- 1. One or both operands have overflow exponent.

- 2. Sum of operand exponents is an overflow.

- 3. Sum of exponents is an underflow.

- 4. Both exponents are all zeros.

Cases 1 and 2 cause a Floating-point Error signal to be sent to the Background Port Status register if the floating-point range errors are enabled. The result delivered to the destination register is forced to an overflow exponent value  $(60001_8)$ . Case 3 results in an all-zero word sent to the destination register. Case 4 computes the coefficients with no normalize correction. The resulting exponent and sign bit for this case is 0, which aids multiple-precision and integer calculations.

#### Reciprocal approximation

The Floating-point Multiply unit forms an approximation to the reciprocal of a floating-point operand value. Instructions 132 and 166 use this sequence.

The values from a table are used in a linear interpolation computation. The following example shows the form of this computation.

#### Example:

In this example, A is a reciprocal approximation for the high-order 12 bits of operand coefficient, B is the operand coefficient, and R is the better reciprocal approximation.

Then the iteration step for interpolation is:

R = 2A - A\*A\*B

The two approximations read from a table are 2A and -A\*A. The normal multiply mechanism is then used to form the product with the additional term included in the summing process.

Two special cases occur in the reciprocal approximation sequence.

- Operand exponent has overflow value.

- Operand exponent has underflow value.

Both cases cause an error signal to be sent to the Background Port Status register if the floating-point range error is enabled and cause the computational result exponent to be forced to an overflow value (60002<sub>8</sub>).

Reciprocal iteration

#### \*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*

#### CAUTION

The reciprocal iteration instructions (126 and 156) should be used only with the reciprocal approximation instructions (132 and 166) and should only be used for one additional iteration. Operands not generated by the reciprocal approximation instructions may not deliver the expected result.

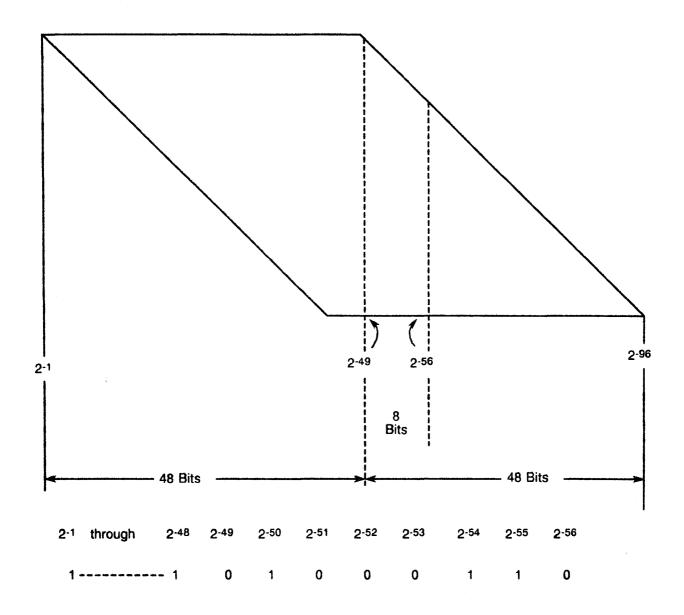

The Floating-point Multiply unit forms a floating-point number that is used in a second iteration for the reciprocal of a full-precision operand. The first iteration is formed in the reciprocal approximation previously described. The second iteration uses the same process to form a reciprocal approximation with 46 bits of coefficient accuracy. Instructions 126 and 156 use this sequence (see figure 2-4).

Figure 2-3. 48-by-48 Bit Matrix Used for Floating-point Product

The division algorithm that computes S1/S2 to full precision requires four operations.

| 1. | <b>S1</b> = a | Dividend                                                 |

|----|---------------|----------------------------------------------------------|

| •  | S2 = b        | Divisor                                                  |

| •  | S3 = /HS2     | 1/ b <sub>1</sub> - Half-precision<br>reciprocal         |

| 2. | S4 = S2 * IS3 | C = (2 - S2 <b>*</b> S3) -<br>Correction factor          |

| 3. | S5 = S3 * FS4 | b <sub>2</sub> = (1/ b <sub>1</sub> * c) -<br>reciprocal |

| 4. | S6 = S1 * FS5 | $x = (a * 1/b_2) - full precision reciprocal$            |

Reciprocal square root approximation

The Floating-point Multiply unit forms an approximation to the reciprocal square root of a floating-point operand value. Instructions 133 and 167 use this sequence.

The values from the table are used in a linear interpolation computation. The following example shows the form of this computation.

#### Example:

In this example, A is a reciprocal square root approximation for the operand coefficient, B is the operand coefficient, and R is the better reciprocal square root approximation.

The iteration step for interpolation is:

R = (3A/2) - (A\*A\*A\*B/2)

The two approximations read from the table are 3A/2 and -A\*A\*A/2. The normal multiply mechanism is then used to form the product with the additional term included in the summing process.

Three special cases occur in the reciprocal square root approximation sequence.

- 1. Operand exponent has overflow value.

- 2. Operand exponent has value of 0 through 3.

- 3. Operand is a negative value.

HR-02000-0D

2-18

Cases 1 and 3 cause an error signal to be sent to the Background Port Status register. All three cases cause the computational result exponent to be forced to an overflow value  $(60004_8)$ .

Reciprocal square root iteration

#### \*\*\*\*\*\*

### CAUTION

The square root iteration instructions (127 and 157) should be used only with the reciprocal square root approximation instructions (133 and 167) and should only be used for one additional iteration. Operands not generated by the reciprocal square root approximation instructions may not deliver the expected result.

#### \*\*\*\*\*\*\*\*\*\*\*\*\*\*\*

The Floating-point Multiply unit forms a floating-point number which is used in a second iteration for the reciprocal square root of an operand. The first iteration is formed in the reciprocal square root approximation previously described. The second iteration uses the same process to form a reciprocal square root with 46 bits of coefficient accuracy. Instructions 127 and 157 use this sequence (see figure 2-5).

The square root algorithm that computes the square root of S1 requires five operations.

| 1. | S1 = x        | Find square root of X                                                           |

|----|---------------|---------------------------------------------------------------------------------|

| •  | S2 = *QS1     | <pre>y = 1/ sqrt(x) - Half-precision reciprocal square root approximation</pre> |

| 2. | S3 = 1        |                                                                                 |

| •  | S4 = S1 ! S3  | Force X odd before doing the iteration                                          |

| 3. | S5 = S4 * FS2 | x * y                                                                           |

| 4. | S6 = S2 * QS5 | z = (3 - x * y * y)/2 - Square<br>root iteration correction factor              |

| 5. | S7 = S5 * FS6 | Sqrt $(x) = (x * y) * z - full precision square root$                           |

Figure 2-4. 48-by-48 Bit Matrix Used for Reciprocal Iteration

Figure 2-5. 48-by-48 Bit Matrix Used for Square Root Iteration

HR-02000-0D

2-21

# 3. BACKGROUND PROCESSOR SYMBOLIC MACHINE INSTRUCTIONS

This section contains detailed information about individual instructions or groups of related instructions. Each instruction begins with boxed information consisting of the Cray Assembly Language (CAL) Version 2 syntax format, an operand (if required), a brief description of each instruction, and the machine instruction (octal code sequence defined by the f field).

Following the boxed information is a more detailed description of the instruction and an example using the instruction.

### 3.1 SYMBOLIC INSTRUCTION FORMAT

The following special characters can appear in the operand field of symbolic machine instructions and are used by the assembler in determining the operation to be performed.

### Character Description

| +        | Integer sum of adjoining registers                |

|----------|---------------------------------------------------|

| +F,+f    | Floating-point sum of adjoining registers         |

| -        | Integer difference of adjoining registers         |

| -F,-f    | Floating-point difference of adjoining registers  |

| *        | Integer product of adjoining registers            |

| *F,*f    | Floating-point product of adjoining registers     |

| *I,*i    | Floating-point reciprocal iteration of adjoining  |

|          | registers                                         |

| *Q, *q   | Floating-point square root approximation          |

| *Q, *q   | Floating-point square root iteration of adjoining |

|          | registers                                         |

| /H,/h    | Floating-point reciprocal approximation           |

| #        | Use ones complement                               |

| >        | Shift value or form mask from left to right       |

| <        | Shift value or form mask from right to left       |

| &        | Logical product of adjoining registers            |

| !        | Logical sum of adjoining registers                |

| Λ        | Logical difference of adjoining registers         |

| CI,ci    | Compressed iota                                   |

| F,f      | Full load (64-bits)                               |

| FIX,fix  | Convert from floating-point to integer            |

| FLT, flt | Convert from integer to floating-point            |

| H,h      | Half load (32-bits)                               |

| L,1      | Left load (32-bits)                               |

| M, m     | Negative                                          |

HR-02000-0D

#### Character Description

| N,n                 | Nonzero               |

|---------------------|-----------------------|

| P,p                 | Parcel load (16 bits) |

| P,p                 | Population count      |

| P,p                 | Positive              |

| <b>P</b> , <b>Q</b> | Parity count          |

| S,s                 | Short load (6 bits)   |

| Z, z                | Leading-zero count    |

| Z, 2                | Zero                  |

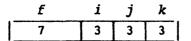

#### 3.2 MACHINE INSTRUCTION FORMAT

The Background Processors translate instructions in 16-bit parcels of data. These parcels are packed 4 per word in the Common Memory. The parcels are addressed as if the Common Memory had four times as many locations and the data were 16 bits long.

Figure 3-1 illustrates the format of a 16-bit instruction parcel.

Figure 3-1. Instruction Parcel Format

As shown in figure 3-1, the f designator is the operation code. The i, j, and k designators generally refer to V, S, or A registers in a three-address format. The i designator generally specifies the destination register for the functional computation. The j and k designators generally specify the source operands.

Uppercase or lowercase designators for the registers are allowed in CAL. Registers can be entered in mixed case letters and have the same meaning. Mnemonics can be entered in all uppercase or all lowercase and have the same meaning. Both cases are used in the symbolic instruction descriptions. The instructions are listed in lowercase and the written descriptions in uppercase for visual clarity.

Some instructions include additional parcels of constant data. An instruction can contain the following parcels of constant data depending on the specific instruction:

- 1  $(m_I)$

- 2  $(m_1 \text{ and } m_2)$

- 4  $(m_1, m_2, m_3, \text{ and } m_4)$

Single parcel constants generally address the Local Memory. Two parcel constants address Common Memory or enter a 32-bit value into an A or S register. Four parcel constants enter 64-bit values in the S registers.

When instructions read constants from the following parcels in the instruction stream, the program address is advanced over these data parcels to point to the next instruction. The high-order data parcel is read first for multiparcel data.

# 3.3 INSTRUCTION DESCRIPTIONS

The instruction descriptions begin with the octal code for the high-order 7 bits of the parcel (f designator). The three octal register designators (i, j, and k) then follow. An x appears in the description where a register's designator is ignored. CAL will insert a zero for every x.

ł

# INSTRUCTIONS 000 - 001

| Result | Operand | Description               | Machine<br>Instruction |

|--------|---------|---------------------------|------------------------|

| err    | exp     | Error exit                | 000x00                 |

| exit   |         | Normal exit               | 000x01                 |

| exit   |         | Normal exit               | 000x <i>jk</i>         |

| CMR    |         | Hold issue on memory busy | 001xxx                 |

Instructions 000 and 001 stop the current program sequence, place the Background Processor in idle mode, and set the Exit Mode and Idle Mode flags in the Background Port Status register. The 6-bit jk value is entered into the Background Port Status register.

| Code Generated | Location   |               | Operand | Comment |

|----------------|------------|---------------|---------|---------|

|                | <u> </u> ] | <u>10</u><br> | 20      | 35      |

| 000000         |            | lerr          | 1       |         |

| 000001         |            | exit          |         |         |

| 000004         | I          | exit          | 4       | T<br>A  |

|                | 1          |               | 1       |         |

| Result           | Operand        | Description                                                                 | Machine<br>Instruction |

|------------------|----------------|-----------------------------------------------------------------------------|------------------------|

| r,a <sub>i</sub> | ak             | Register jump to (a <sub>k</sub> ) with<br>return address to a <sub>i</sub> | 002 <i>ixk</i>         |

| j                | a <sub>k</sub> | Register jump to (a <sub>k</sub> ), value<br>in a <sub>k</sub> erased       | 002 <i>kxk</i>         |

Instruction 002 stops the current program sequence and begins a new sequence at a computed parcel address read from the  $A_k$  register. The parcel address for the next instruction in the current program sequence is entered into the  $A_i$  register.

| Code Generated | Location<br>1 | Result<br>10 | Operand<br>20 | Comment<br>35 |

|----------------|---------------|--------------|---------------|---------------|

| 002102         |               | r,al         | <br>  a2      |               |

| 002101         |               | j            | al            |               |

| Result | Operand | Description        | Machine<br>Instruction               |  |

|--------|---------|--------------------|--------------------------------------|--|

| j      | exp     | Unconditional jump | 003xxx m <sub>1</sub> m <sub>2</sub> |  |

Instruction 003 stops the current program sequence and begins a new sequence at a specified constant parcel address read from the next 2 parcels in the instruction queue.

For the expression:

- A word address is not allowed.

- An immobile relative attribute is not allowed.

- A parcel address is forced if the expression has a value attribute.

- If the expression is relocatable, it must be relative to either a mixed or code section targeted for Common Memory.

| Code Generated          | Location | Result<br>10 | Operand<br>20 | Comment<br>35 |  |

|-------------------------|----------|--------------|---------------|---------------|--|

| <br> 003000 0000000012a | -        | <br> j<br>   | <br> +43      |               |  |

### **INSTRUCTIONS 004 - 005**

| Result | Operand | Description                                                   | Machine<br>Instruction                     |

|--------|---------|---------------------------------------------------------------|--------------------------------------------|

| jcs    | exp     | Jump to constant parcel if<br>Semaphore clear; set Semaphore. | 004xxx m <sub>1</sub> m <sub>2</sub>       |

| jss    | exp     | Jump to constant parcel if<br>Semaphore set; set Semaphore.   | 005 <b>xxx m<sub>1</sub> m<sub>2</sub></b> |

Instructions 004 and 005 conditionally stop the current instruction sequence and begin a new sequence at a specified constant parcel address read from the next 2 parcels in the instruction queue.

The branch is conditional on the state of the Semaphore flag assigned to this Background Processor. The Background Port Status register points to the Semaphore flag. The Semaphore flag is set for either instruction if it was not previously set. The Semaphore flag bit in the Background Port Status register is set if either instruction alters the state of the flag from 0 to 1.

For the expression:

- A word address is not allowed.

- An immobile relative attribute is not allowed.

- A parcel address is forced if the expression has a value attribute.

- If the expression is relocatable, it must be relative to either a mixed or code section targeted for Common Memory.

| Examp. | le | S | : |

|--------|----|---|---|

|--------|----|---|---|

| Code Generated                                 | Location            | Result           | Operand            | Comment |

|------------------------------------------------|---------------------|------------------|--------------------|---------|

|                                                | _ <del> .</del><br> |                  |                    |         |

| 004000 0000000025a<br> <br> 005000 0000000025a |                     | jcs<br> <br> iss | 1+83<br> <br> 83+1 | 1       |

|                                                | 1                   | _ 55             |                    | f<br>1  |

| Result | Operand | Description   | Machine<br>Instruction |

|--------|---------|---------------|------------------------|

| SSM    |         | Set Semaphore | 006 <i>xxx</i>         |

Instruction 006 sets the Semaphore flag assigned to this Background Processor without regard to its previous state. The Semaphore flag bit in the Background Port Status register is set if the previous state of the Semaphore flag was a 0. The operating system program uses this instruction to restore Semaphore flag values at the time of job restart.

| Code Generated  | Location | Result | Operand   | Comment |

|-----------------|----------|--------|-----------|---------|

|                 | 1        | 10     | 20        | 35      |

| <br> 006000<br> |          | ssm    | <br> <br> |         |

| Result | Operand | Description     | Machine<br>Instruction |

|--------|---------|-----------------|------------------------|

| csm    |         | Clear Semaphore | 007***                 |

Instruction 007 clears the Semaphore flag assigned to this Background Processor without regard to its previous value. When this instruction executes, the semaphore bit in the Background Port Status register is cleared. A Background Processor program may use this instruction to release access to a privileged area of Common Memory for other processors assigned to this job.

This instruction issues without delay. Execution of the function may be delayed, however, by activity in the Common Memory port. The following instruction does not issue until the Common Memory quadrant buffers are clear. The delay ensures that any Common Memory write operations have been completed before another processor is allowed access to the privileged area.

| Code | Generated | Location<br>1 | Result<br>10 | Operand<br>20 | Comment<br>35 |

|------|-----------|---------------|--------------|---------------|---------------|

| 0070 | 00        |               | CSM          | 8             |               |

# INSTRUCTIONS 010 - 013

| Result | Operand             | Description                             | Machine<br>Instruction               |

|--------|---------------------|-----------------------------------------|--------------------------------------|

| jz     | a <sub>k</sub> ,exp | Branch if (a <sub>k</sub> ) is zero     | 010xxk m <sub>1</sub> m <sub>2</sub> |