This manual is not for further distribution without written approval from the nearest CRAY RESEARCH, INC. regional or country office.

# Cray Product Familiarization

Overview Presentation

**Software Training Department**

Cray Research, Inc. 2520 Pilot Knob Road Mendota Heights, MN 55120 (612) 452-9410

January, 1990

Copyright (c) 1986, 1990, by Cray Research, Inc. This workbook or parts thereof may not be reproduced in any form unless permitted by contract or by written permission of Cray Research, Inc.

Requests for copies of Cray Research publications and comments about these publicators should be directed to:

#### CRAY RESEARCH, INC.

2520 Northland Drive Mendota Heights MN 55120

| Revision   | Description                                                                                     |

|------------|-------------------------------------------------------------------------------------------------|

| <b>A</b> . | September, 1986 Original printing                                                               |

| В          | September, 1987 Reorganized and updated                                                         |

| C          | November, 1987 Reorganized and updated                                                          |

| D          | May, 1988 Updated to include Y-MP and X-MP EA                                                   |

| E          | December, 1988 Updated to include Cray Ada, Lisp, and new options                               |

| ħ          | April, 1989 Updated to include new Y-MP models, UNICOS 5.0 features, and new networking options |

| C          | January, 1990 Updated Cray System Performance Section                                           |

CRAY, CRAY-1, SSD, and UNICOS are registered trademarks and CFT, CFT7, CFT2, COS, CRAY Ada, CRAY-2, CRAY X-MP, CRAY X-MP EA, CRAY Y-MP, CSIM, Delivering the Power..., HSX, IOS, SEGLDR, and SUPERLINK are trademarks of Cray Research, Inc.

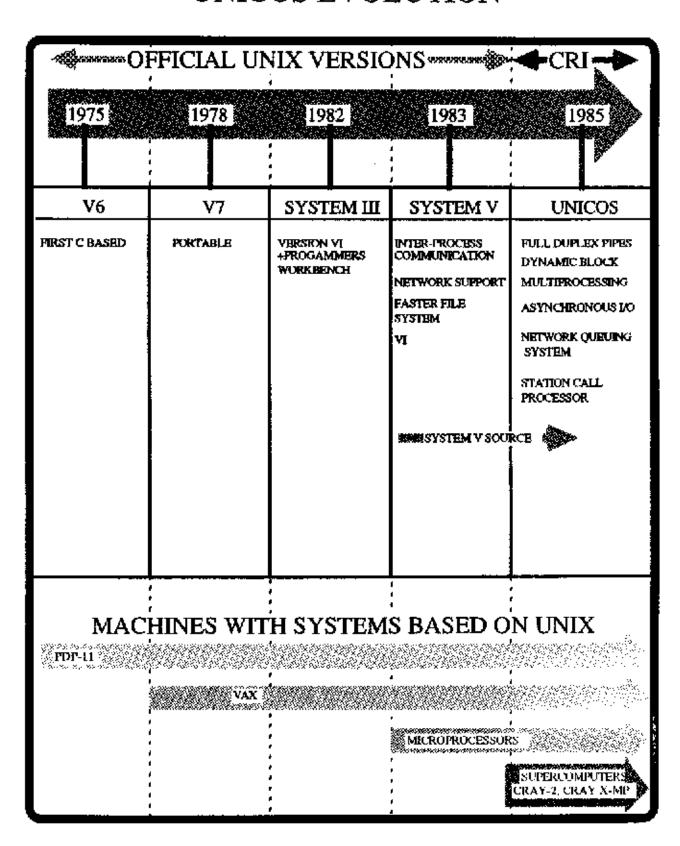

The UNICOS operating system is derived from the AT&T UNIX System V operating system. UNICOS is also based in part on the Fourth Berkeley Software Distribution under license from The Regents of the University of California.

ACP2 is a registered trademark of Computer Associates. Allegro CL is a registered trademark of Franz, Inc. Amdahl is a resiltered trademark of Apollo Computer Inc. DEC, DECnet, VAX, VMS, and VT are trademarks of Digital Equipment Corporation. CA-1 is a product of Computer Associates. CDC is a registered trademark of Control Data Corporation. Ethernet is a registered trademark of the Xerox Corporation. Fluorinert Liquid is a registered trademark of 3M. Freon is a trademark of Dupont. HYPERbus, HYPERchannel, NETBX and NSC are registered trademarks of Network Systems Corporation. Fujitsu is both a trademark of Fujitsu America. IBM is a registered trademark and MVS, RACF, and VM are products of International Business Machines Corporation. LANlord is a trademark of Computer Network Technology Corporation. Molorola is a registered trademark of Motorola, Inc. NETEX is a registered trademark of Network Systems Corporation. NFS is a trademark of Sun Microsystems, Inc. Pyramid is a trademark of Pyramid Technology Corporation. Sun Workstation is a registered trademark and Sun and Sun-3 are trademarks of Sun Microsystems, Inc. UNIX is a registered trademark of AT&T. X Window System is a trademark of the Massachuseus Institute of Technology.

#### **Table of Contents**

## Introduction Section 1 Section 2 Section 3 Section 4 Section 5 Section 6 Section 7 Section 8 Section 9 Section 10 Section 11 Section 12 Section 13

### Cray Product Familiarization

#### Description

This course is designed to give Cray employees and customers a general overview of all the Cray Research hardware and software products. Because of the different needs of the various types of students, this course is presented in the following different versions.

#### Product Familiarization for Cray Non-technical Employees

This version of the course is for the Cray employee who does not have a strong background in the technical aspects of computers, it is **strongly** recommended that an employee who has little knowledge of computers take the two-day computer fundamentals course before attending this course.

## Product Familiarization for New Cray Technical Employees and Cray Customers

This version of the course is intended for the newly hired Cray technical employee and Cray customers. For Cray employees, this course should be taken as soon as possible after the employee has been hired.

### Product Familiarization for Cray Sales Employees

This version of the course differs from the others in that the course is presented using product presentation materials that are used in actual sales presentations. The materials are organized differently in order to provide a showcase of available presentation materials.

### Product Familiarization for Technical People

This course is for the Cray employee or customer who has been in the computer industry for a while and needs an update on the newer Cray hardware and software products. This course can be tailored to the individual needs of a specific audience. Depending on the audience, the length of this class may vary from several hours to two days.

# Cray Product Familiarization Course Objectives

Upon successful completion of this course, the learner should be able to:

- Identify the major Cray Research hardware products and explain their main characteristics and applications

- Identify the major Cray Research software products and explain their main characteristics and applications

- 3. Explain how the unique architectural features of the Cray Research hardware contribute to its high performance

- Explain how the unique features of the software products take advantage of the hardware

- Identify some of the main applications for which Cray Products are used.

# Cray Product Familiarization Course Outline

- Introduction

- II. Cray Product Overview

- A. Product History

- B. Hardware Products

- C. Software Products

- D. Product Applications

- III. Cray Hardware Products

- A. General CRAY Architecture

- B. CRAY Y-MP Computer Systems

- C. CRAY X-MP EA Computer Systems

- D. CRAY-2 Computer Systems

- IV. Cray Software Products

- A. The COS Operating System

- B. The UNICOS Operating System

- C. Communications and Networking

- D. Cray Programming Languages

- V. Cray Performance and Applications

- A Cray Programming Languages

- B. Cray Applications

## SECTION 1

Cray Product Familiarization

## **Product Overview**

BESKERBERGERSERE BESKER CTBy Research, Inc. Software

300

## THIS PAGE IS INTENTIONALLY LEFT BLANK.

#### ABOUT THE COMPANY

Cray Research, Inc. was organized in 1972 by Seymour R. Cray, a leading designer of large-scale scientific computers, along with a small group of computer industry associates. The company and its subsidiaries are engaged in the design, development, and manufacture of large-scale, high-speed computing systems and the marketing and support of such systems. The company's computer systems are used primarily for simulation of physical phenomena.

Initially, the market for Cray computer systems seemed to lie strictly in weather, energy, and defense research. But, by 1978, because Cray computer systems are general purpose in design, it became clear that a commercial market existed that would extend the marketplace beyond the traditional Cray customer. Commercial applications of the machines have widened the market to include users in petroleum research, fluid dynamics, geophysics and seismic analysis, structural analysis, electrical engineering, aerospace design, computational chemistry, and other disciplines.

#### WHAT IS A SUPERCOMPUTER?

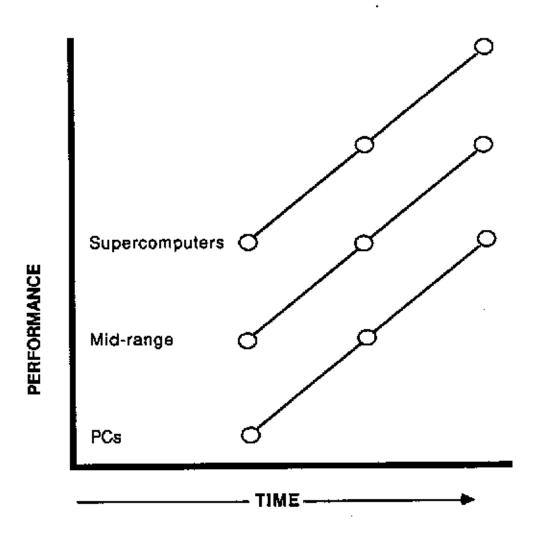

Supercomputers, by definition, are the fastest, most powerful computers commercially available at any time. Supercomputers are considered to be an order of magnitude (10 times) faster than the next most powerful class of computers.

#### WHY A CRAY?

Cray computer systems can solve complex mathematical and logical operations that involve large quantities of data and have the ability to carry out these operations at phenomenal speeds. The speed of each system is partially derived from its unique semi-circular design, which allows short wire lengths to carry the electrical signals. Patented cooling systems solve the heat generation problem that is produced by such advanced computation. In addition, new designs have made multiprocessing cost-effective for Cray users.

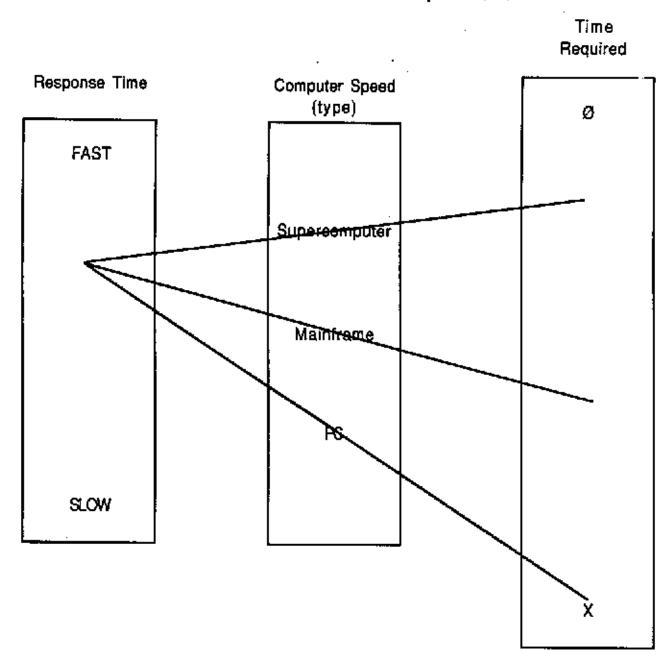

On a Cray computer system customers can:

- Solve problems that otherwise could not be solved.

- Solve problems which are difficult or impossible to physically measure

- Solve problems more cost effectively than many physical tests or tests done on slower computer systems

- Solve very complex problems within a specific response time

- · Achieve high quality results by allowing the investigation of more options

Because of the ever-expanding range of uses of Cray computers, the company has become known as the developer of "the world's fastest general-purpose computers".

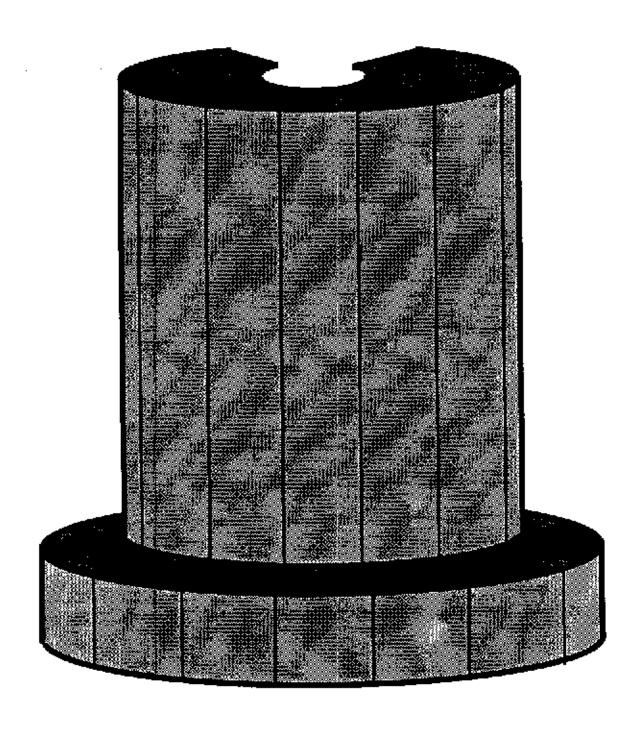

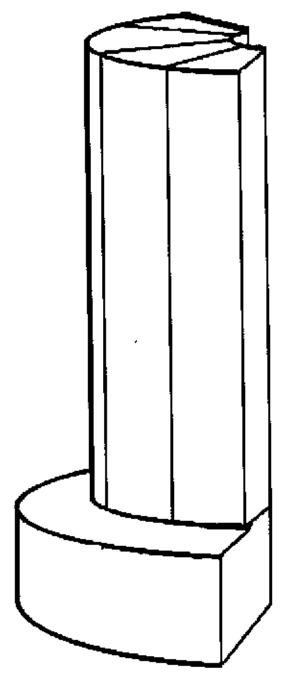

## **CRAY-1** Supercomputer

The CRAY-1 was Cray Research, Inc.'s first supercomputer. Development began in 1972 with Seymour Cray and a small group of developers. The first computer (serial number 1) was delivered to a customer in 1976. Cray-1 systems were a part of the product line until 1984 when the X-MP/1 replaced the CRAY-1M as the low-end model in the product line.

A CRAY-1 is identifiable by its squared seat corners, flat column panels, and aluminum protrusions on its top.

The following different models of the Cray-1 were produced:

CRAY-1A no IOS or SSD

CRAY-1B no IOS or SSD

CRAY-1S optional IOS, SSD available later

CRAY-1M IOS required, SSD available later

Within each specific model, a number of options existed for memory size, I/O channels, etc.

CRAY-1 SN1 went to Los Alamos National Labs in 1976 and included no software. Serial number two was destined for the National Center for Atmospheric Research (NCAR) but was cannibalized to create a new version of the machine (SN3) which included SECDED memory correction/detection hardware. All CRAY-1s but SN1 contain SECDED hardware which makes them about one foot taller than SN1. Serial number one has been at seven sites during its lifetime and will be retired to the planned supercomputer museum in Chippewa Falls. The last CRAY-1 manufactured was sent to Lockheed in 1983 making 57 the total number of CRAY-1s built.

# CRAY-1

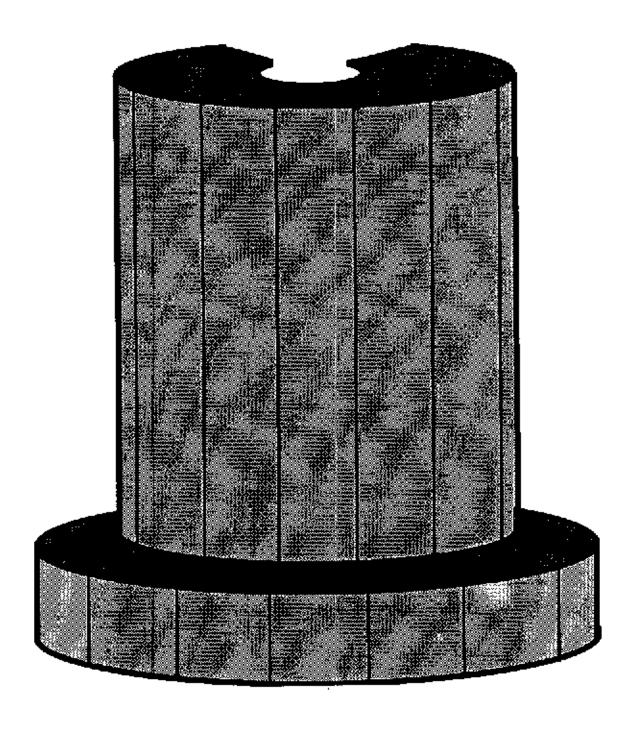

#### CRAY X-MP Supercomputer

The CRAY X-MP line of supercomputers was announced in 1982. The development work was done by Steve Chen and his team of developers. The X-MP system evolved from the CRAY-1 system, taking advantage of newer semiconductor technology and adding improved performance, enhanced architecture, multiple processors, and the SSD. The first system delivered in 1982 was a two-processor system that, at the time, was the upper model in a product line that consisted of both the X-MP and the CRAY-1.

Since then, many enhancements have been made to the X-MP to improve its performance, including adding more memory and more CPUs. All of the current X-MP models are designed with an "extended architecture" (EA) which makes them compatible with the Y-MP computer systems and allows the addition of more memory.

#### **CRAY X-MP Models**

The following different models of the X-MP were produced. Each model had a number of options for memory size. Details on options and improvements will be covered later. Only the X-MP EA se models are still produced.

CRAY X-MP/1 one-processor system

CRAY X-MP/2 two-processor system

CRAY X-MP/4 four-processor system

CRAY X-MP EA/1 one-processor system

CRAY X-MP EA/2 two-processor system

CRAY X-MP EA/4 four-processor system

#### X-MP Serial Numbering Scheme

| 100  | X-MP/2        | ECL memory                   |

|------|---------------|------------------------------|

| 200  | X-MP/4        | ECL memory                   |

| 300  | X-MP/1        | MOS memory (replaced CRAY-1) |

| 400  | X-MP/2        | MOS                          |

| 500  | X-MP/14se     | MOS                          |

| 1100 | X-MP EA/4     | MOS                          |

| 1200 | M-MP EA/1 & 2 | MOS                          |

| 1300 | X-MP EAse     | MOS ·                        |

# CRAY X-MP EA

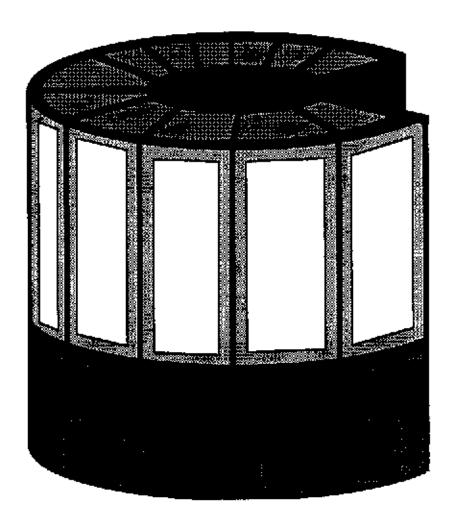

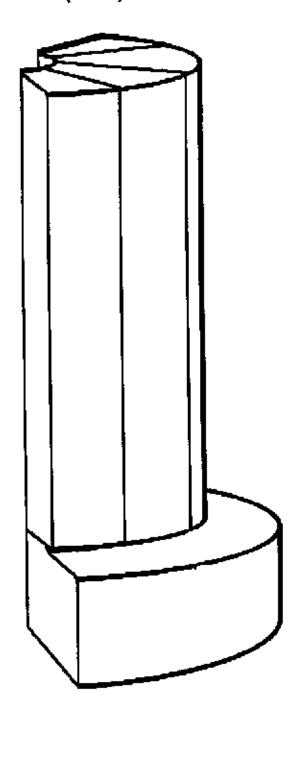

### **CRAY-2 Supercomputer**

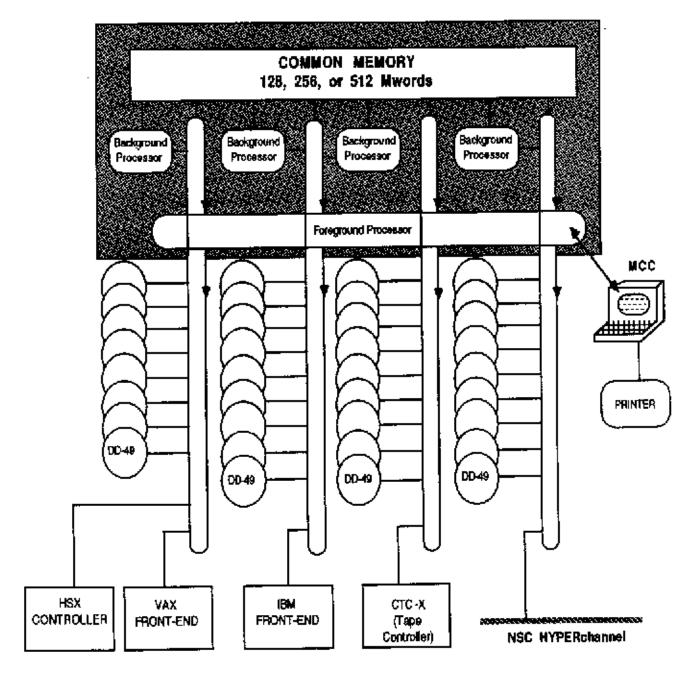

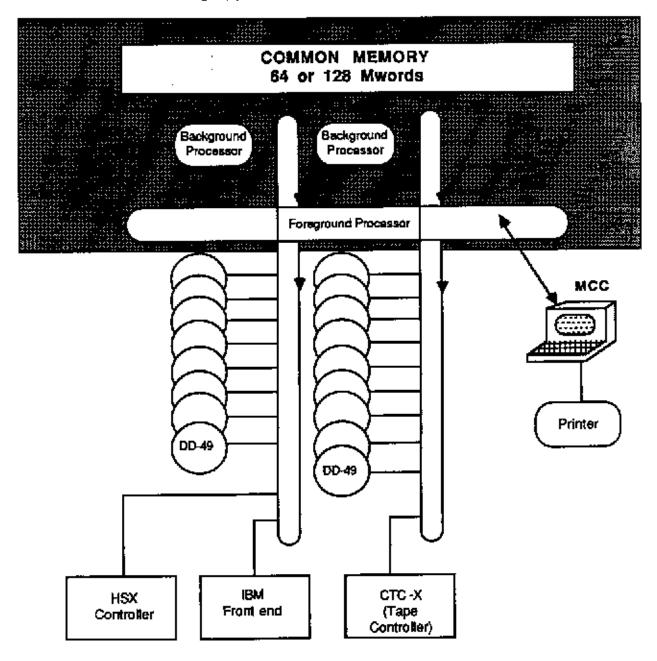

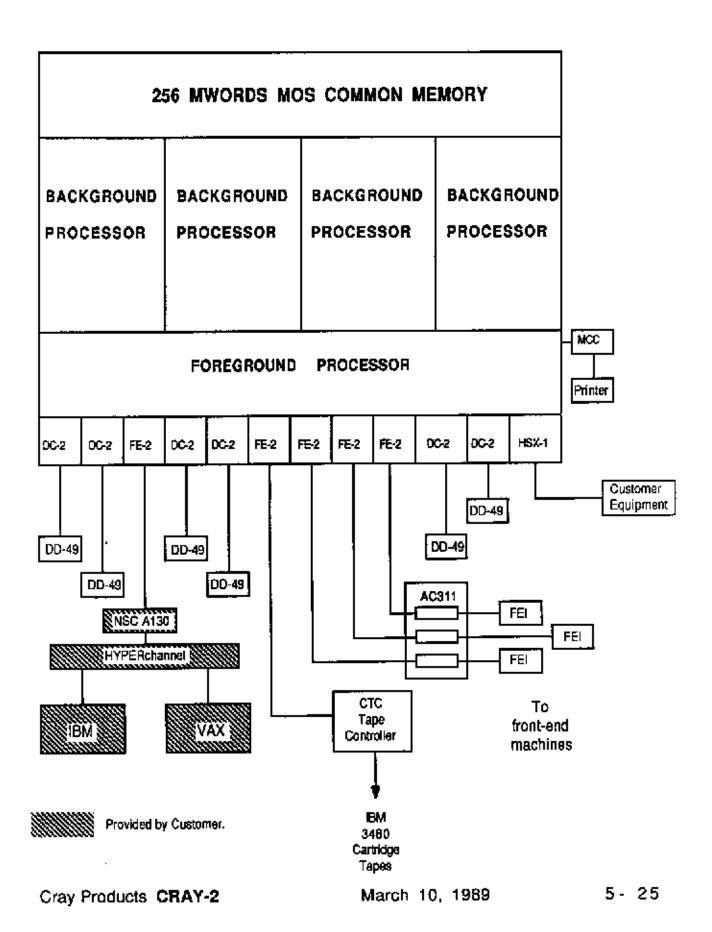

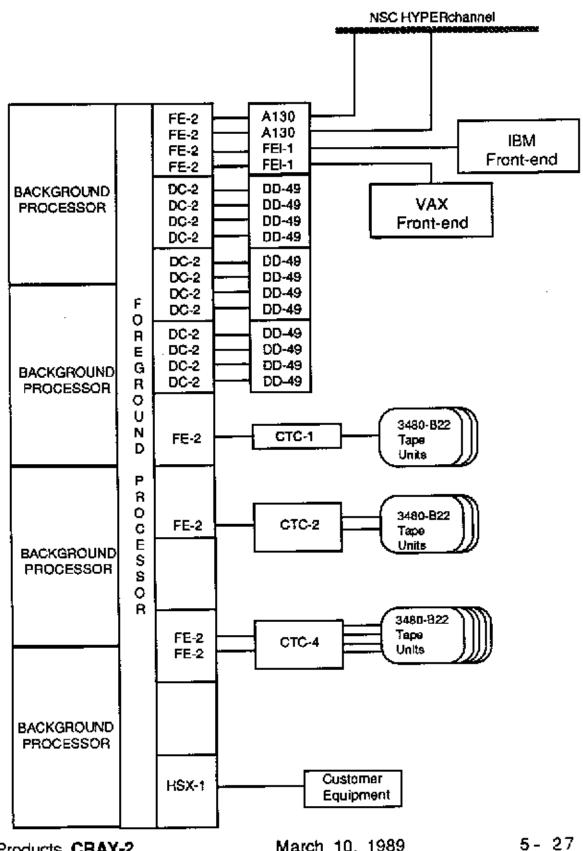

The CRAY-2 system was announced in the summer of 1985. Seymour Cray was responsible for the new design that offered high performance, a very large central memory, and liquid immersion cooling technology.

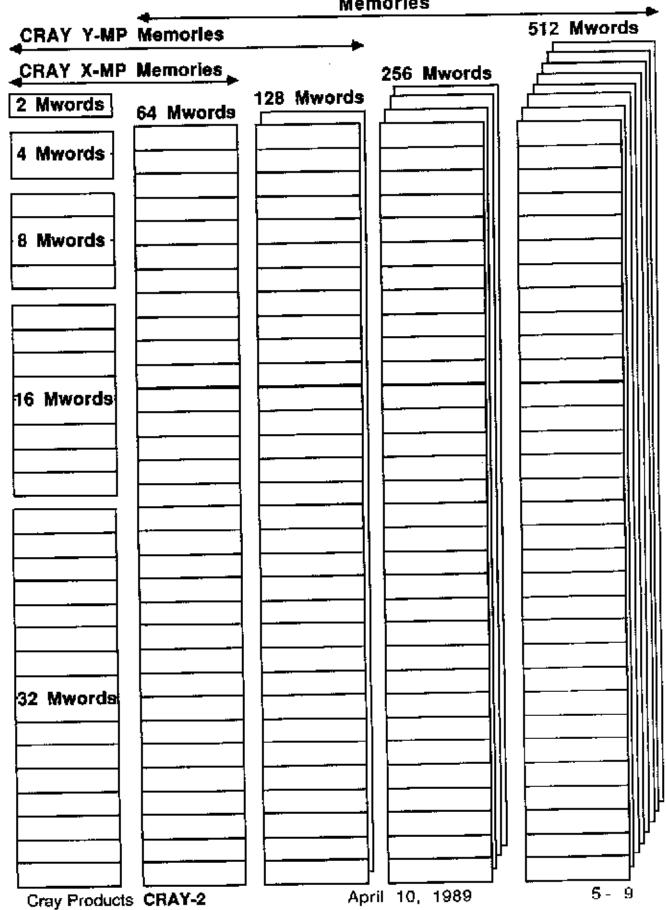

The CRAY-2 features a common memory of up to 512 million 64-bit words - allowing applications to accomplish in-memory solutions to problems that were previously considered impractical due to much smaller memory sizes.

Four background processors running with a clock period of 4.1 nanoseconds offer an effective throughput six to twelve times that of the original CRAY-1.

The CRAY-2 runs the UNICOS operating system which is based on the AT&T UNIX operating system.

# CRAY-2

### **CRAY Y-MP Supercomputer**

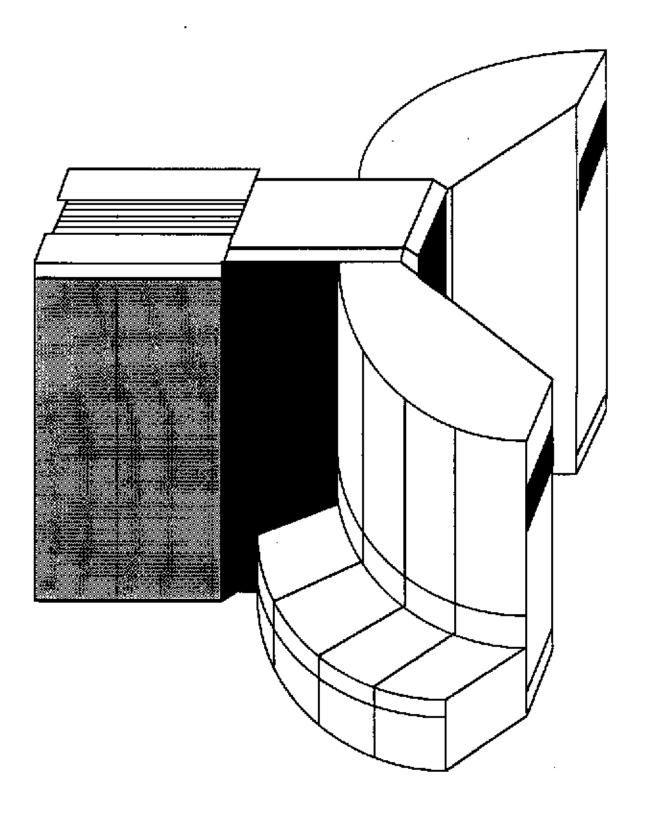

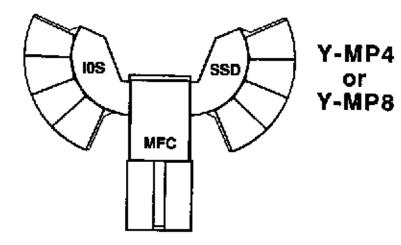

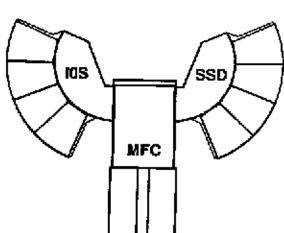

The CRAY Y-MP line of supercomputers was announced in February, 1988. The Y-MP system evolved from the CRAY X-MP system but it provides more processing power in a smaller space because it incorporates Very Large Scale Integration (VLSI). This essentially means putting more computing power on a chip. Two of the new chips used on the Y-MP contain the processing power of one whole module used in the CRAY-1/A. The first release of the Y-MP has eight CPUs and a clock speed of 6.0 nanoseconds, which is approximately 30% faster than the X-MP's 8.5 nanosecond clock. The Y-MP's design also includes a new cooling design. A new model of the IOS and an SSD both become part of the chassis, combining to form an approximate "Y" shape.

The first Y-MP (SN1001) has 32 million words of main memory and a 128-million word SSD. New models have been announced which will replace most of the X-MP line. Model options will be discussed later.

The intent with the design of the Y-MP was to increase processing power, speed, and memory while remaining compatible with the X-MP line of supercomputers.

# CRAY Y-MP

### Input/Output Subsystem (IOS)

The I/O Subsystem was introduced in 1979 as an option of the CRAY-1S system. The function of the I/O Subsystem is to reduce the I/O overhead on the mainframe and to provide enhanced I/O capabilities such as on-line tapes. The I/O subsystem is a required component of all CRAY-1M, CRAY X-MP, and CRAY Y-MP systems.

#### I/O Subsystem Models

The following I/O Subsystem models have been produced:

IOS Model A

IOS Model B

**IOS Model C**

KOS Model D

### Solid-State Storage Device (SSD)

The SSD was introduced in 1982 as an option for the X-MP and CRAY-1S systems. The function of the SSD is to provide an extremely fast secondary storage for the CRAY mainframe. The SSD is viewed by the user and the operating system exactly like a disk. This makes it very easy to take existing I/O-bound programs and speed them up by as much as 20-30 times by moving disk datasets to the SSD.

#### **SSD Models**

The SSD comes with a number of memory size options. They are:

32 MWords (can be built into IOS Model C or D)

128 MWords (standalone or can be built into IOS Model D)

256 MWords

512 Mwords

# Input-Output Subsystem (IOS)

Solid-state Storage Device (SSD)

Cray Products Overview

March 2, 1989

1-13

## Other Hardware Products

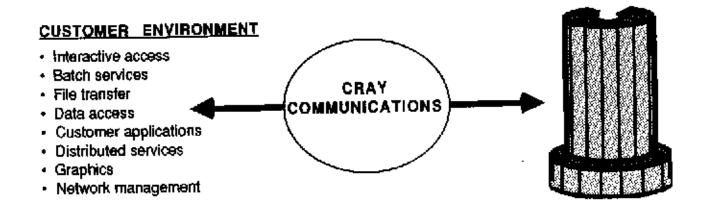

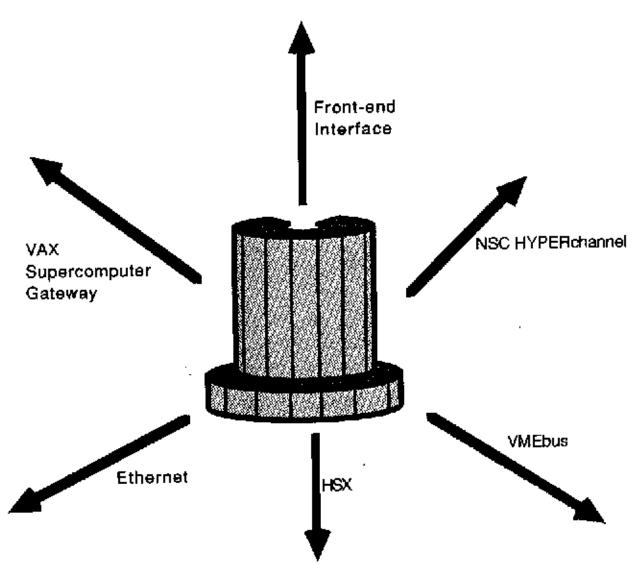

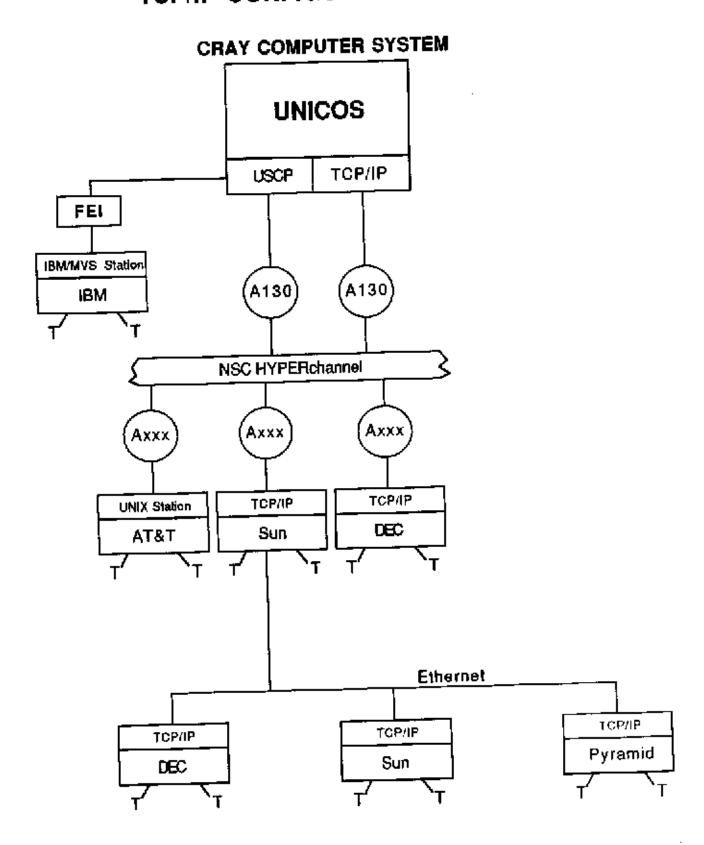

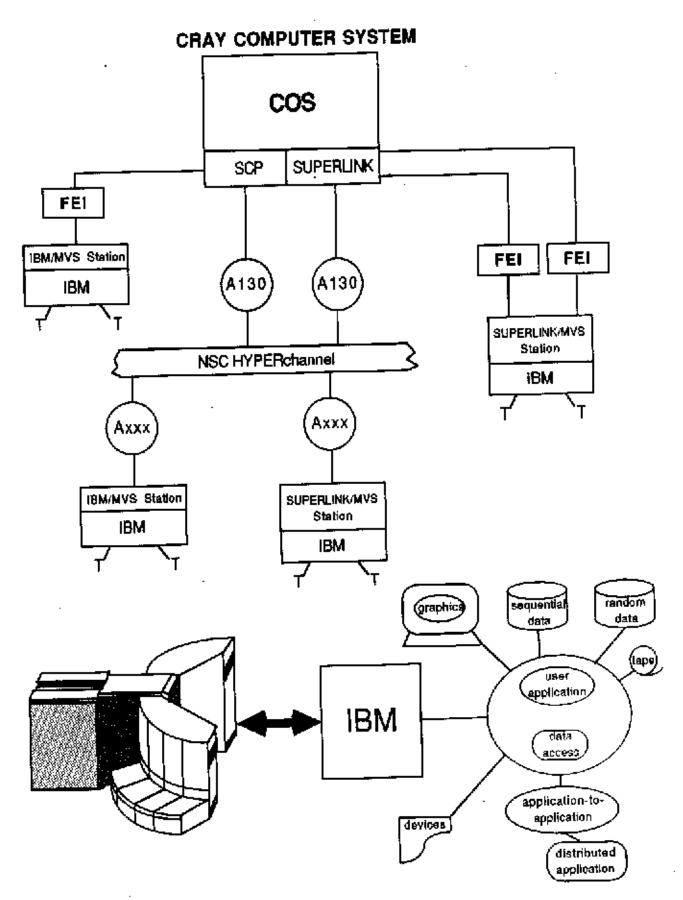

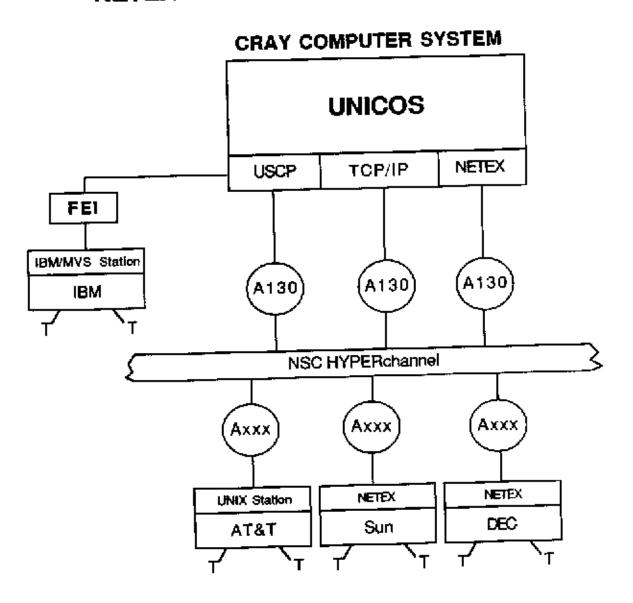

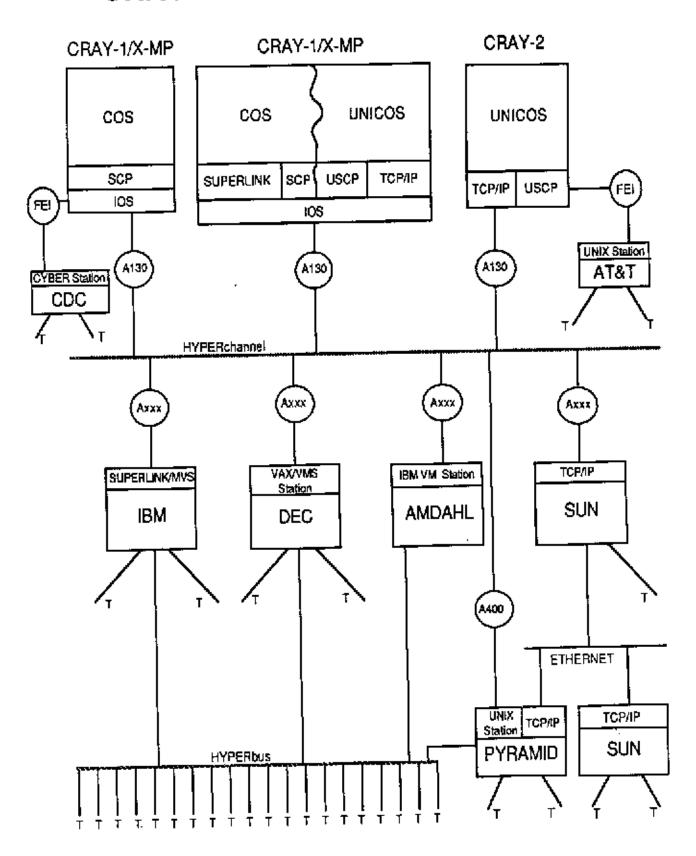

#### Front-End and Networking Interfaces

Cray manufactures interfaces for a number of different front-end computers and networks. A front-end interface allows a front-end computer to communicate with a Cray computer. Some of the front ends that are supported are IBM, CDC, Amdahi, and DEC. A network interface provides a means of making a Cray computer a node on a network of many front end computers so they may all communicate with each other.

#### Disk Storage Devices

Cray does not manufacture disk drives but does supply them with systems. The disk drives in the current product line include the DD-40 (with drives made by Control Data Corp.), the DD-49 (made by lbis), and the DD-39 (made by Fujitsu). Disk drives that are supported but no longer part of the current product line are the DD-19 and DD-29 drives (made by Control Data).

#### Tape Drives

Cray provides software and hardware channel support for IBM compatible tape drives as an option on some of the systems. It is normally the responsibility of the customer to obtain the tape drives.

#### Miscellaneous Peripherais

Every Cray system includes a number of peripheral devices that are used to maintain and operate the system. Depending on the system, these might include operator consoles, small tape and disk drives, and a small printer/plotter.

#### **Power and Cooling Equipment**

Because of the tremendous electrical and cooling requirements of a Cray system, some rather large power and cooling devices are supplied with each system. These include motor generators, cooling condensors, and power distribution units. The CRAY-2 with its unique liquid immersion cooling system has additional cooling devices (pods) and coolant reservoirs.

#### On-site Maintenance Equipment

Each site has the capability to repair systems. Resources include a large spare parts inventory and equipment such as module testers.

## **Cray Software Products**

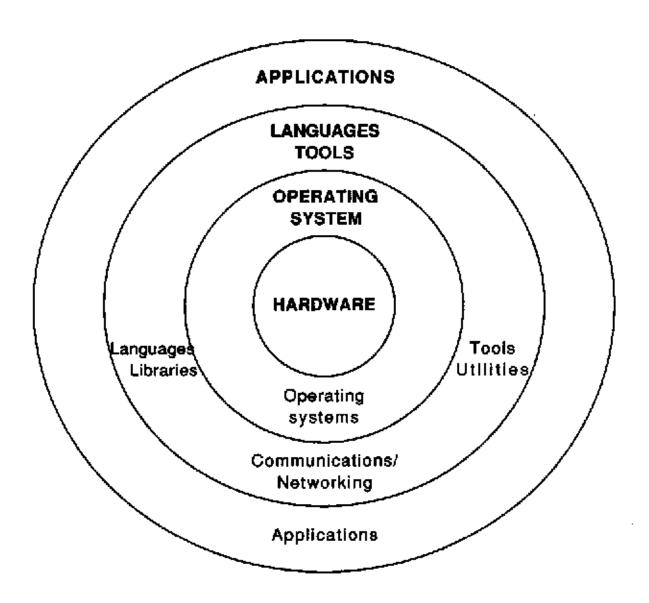

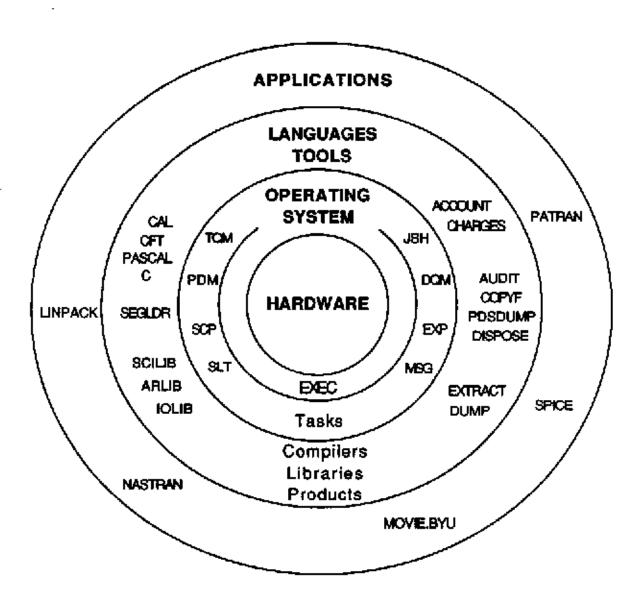

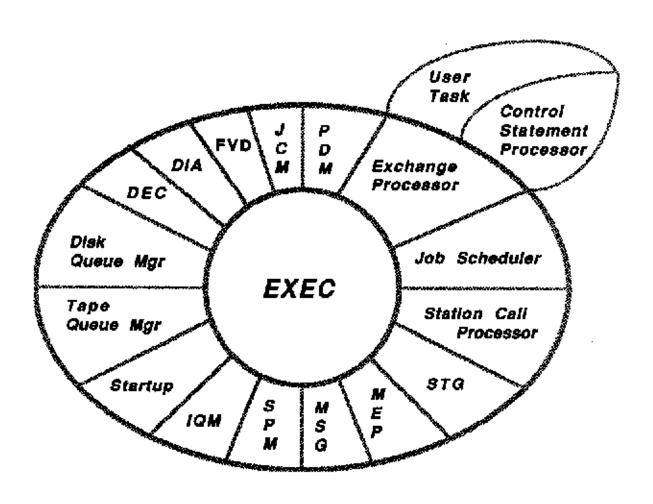

#### Operating Systems

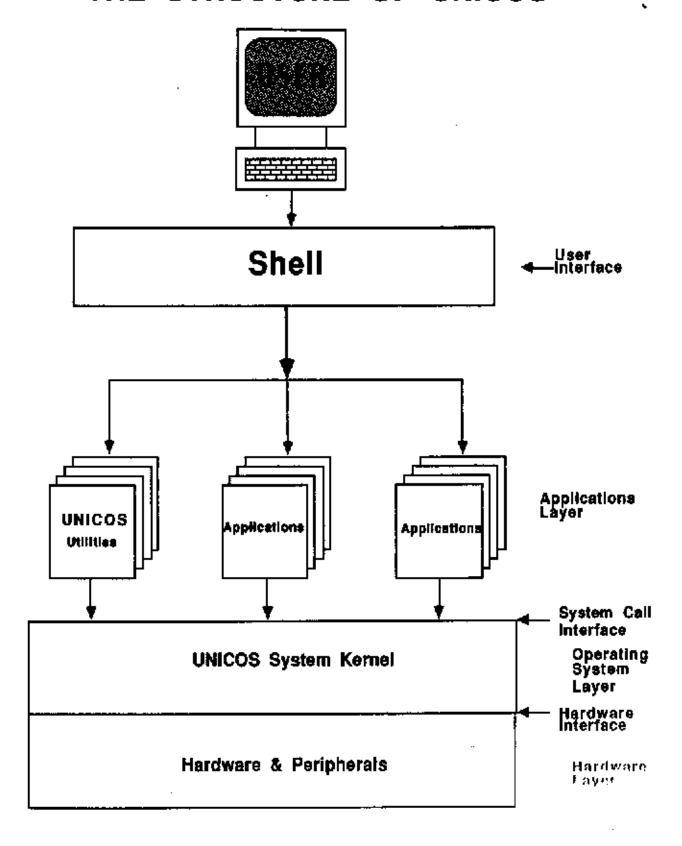

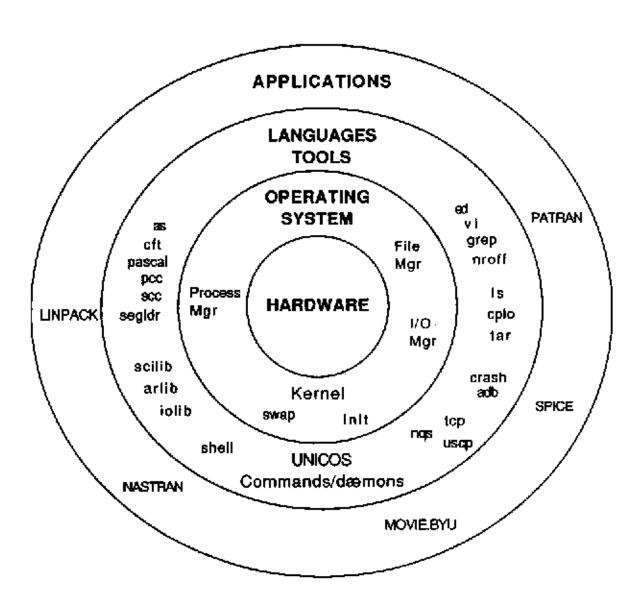

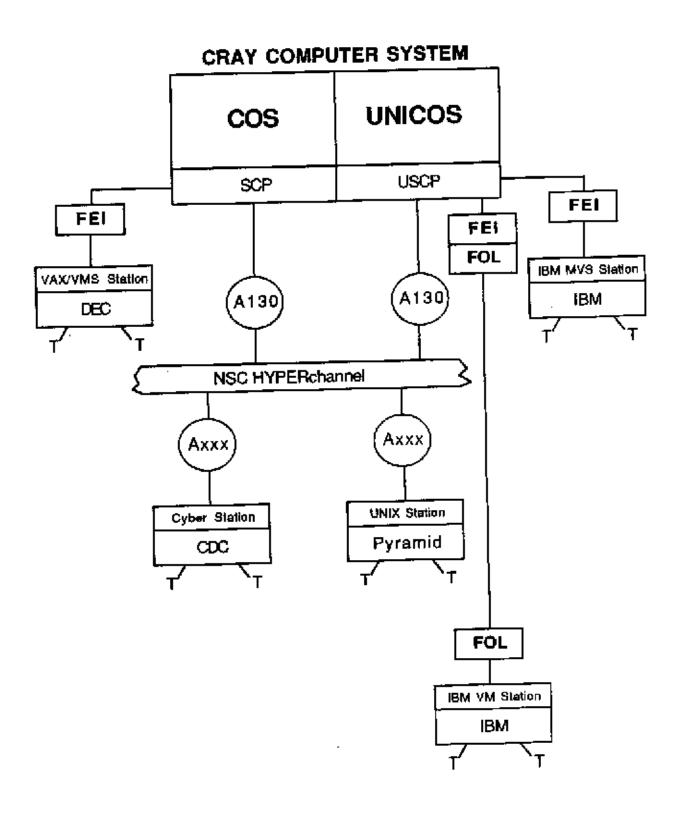

The two operating systems that Cray supports are COS (Cray Operating System) and UNICOS (Cray's operating system based on UNIX). Another operating system that runs on many Cray systems is CTSS. CTSS was developed and is supported by a Cray customer.

### Programming Languages/Compilers

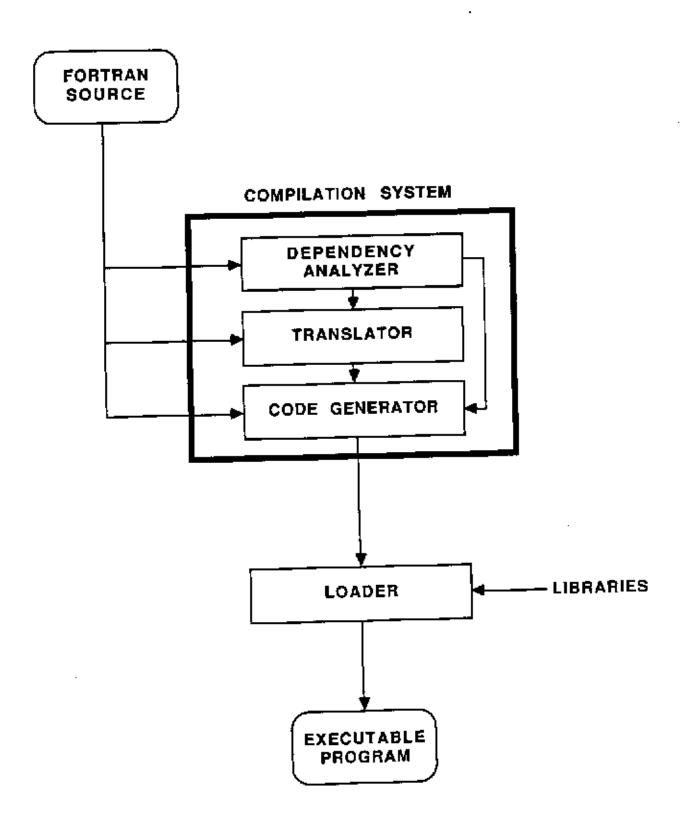

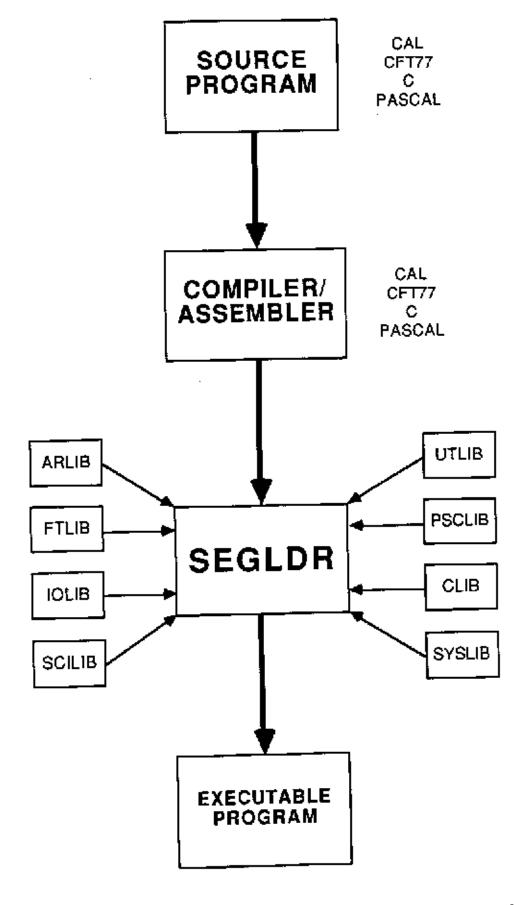

The programming languages that Cray has developed compilers for are FORTRAN (CFT and CFT77), Pascal, C, and CAL (Cray Assembly Language).

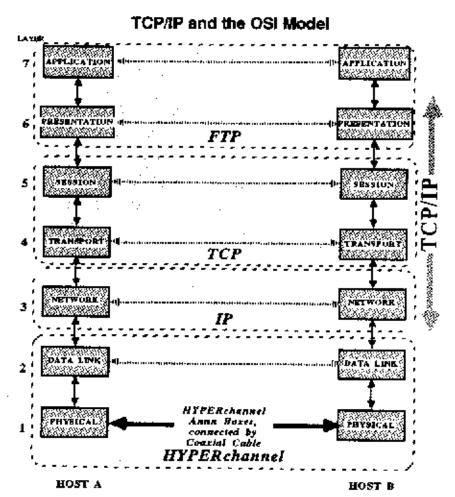

### Stations / Networking Protocols

A station is the software that resides on a front-end computer to provide communication with the Cray system. Some of the stations that Cray supports are IBM MVS and VM, CDC NOS and NOS/BE, DEC VAX/VMS, Data General RDOS, and AT&T Unix<sup>TM</sup>. Other front ends are supported with station software available from third parties. Cray now offers the TCP/IP protocol for network communications.

#### **Utilities**

A number of utility programs are available for dataset manipulation, editing, debugging, source and object code library maintenance, program loading, etc.

#### Libraries

A number of libraries exist to provide subprograms in the areas of arithmetic, i/o, scientific routines, utilities, etc.

#### **Applications**

Cray Research Is not in the primary business of developing new applications programs. However, the applications department assists customers and third party software suppliers in converting and developing programs to run efficiently on Cray systems. The current **Directory of Supercomputer Applications Software** contains hundreds of programs in the areas of structural and mechanical engineering, electrical engineering, chemistry and biotechnology, nuclear engineering, computational fluid dynamics, petroleum reservoir simulation and seismology, mathematics, simulation, graphics and imaging, languages and tools, and others.

## THIS PAGE IS INTENTIONALLY LEFT BLANK.

## SECTION 2

Cray Product Familiarization

## **ARCHITECTURAL FEATURES**

Cray Research, Inc. Software Training assessments

THIS PAGE IS INTENTIONALLY LEFT BLANK.

#### **General Architectural Features**

This section addresses some of the underlying hardware architectural features that contribute to the high performance of Cray systems. Some of the features apply to all Cray systems while others apply to a specific machine.

Some of the concepts covered in this section are:

- Scalar Processing

- Vector Processing

- Pipelining of Functional Units

- Chaining

- Compressed Index/lote and Gather/Scatter

- Multiple Processors

- Multiprogramming

- Multiprocessing

- at the job level

- at the task level

- macrotasking

- microtasking

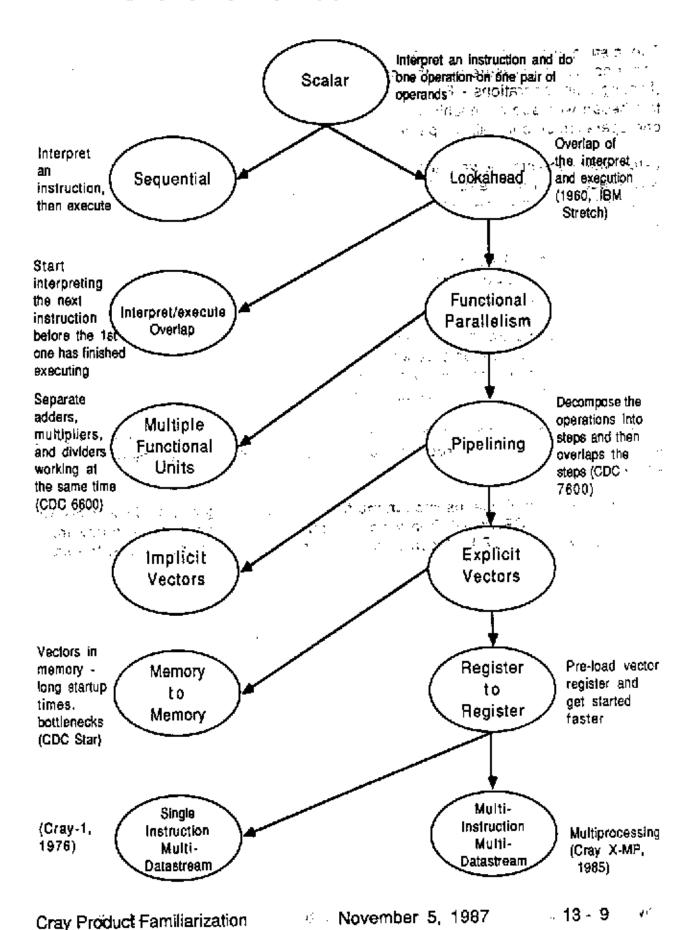

### Scalar Processing

Supercomputers, like more conventional computers, are able to do computations in scalar mode. Unlike conventional computers, supercomputers can also compute in vector mode. Before looking at vector processing, it is important to review scalar processing.

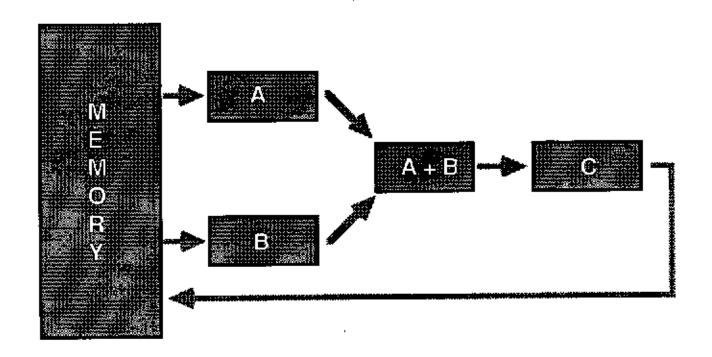

The main concept with scalar processing is that scalar computations deal with a single pair of numbers at one time; that is, one instruction performing one operation at a time. The diagram on the right illustrates a scalar add operation on a Cray computer. Other computers that do scalar processing operate in a similar way.

The diagram on the next page shows the adding of two numbers giving a third number as a result. To do this on the Cray and other computers typically takes four steps (instructions). In this case the original two numbers are in memory and the resulting number will be placed in memory.

| Step 1 | Load number A into a register                    |

|--------|--------------------------------------------------|

| Step 2 | Load number B into a register                    |

| Step 3 | Add A and B putting the result C into a register |

| Step 4 | Store the result C into memory                   |

Although scalar processing does not yield the computational rates that vector processing does, it is important that a supercomputer has high scalar performance. Many scientific problems do not lend themselves to vector processing. Even problems that can be programmed in vector mode still may have large scalar processing requirements. Cray systems provide an excellent balance of high scalar and vector performance.

## Scalar Processing

## Cray Assembler Language (CAL) example:

| S1     | 49    | Store the value 49 in S1             |

|--------|-------|--------------------------------------|

| S2     | 51    | Store the value 51 in S2             |

| \$3    | S1+S2 | Store the value of S1+S2 in S3       |

| TOTAL, | \$3   | Store the value 53 at symbolic       |

| , -,   |       | location TOTAL in central memory     |

|        |       | Address TOTAL contains the value 100 |

#### **Vector Processing**

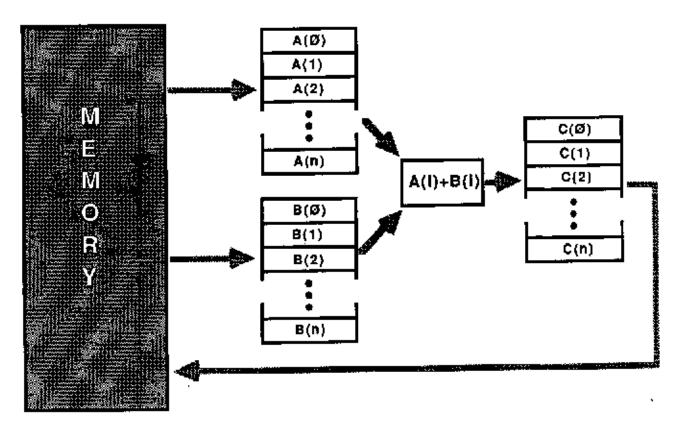

High performance vector processing capabilities are what make a supercomputer super. The important concept to grasp here is that in vector processing mode, computations are made with groups of numbers (vectors) as opposed to the single sets of numbers processed in scalar mode; that is, one instruction operates several inputs, producing several outputs. The diagram on the right page illustrates a vector add operation on a Cray computer. The actual implementation of vector processing on other systems may be quite different in detail.

The diagram on the next page illustrates adding one group of numbers (vector A) and another group of numbers (vector B) giving a result (vector C). Vector A and B initially reside in memory and the resulting vector will be stored in memory. On the Cray, this typical operation requires four main steps (instructions).

| Step 1 | Load vector A from memory Into a Vector register                                       |

|--------|----------------------------------------------------------------------------------------|

| Step 2 | Load vector B from memory Into a Vector register                                       |

| Step 3 | Add the vectors A and B putting the resulting vector C<br>Into another vector register |

| Step 4 | Store vector C into memory                                                             |

In the vector add operation, the first elements of vectors A and B are added giving the first element in vector C. Then, the second elements of A and B are added giving the second element of vector C, and so forth until all the elements of the vectors are processed.

On Cray systems, the number of elements (numbers) that can be processed in a single vector operation is limited by the length of the vector registers. There are eight vector registers in a single Cray CPU, each capable of holding 64 elements. A vector operation may operate on any vector size between 1 and 64.

A feature of the CRAY FORTRAN Compilers (CFT,CFT77) is its ability to autovectorize programs. The compiler analyzes the program to determine how to most efficiently run it (optimization). The programmer does not need to code for this feature.

## Vector Processing

Cray Assembler Language (CAL) example:

(Note that more instructions are required in order to set up the vectors.)

| Α7    | 64      | Store the value 64 in A7                               |

|-------|---------|--------------------------------------------------------|

| VL    | A7      | Make the vector length 64                              |

| AØ    | VECTOR1 | Put the address of VECTOR1 in AØ                       |

| ν1    | ,AØ,1   | Copy the 64 elements at AØ to V1                       |

| ΑØ    | VECTOR2 | Put the address of VECTOR2 in AØ                       |

| V2    | ,AØ,1   | Copy the 64 elements at AØ to V2                       |

| V3    | V1+V2   | Add V1 to V2 and store result in V3                    |

| AØ    | VECTOR3 | Put the address of VECTOR3 in AØ                       |

| ,AØ,1 | V3      | Copy the 64 elements in V3 to the address stored in AØ |

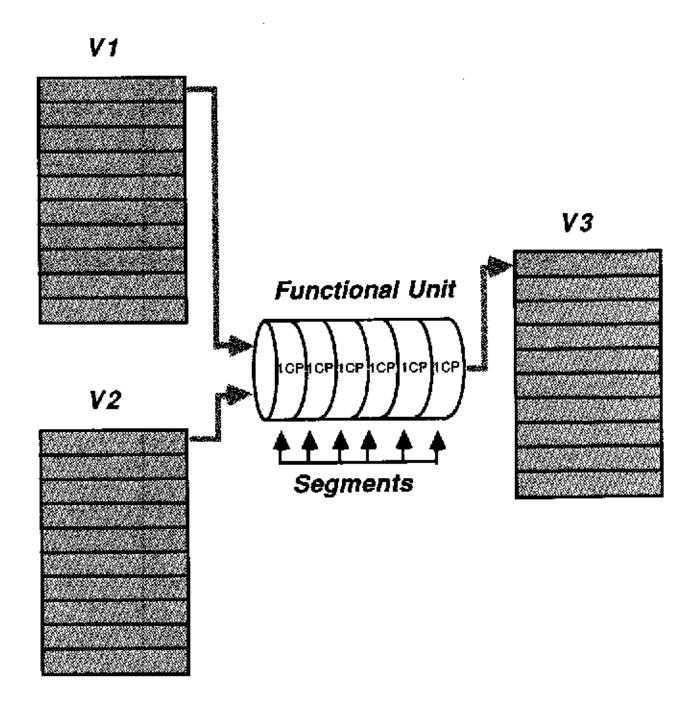

### **Pipelining**

The concept of pipelining applies to the design of the functional units in a Cray CPU. A Cray CPU contains a number of functional units, each designed for a specific purpose. For example, there is a separate functional unit to do floating point adds and a separate functional unit to do floating point multiplies. Since the functional units operate independent of each other, operations can occur in parallel (such as floating point adds and multiplies.)

The diagram on the next page illustrates the pipelined design of the functional units. Each functional unit is made up of several separate segments. Each segment is designed to do a part of an operation. The functional unit operates as follows:

In the first clock period of the operation the first elements of vectors V1 and V2 enter the first segment of the functional unit. On the second clock period the elements in the first segment of the functional unit move to the second segment and the second elements of V1 and V2 move into the first segment of the functional unit. This continues each clock period. Soon, results start leaving the functional unit and are entered into vector register V3 at the rate of one result every clock period. This rate can be used in calculating the peak megaflop rate of a particular system (more on this later).

Different functional units will have different numbers of segments depending on their complexity. For example, the reciprocal approximation functional unit has more segments than the floating point multiply functional unit, etc.

Cray terminology for this pipelining design is "fully segmented functional units".

## Pipelining

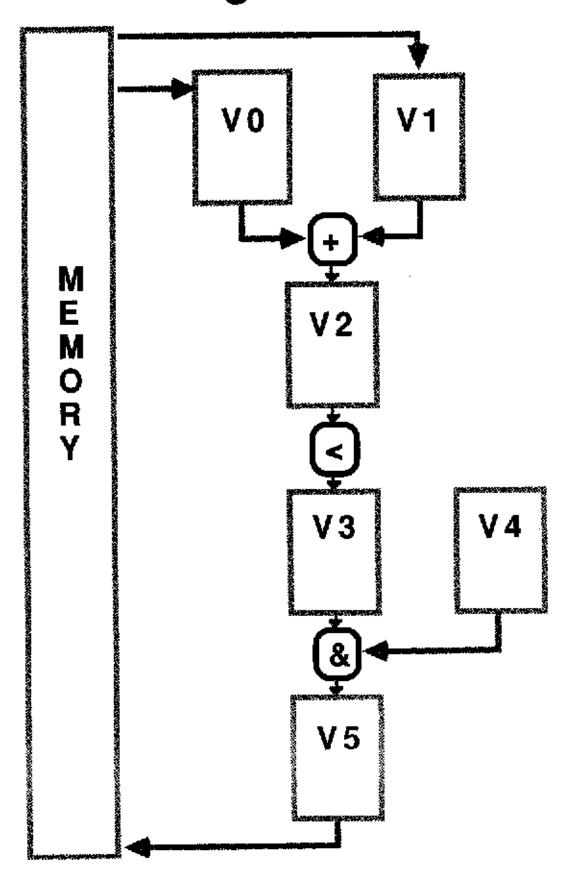

#### Chaining on the CRAY-1, X-MP, and Y-MP

The functional units in the CPU can function independently (in **parallel**). That is, an add could be taking place at the same time as a multiply. Because of this possibility, output from one operation can become input to another functional unit.

For example, the diagram on the next page shows two vector registers being loaded. Based on the pipelining function, as soon as VØ and V1 each contain one element, those elements may begin the process of being added together. Likewise, as soon as one element has been put into V2 it can go through the shift process and be put into V3 (a shift does things like chop off leading zeros, etc.).

Assuming V4 was already loaded, V3 and V4 can be **anded** (anding does a logical compare between the elements in V3 and V4 and comes up with a new number). The results can begin being written to memory as soon as one element has been put into V5.

## Chaining on a Y-MP

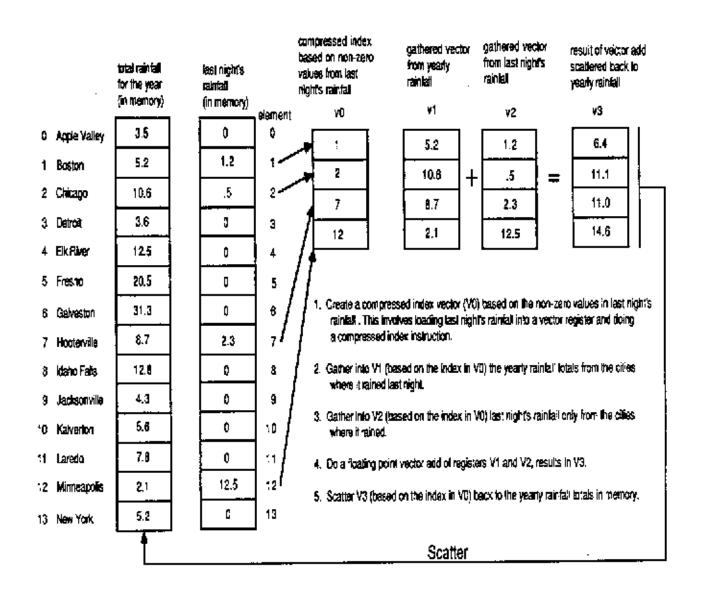

## COMPRESSED INDEX/IOTA AND GATHER/SCATTER

Some supercomputer programs such as those used in weather forecasting and in predicting where oil may be located deal with very large collections of data. Those collections often contain a lot of unuseable or unnecessary data. In order to more efficiently run the programs utilizing only the important data, Cray computers now offer an efficient means of locating it in memory.

Compressed Index is a means of creating an Index of the location of the important data. An example might be to make an index of all the locations which contain a non-zero value because the zeros are useless data for our program. By avoiding the locations containing zero we avoid wasting computer time dealing with them. A term used for groups of data which contain lots of unnecessary data is **sparse matrix**. Compressed index is know as **compressed lots** on the CRAY-2.

Once the index is created, a **gather** operation may be done which simply uses the index to find the non-zero data and copy it. Once copied, the data can be run through a functional unit to create new values. The new data (results) can then be copied back into the exact locations it originally came from by using the same index. This is called a **scatter** operation. Now the new data can be gathered using the same index and run through other functional units to come up with more new values, if needed.

Another term associated with gather/scatter and compressed index is **stride**. It simply is a way of setting up an index that allows gathering or scattering data on a fixed increment (e.g., every fifth data element). This is useful when the data dealt with is known to contain important data only specific incremental locations.

## Gather / Scatter / Compressed Index Example

### Cray Assembler Language (CAL) example

| NITERAIN | AØ gets address of NITERAIN array                                          |

|----------|----------------------------------------------------------------------------|

| ,AØ,1    | V1 gets a vector length of NITERAIN, stride=1                              |

| V1,N     | VØ gets index of non-zeros in V1                                           |

| VM       | S1 gets vector mask                                                        |

| PS1      | A1 gets population count of S1                                             |

| A1       | Vector length set to A1 (= # of non-zeros)                                 |

| .AØ.VØ   | V1 gathers non-zeros from NITERAIN                                         |

| , .      | AØ gets address of YEARRAIN                                                |

| .AØ.VØ   | V2 gathers non-zeros from YEARRAIN                                         |

| • •      | V3 gets floating point sum of V1 and V2                                    |

| V3       | V3 scattered back to YEARRAIN                                              |

|          | ,AØ,1<br>V1,N<br>VM<br>PS1<br>A1<br>,AØ,VØ<br>YEARRAIN<br>,AØ,VØ<br>V1+FV2 |

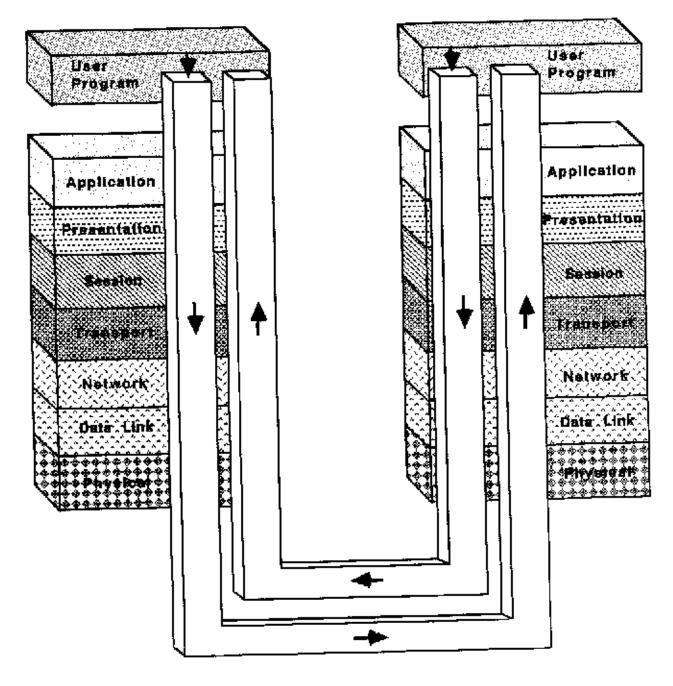

### Multiprogramming

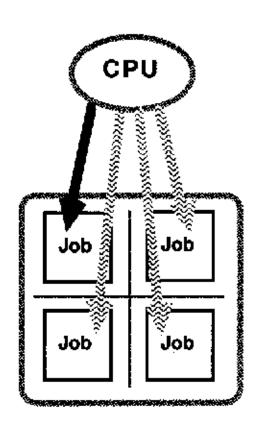

A computer would be very slow if it ran one program to completion before starting the next. Multiprogramming means that many programs can run concurrently on the system - each program is given a "time-slice" and then waits while another runs. This is also known as interleaving.

Throughput is improved by multiprogramming even though there is more system overhead involved. This is because of **parallel** system functions (several parts of the computer can be running at the same time).

In the case of multiprogramming, the output of one program can be routed back to a front-end computer while an incoming program is being loaded into memory and still another is executing ("number-crunching") in the CPU. The operating system keeps track of each job. It will assign a hardware component to complete a task and then, instead of walting for that task to finish, assign another idle component a task.

This requires a sophisticated operating system, but does not require the applications programmer to call for it.

# Multiprogramming

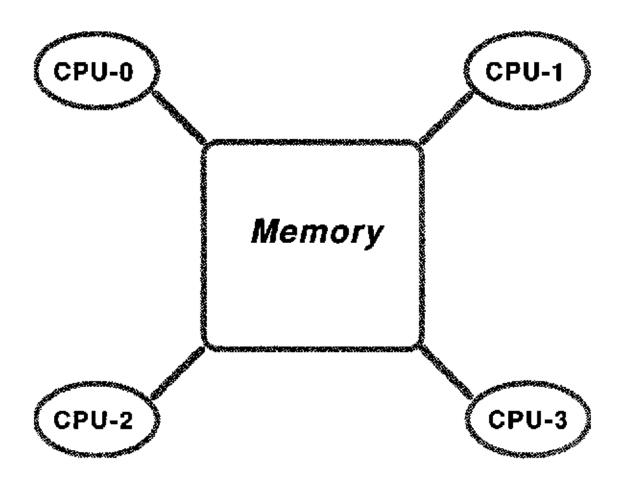

#### Multiprocessing

If one CPU is good, two or more should be better and that is true with the X-MP, CRAY-2, and Y-MP. Each CPU has its own identical set of functional units and registers operating in parallel. Multiprocessing takes that concept one step further by incorporating two or four CPUs in one machine. This increases the capacity of the machine as well as program throughput.

# Multiple Processors

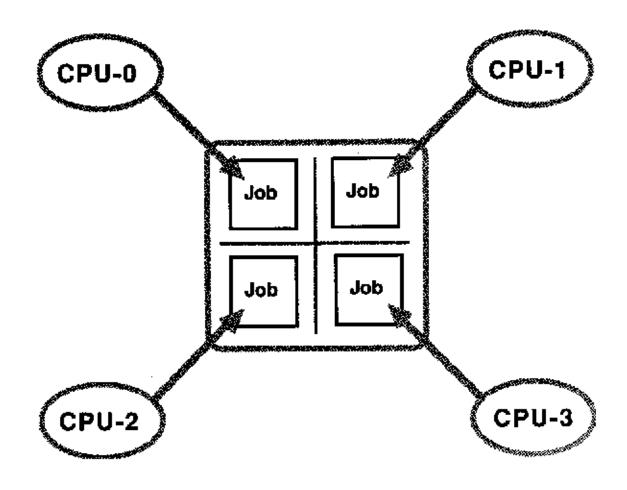

#### Multiprocessing at the job level

A machine with more than one processor can divide up the work load. With multiprocessing, incoming programs can be assigned a CPU. This allows for up to eight programs running in separate CPUs at any one time (on a Y-MP).

Multiprocessing requires the operating system to ensure that a program in one CPU does not conflict with a program in another CPU.

# Multiprocessing at the job level

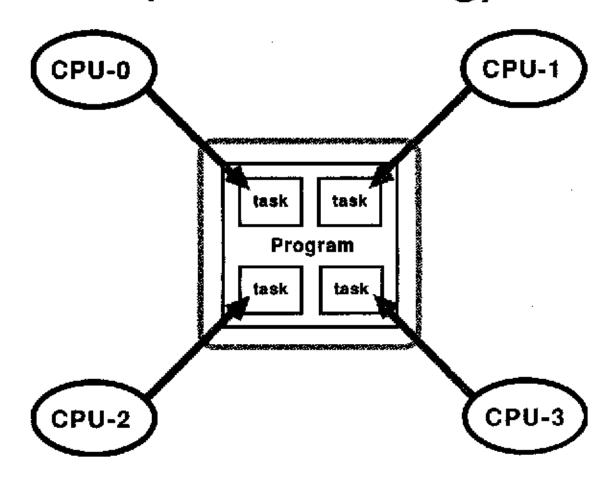

#### Multiprocessing at the task level (Macrotasking)

Imagine a program so large that it alone could use a whole system's resources for hours, days, or even weeks. Because there are programs like that, it would be more efficient to divide up the workload among more than one CPU.

The means for doing that is known as **multitasking**. This feature allows two or more parts of a program (tasks) to be executed in parallel which results in faster program execution than if the program ran serially.

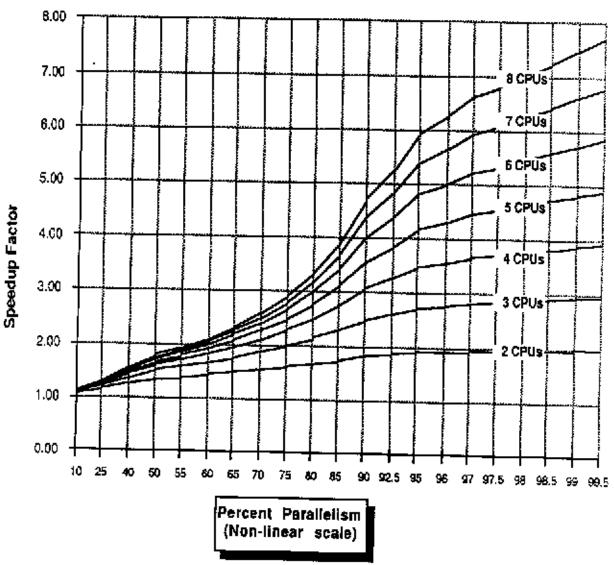

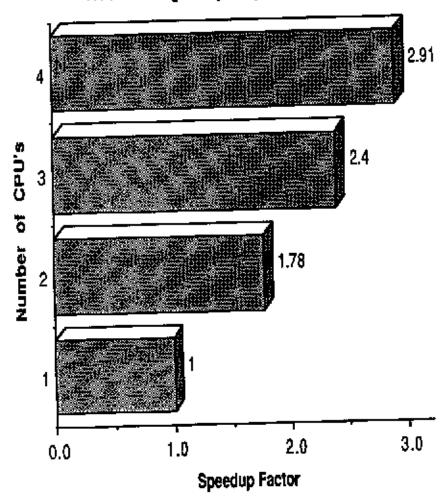

Experience shows that multitasked applications running on CRAY X-MP/2 computers can realize speed increases of 1.8 to 1.9 times over single-processor CRAY X-MP execution times; speed increases of 3.5 to 3.8 times have been achieved with CRAY X-MP/4 systems. The throughput of a multitasked application which utilizes all of a Y-MP's CPUs could be more than seven times faster than if it were run in only one of the Y-MP's CPUs.

One method of multitasking on a CRAY X-MP, CRAY-2, or Y-MP is called macrotasking.

To use macrotasking the program is modified to use FORTRAN-callable subroutines which define and synchronize tasks within subroutines. The system launches subjobs which compete for CPUs. For this reason macrotasking is best suited to programs with large tasks running with dedicated processors.

# Multiprocessing at the task level (macrotasking)

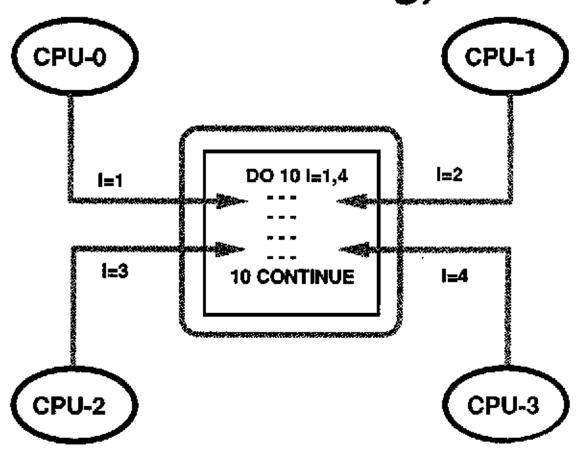

#### Multiprocessing at the task level (Microtasking and Autotasking)

Two other forms of multitasking available for use on CRAY computers are microtasking and autotasking. Microtasking is similar to macrotasking in that it divides up a single application program's work among two or more processors.

It is different, however, in that it is a dynamic function which operates at run-time. Instead of specifying portions of the program's code to be handled by different CPUs (as macrotasking does), microtasking looks for idle CPUs which it could use for parts of the program. If it can't find any, it will execute in its current CPU. This helps efficiently use the system's resources and allows faster execution of a program even on a mainframe in a production environment (many users).

Microtasking is primarily used with FORTRAN DO Loop-level routines. A DO loop is a series of computations done over and over a specified number of times. Microtasking uses a FORTRAN preprocessor called PREMULT that identifies DO loops which could be run independently (in parallel) on separate processors. As the program runs, each of the identified DO loops is executed in the next available CPU. PREMULT has its own efficiency monitor to allow observation of speed improvements. Microtasking uses compiler-like directives which makes it easy to use.

Microtasking is beneficial for programs with any size task running in either a dedicated or production (many users) environment.

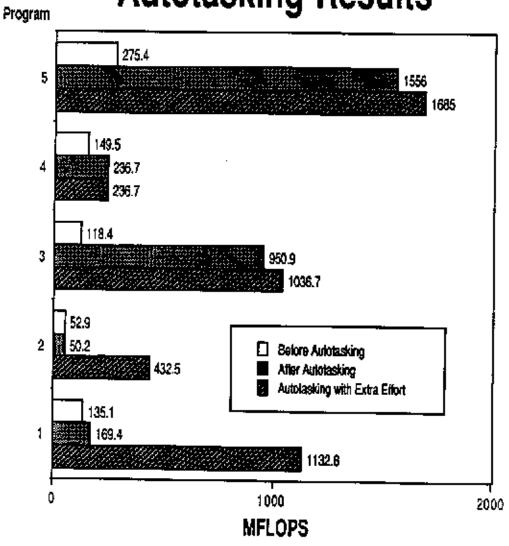

Autotasking does essentially all of the above steps in multitasking a program, but it does it automatically, with no user intervention required. It requires several passes through a program to analyze it, but it divides up the work as it sees fit. Autotasking can also include some microtasking code for special situations.

# Multiprocessing at the task level (microtasking and autotasking)

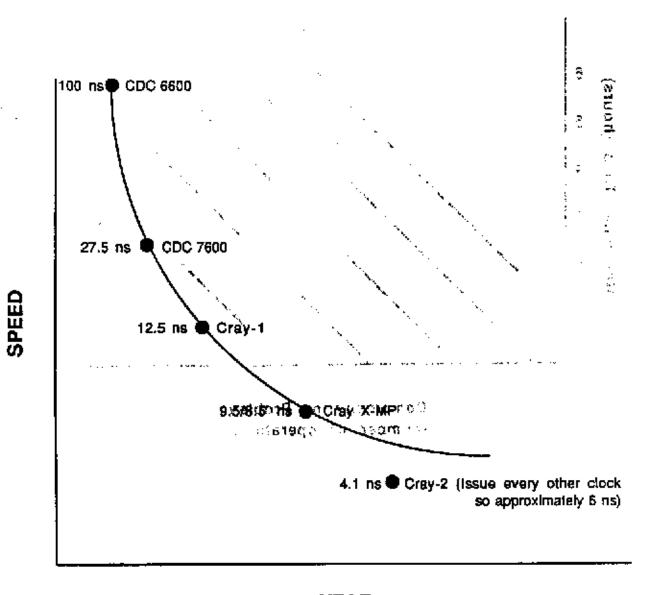

#### CLOCK RATE and MEGAFLOPS

Clock Rate and Megaflops (MFLOPs) are two terms often used in rating a supercomputer's processing speed. Clock rate (or clock period) refers to the timing or pulse of the computer. The smaller the number, the faster the rate at which the hardware can theoretically work. Of course, the distance between hardware components is critical for timing. That is why Cray computers are so compact, using very short wires and a circular design for instance. The number of ticks per second can be determined by the formula 1/clock speed (e.g., on a Y-MP with a 6.0 nanosecond clock the formula is 1/6.0-9 which equals 166 million ticks per second).

Supercomputer speed is often rated in **megaflops** rather than ticks per second. Megaflop stands for "millions of floating point operations per second". Floating point numbers include numbers which contain a decimal point (e.g., 132.098) and large numbers which are more easily defined using exponential notation (e.g., 10<sup>23</sup>). Since these types of numbers are more often used in supercomputer applications than simple integers (whole numbers), how fast they can be added, multiplied, etc. is considered a good means of measuring the speed of the computer.

One floating point operation per second would be like completing this operation (1.23+8.1=9.33) in one second. One megaflop would be one million of them per second. Because Cray computers incorporate multiprocessing and chaining, the following formula is used to determine megaflops on Cray computers: Ticks per second x number of CPUs x number of functional units running in parallel.

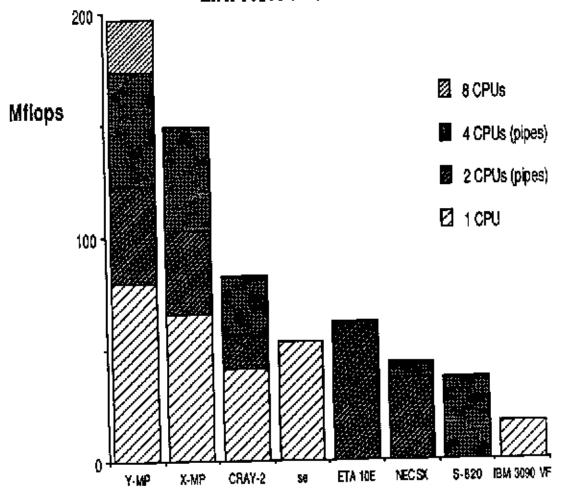

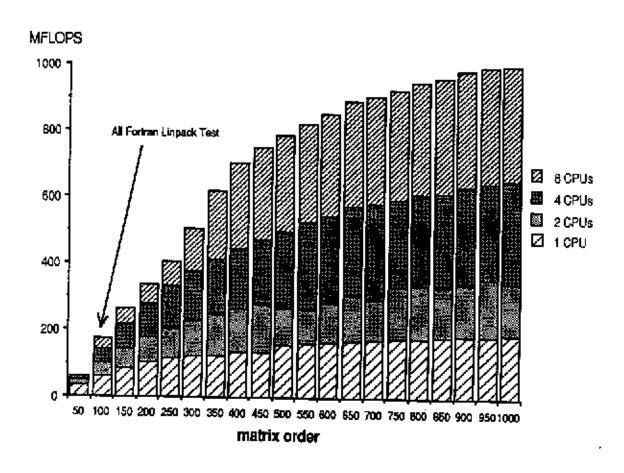

### **CLOCK RATES AND MFLOPS**

|              | Clock<br>Rate<br>(ns) | Ticks/<br>Second<br>(millions) | MFLOPS<br>(1 F.U.) | MFLOPS<br>(2 F.U.) | (2 F.U.)<br>x 2 | MFLOPS<br>(2 F.U.)<br>x 4<br>CPUs |      |

|--------------|-----------------------|--------------------------------|--------------------|--------------------|-----------------|-----------------------------------|------|

| CRAY-1       | 12.5                  | 80                             | 80                 | 160                | • •             |                                   |      |

|              | 9.5                   | 105                            | 105                | 210                | 420             | 840                               |      |

| CRAY X-MP EA | 8.5                   | 117                            | 117                | 234                | 468             | 936                               |      |

| CRAY-2       | 4.1                   | 243                            | 243                | 486                | 972             | 1944                              |      |

| Y-MP         | 6.0                   | 166                            | 166                | 332                | 664             | 1328                              | 2656 |

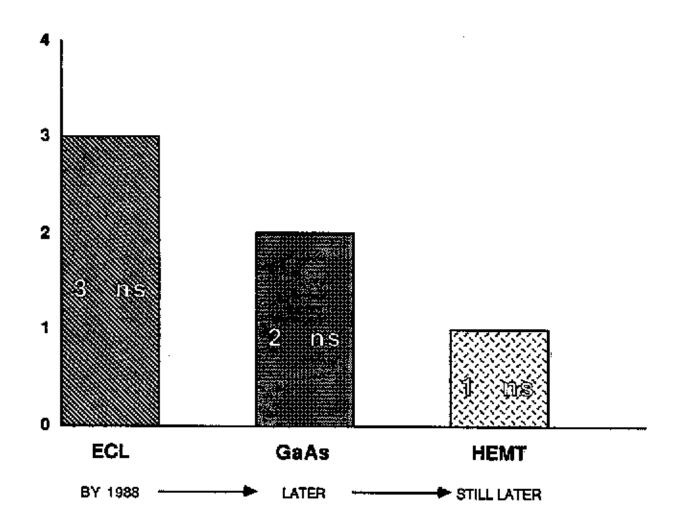

#### CRAY LOGIC AND MEMORY CHIP TECHNOLOGY

Probably the two computer components that have had the greatest impact on the speed and size of Cray computer systems are the logic and memory chips.

#### LOGIC CHIPS

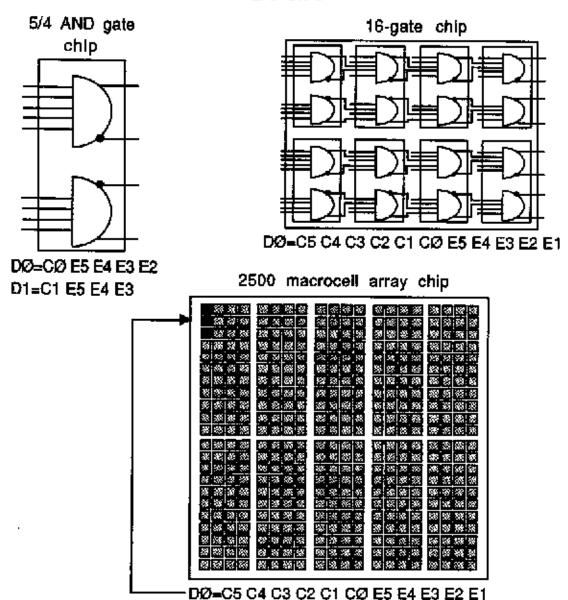

Logic chips contain the circuitry (on/off switches) which, when used in certain combinations, perform all the possible instructions a Cray computer is designed to do such as calculating answers to mathematical equations. The chips are specifically designed to perform these functions by using a branch of mathematics known as Boolean Algebra (which was invented by George Boole in the 19th century who believed that everything in the universe could be explained logically in terms of man and God (or 1 and Q)).

CRAY-1 systems used simple 5/4 AND gates in combinations. These chips contain only two gates (switches). Because of this, it took 550 2-board modules to make one CPU. The X-MP and all CRAY-2 systems were designed to use 16-gate logic chips. This, in effect allows eight times the logic on one chip, although not all 16-gate chips use all 16 gates. This chip density effectively decreased the size of a CPU in half.

Currently, the Y-MP and the X-MP EA incorporate 2500-gate array logic chips. These chips are roughly equivalent to 1250 5/4 AND gate chips and one chip is roughly equal to one X-MP module. Because of these chips, one CPU now fits on one Y-MP module, although the module is larger than an X-MP module. The Y-MP uses these chips exclusively and the X-MP EA uses some 2500-gate and some 16-gate chips. Some of the 2500-gate chips are produced in Chippewa Falls. The 2500-gate array chips are considered VLSI (Very Large Scale Integration) chips.

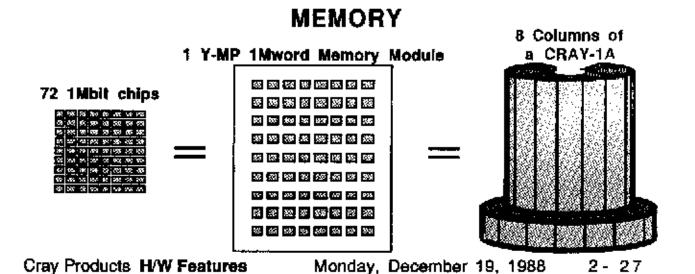

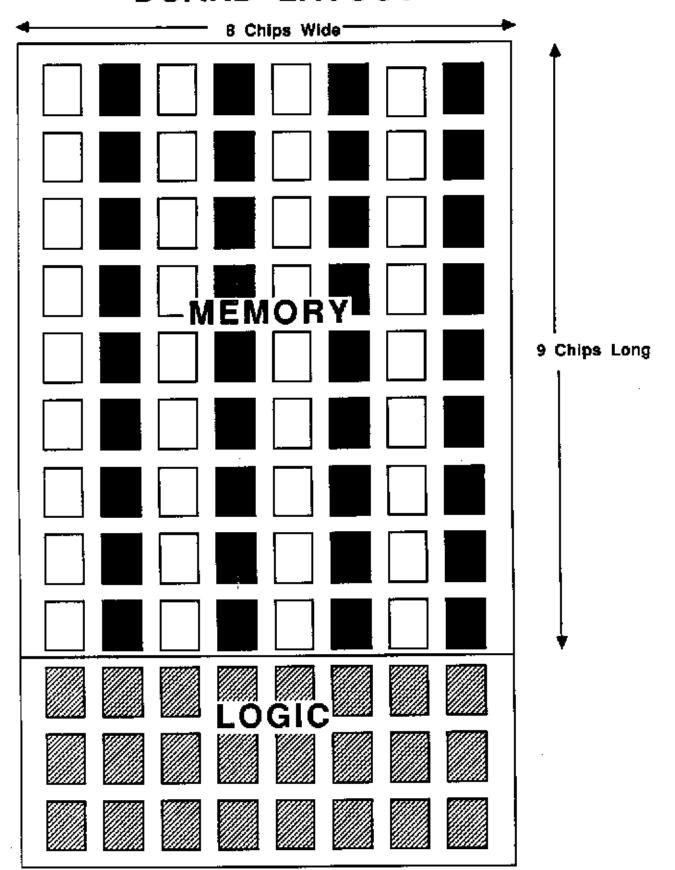

#### MEMORY CHIPS

As with logic chips, memory chip technology has improved over time. Today's memory chips are much denser (store more data) and faster (to read and write the data) then the memory on the CRAY-1. The CRAY-1A used 1 Kbit memory chips; today an SSD uses 1 Mbit chips. One Y-MP memory module equals 72 1Mbit SSD memory chips which equals 8 columns on a CRAY-1A.

Cray computer systems have used different types of memory. One type is called ECL (Emitter-coupled logic) memory. These chips are quite fast, but they require a lot of electrical power, generate a lot of heat, and take up a lot of space. Capacity of ECL memory chips used on Cray computers ranges from 1Kbits to 256Kbits per chip. ECL chips on the Y-MP have an access time of 15 ns.

Another type is called MOS (Metal-oxide semiconductor) memory. MOS memory is cheaper, denser, requires less power, and generates less heat than ECL memory. But, it is also slower. Capacity of MOS chips used on Cray computers ranges from 16Kbits to 1Mbits per chip. There are two types of MOS chips used on Cray computers: DRAM and SRAM. DRAM (Dynamic Handom Access Memory) chips are cheap, but use capacitors to hold the electrical charge representing the 1 or Ø. This requires overhead for the computer to recharge the capacitors to hold their value. DRAM chips on the CRAY-2 have an access time of 80 ns. SRAM (Static Random Access Memory) chips do not need the refresh and so are faster. SRAM chips on the CRAY-2 have an access time of 55 ns.

# CRAY CHIP TECHNOLOGY HISTORY

#### **CRAY PRODUCT STRATEGY**

- Deliver the fastest vector and scalar processors

- Parallel processing via multitasking and microtrasking

- Commitment to large real memories

- Support of very high-speed I/O

- Fast, efficient software

- System integration supporting a variety of mainframes

- Expanding application software

- On-site support and maintenance

- Close customer contact

- Large R & D expenditures for hardware and software

# Cray System Comparisons

| Model                                   | 1/A,B | 1/5          | 1/5/         | X-MP<br>14se | X-MP         | X-MP         | X-MP        | CRAY-<br>2     | CRAY-<br>2S   | X-MP<br>EA/1se |              | X-MP<br>EA/2 | X-MP<br>EA/4 | Y-MP2       | Y- <b>VIP</b> 4 | Y-VIPE              |

|-----------------------------------------|-------|--------------|--------------|--------------|--------------|--------------|-------------|----------------|---------------|----------------|--------------|--------------|--------------|-------------|-----------------|---------------------|

| CPU Number of CPUs                      | 1     | 1            | 1            | ;            | 1            | 2            | 4           | 4              | 2,4           | 1              | 1            | 2            | 4            | 1,2         | 2,4             | 4,8                 |

| Clack period (re)                       | 12.5  | 12.5         | 12.5         | 10.0         | 9.5,<br>8.5  | 9.5,<br>8.5  | 9.5,<br>8.5 | 4.1            | 4.            | 8.5            | 8.5          | 8.5          | 8.5          | 6.0         | 6.0             | €.0                 |

| Memory Sze (mm)                         | .5,*  | .5,1.<br>2,4 | .5,1,<br>2.4 | 4            | 4, B,<br>18  | 2.4<br>8,18  | 4,8,<br>15  | 256,<br>512    | 64,<br>129    | 4,16           | 15,32,<br>64 | 16,32,<br>64 | 16,32,<br>64 | 18,32       | 18,12,<br>64    | 32,64,<br>128       |

| Memory chip<br>technology               | ECL   | ECL          | MOS          | MOS          | MOS          | ECL,<br>MICS | ECL,<br>Mos | Dymamic<br>MOS | Static<br>MOS | MOS            | MOS          | MOS          | MOS          | ECL         | ECL             | ÉCL                 |

| Banks                                   | 8,18  | 9,16         | <b>8</b> ,16 | 16           | 16,32        | 16,32        | 32,64       | 128            | 64,<br>128    | <b>1</b> 6     | 32.64        | 32,84        | 32,64        | 64          | 128             | 256                 |

| Viemory ports                           | 1     | • •          | -            | 5            | 6            | 2:4          | 4x4         | dr1            | 2x1,<br>4x1   | 5              | 5            | 2x4          | 424          | 1x5,<br>2x4 | 2x4.<br>4z4     | 4%4,<br>884         |

| I/O I/O subsystem                       | No    | Opt.         | Opt          | Built-in     | Yes          | Yes          | Yas         | FGP            | FGP           | Yea            | Yes          | Yes          | Yes          | Yes         | Yes             | Yes;<br>Opt,<br>2nd |

| SSD channel<br>(Mbytes/s)               |       | <b>'</b> 8   | 100          | NA.          | 100,<br>1006 | 1500         | 2x<br>1000  | Ha             | No            | MA             | 1000         | 1003         | 2x<br>:000   | 1x<br>1000  | 2x<br>1000      | 2x<br>1000          |

| High-speed channel pairs (100 Mbytus/s) | -     | 1,2          | 1.2          | :2           | 1,2          | 2            | 4           | ,              | •             | 1,2            | 1.2          | 2            | •            | 1,2         | 1.2,‡           | 1,2,4               |

| Low-speed channel<br>peirs (8 Mbytes/s) | 12    | 12           | 12           | 4            | -            | 4            | 4           | -              |               | 1              | 4            | 4            | 4            | 1,2         | 1,2,4           | 1.2,4               |

| Mainfeame Columns :                     | 12,8  | 12,8         | 12,8         | 6            | 6            | 12,8         | 12          | 14             | 14            | 6              | 6            | 12,8         | 12           | 1           | •               | 1                   |

#### THIS PAGE IS INTENTIONALLY LEFT BLANK.

## SECTION 3

Cray Product Familiarization

# CRAY Y-MP Computer System

#### THIS PAGE IS INTENTIONALLY LEFT BLANK.

# CRAY Y-MP SUPERCOMPUTING PHILOSOPHY

Innovative VLSI architecture is incorporated in:

CPU technology

same functionality as X-MP using less real estate

Hardware design

- yields significant performance improvements

Memory accessing

- larger numbers of paths to central memory

- Improved reliability

Fewer parts

I/O capability

Second I/O subsystem available option allows

Unprecedented amount of accessible disk space

- Wide variety of memory and SSD options

- Compatible with CRAY X-MP

CRAY X-MP (X-mode) instruction set may run on the CRAY Y-MP

#### **CRAY Y-MP SERIES CHARACTERISTICS**

- Highly modular architecture in three frame types

- 1, 2, 4, or 8 CPUs

- 6 nanosecond clock period

- 16/32/64/128 Mwords Central Memory

- Extensive use of VLSI logic circuits

#### Y-MP Central Memory

- Up to 128 million words, depending on model, enabling users to solve large problems without the need for as much disk I/O

- Directly addressable for faster reads and writes

- Memory size is upgradable on most models

- Memory integrity is checked using single-bit error correction, double-bit error detection (SECDED) logic

- Multiprocessor Y-MPs share a central memory organized in interleaved memory banks that can be accessed independently and in parallel during each machine clock period

- Each processor has four parallel memory ports connected to central memory: two for vector and scalar fetches, one for result store, and one for independent I/O operations (such as to the IOS and SSD); the CRAY-1system had only 1 bidirectional memory port

- The multiport memory has built-in conflict resolution hardware to minimize delays and maintain the integrity of simultaneous memory bank references

- 15ns 64Kbit or 256Kbit ECL memory is or will be used on all Y-MP models

#### **CRAY Y-MP SERIES CONFIGURATIONS**

| Product       |       |             | Memory Opt       | mory Options* |           |           |  |

|---------------|-------|-------------|------------------|---------------|-----------|-----------|--|

| <u>Family</u> | Frame | <u>CPUs</u> | <u>128 Mword</u> | 64 Mword      | 32 Mword  | 16 Mword  |  |

| Y-MP          | 8     | 8           | Y-MP8/8128       | Y-MP8/864     | Y-MP8/832 |           |  |

|               |       | 4           | Y-MP8/4128       | Y-MP8/464     | Y-MP8/432 |           |  |

| Y-MP          | 4     | 4           |                  | Y-MP4/464     | Y-MP4/432 | Y-MP4/416 |  |

|               |       | 2           |                  | Y-MP4/264     | Y-MP4/232 | Y-MP4/216 |  |

|               |       | 1           |                  | Y-MP4/164     | Y-MP4/132 | Y-MP4/116 |  |

| Y-MP          | 2     | 2           |                  |               | Y-MP2/232 | Y-MP2/216 |  |

|               |       | 1           |                  |               | Y-MP2/132 | Y-MP2/116 |  |

Models in italics will be available for delivery in the second quarter of 1990.

# **CRAY Y-MP FOOTPRINTS**

### CRAY Y-MP2

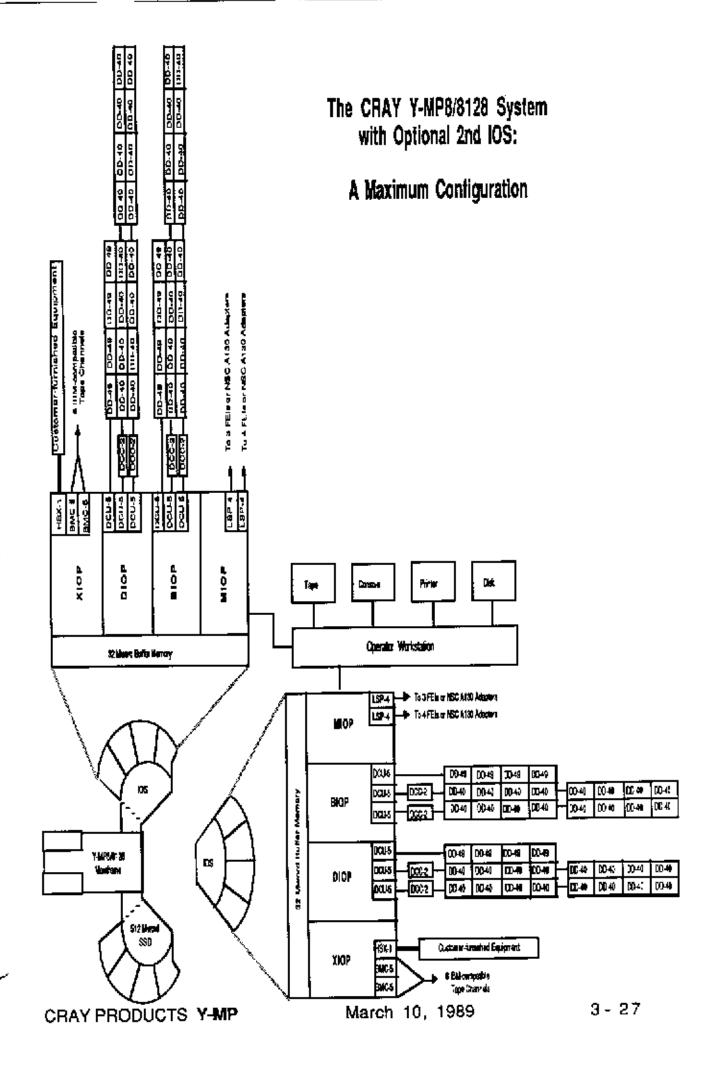

CRAY Y-MP8 with 2nd optional IOS

CRAY PRODUCTS Y-MP

March 10, 1989

3 - 5

#### **VLSI ARCHITECTURE**

The VLSI architecture used on the Y-MP is based on 2500-gate macrocell array chips. Because of the use of these chips the following is possible in the Y-MP:

- Reduced module count

- Improved reliability

- Lower usage of costly floor space

- Faster repair capability

- A faster clock period

#### Y-MP MODULES

- Each module:

- measures 23.3 in. x 12.8 in. x 1.4 in.

- consists of four printed circuit boards and cold plate assemblies

- cold plate assemblies are made up of two hollow cold plates with a printed circuit board mounted on each side of the cold plates

- printed circuit boards have 12 layers and measure 11 in. x 21.2 in. Each board contains 4 million traces and spaces, and 8,000 buried resistors

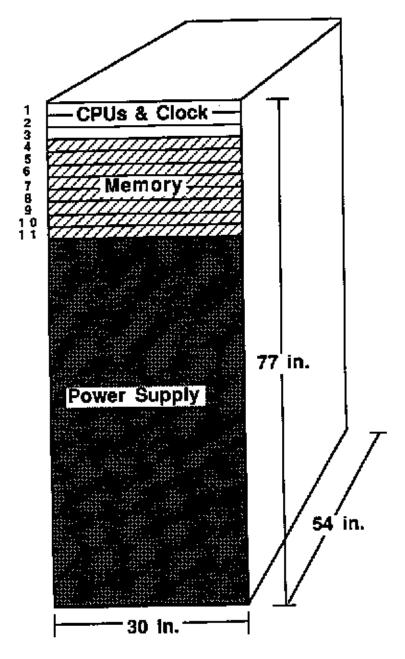

#### Y-MP2 CHASSIS COLUMN

- Total of 11 slots in one column.

- 1 or 2 CPU modules.

- Up to 8 memory modules

- 1 system clock module

## Y-MP2 CHASSIS DIMENSIONS

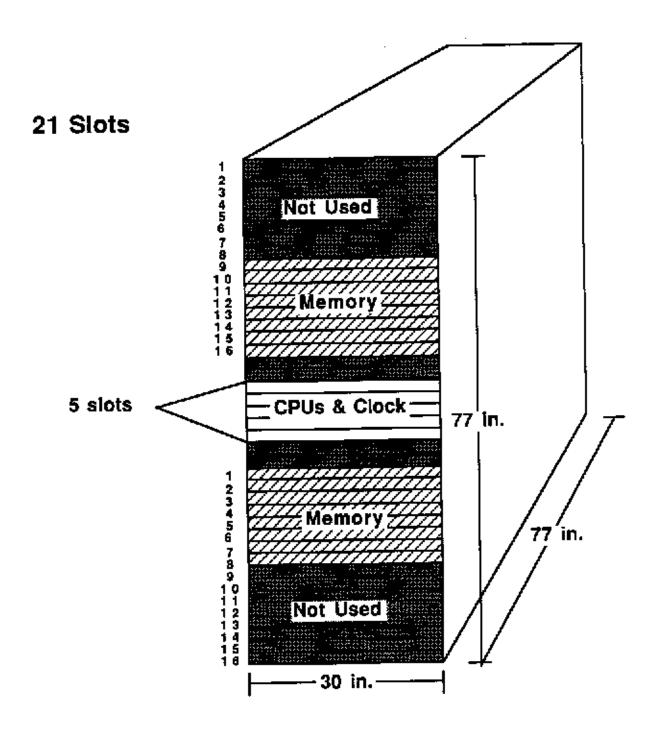

### Y-MP4 CHASSIS COLUMN

- Total of 21slots in one column

- 1, 2, or 4 CPU modules

- Up to 16 memory modules

- 1 system clock module

### Y-MP4 CHASSIS DIMENSIONS

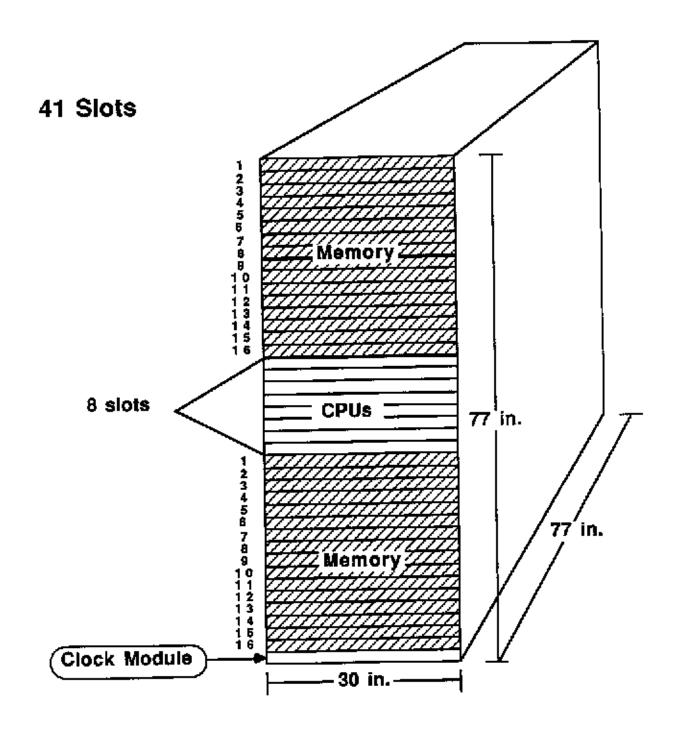

### Y-MP8 CHASSIS COLUMN

- · Total of 41 slots in one column

- 4 or 8 CPU modules

- Up to 32 memory modules

- 1 system clock module

### Y-MP8 CHASSIS DIMENSIONS

### Y-MP SHARED RESOURCES

#### CENTRAL MEMORY

Word width

- Data bits 64 - Error Correction bits 8

Memory size (Mwords)

Number of banks (64 per section)

16, 32, 64, 128

64, 128, 256

Number of ports per CPU

#### I/O SECTION

VHISP channels (1000 Mbytes/s)

HISP channels (100 Mbytes/s)

LOSP channels (6 Mbytes/s)

2, 4, 8

2, 4, 8

# SHARED REGISTERS, NINE CLUSTERS CONSISTING OF:

Shared address (SB) 32 bits each

Shared scalar (ST) 64 bits each

Semaphore (SM) 1 bit each

32

REAL TIME CLOCK, 64 BITS

### Y-MP8/832 PHYSICAL CHARACTERISTICS

(excluding attached IOS and SSD)

Floor space 18.4 square feet

Weight 5,000 pounds

Height 6.3 feet

Power 163 KVA

Cooling 80 gallons per minute Fluorinert (2 gallons per

minute through each module)

10 degrees F. temperature difference in/out

42 tons cooled by chiller

1

### **CENTRAL MEMORY I/O PORTS**

| Масhіле | Ports/Processor            | Total |

|---------|----------------------------|-------|

| Y-MP2/1 | 2 Read<br>2 Write<br>1 I/O | 4     |

| Y-MP2/2 | 2 Read<br>2 Write<br>1 I/O | 8     |

| Y-MP4   | 2 Read<br>2 Write<br>1 I/O | 16    |

| Y-MP8   | 2 Read<br>2 Write<br>1 I/O | 32    |

- Shared Central Memory (16 Million to 128 Million 64-bit Words)

- 4 Memory Ports per CPU

CRAY PRODUCTS Y-MP

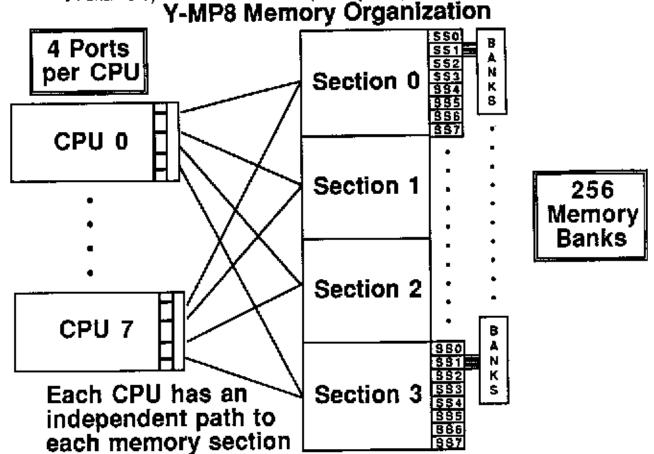

Each of eight CPUs can perform two reads, one write, and one I/O to central memory at the same time. At the rate of 4 64-bit words generated each clock period, peak memory bandwidth is 340 Gbits/s (8 CPUs \* 4 words/cp \* 64 bits/word)/6.0 ns = 340 Gbits/s (42.5 Gbytes/s) assuming no bank conflicts. This compares with 120 Gbits/s on an X-MP/48 system \* 4 CPUs \* 4 words/cp \* 64 bits/word)/8.5 ns = 120 Gbits/s (15 Gbytes/s) assuming no bank conflicts.

December 19, 1989

3 - 13

#### **CRAY Y-MP CONCEPTS**

- CPU has scalar and vector instructions.

- Eight vector registers per processor, each with 64 x 64-bit elements

- All arithmetic is register-to-register.

- Eight independent functional units per processor can be used by vector instructions

- Pipelining:

- All functional units are fully segmented; after initial startup,

results are generated at the rate of one per clock period per processor.

- Vector instructions using independent resources may execute in parallel

- Chaining:

Result vector is eligible to become an operand once the first element has been computed

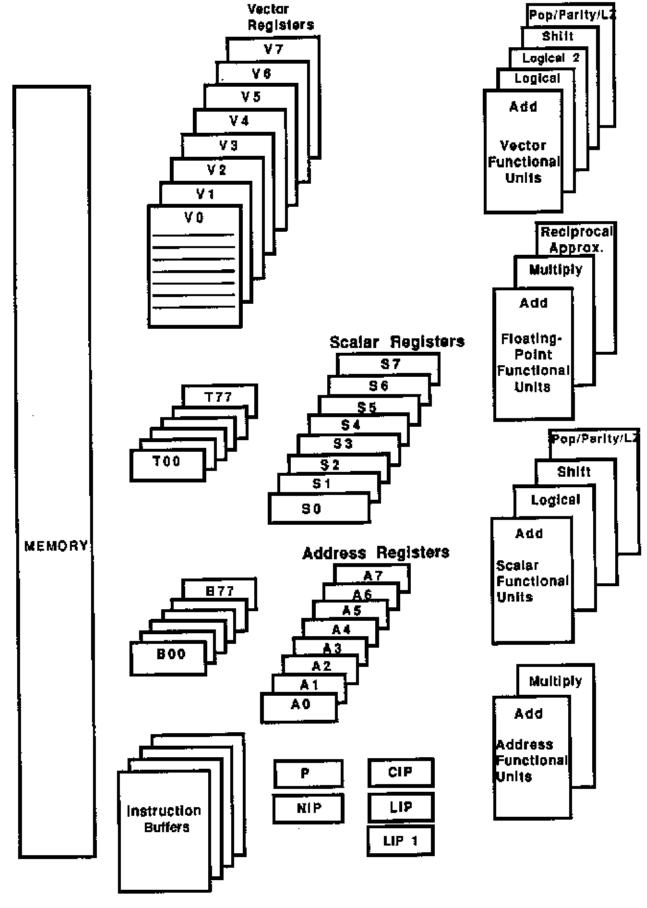

#### CPU COMPUTATION SECTION

#### Each CPU features:

- 6.0 ns Clock Period

- 14 functional units

- 8 32-bit address registers (A registers)

- 64 32-bit intermediate address registers (B registers)

- 8 64-bit scalar registers

- 64 64-bit scalar save registers (T registers)

- 8 64-element (64-bit) vector registers

- Flexible chaining

- 64-bit floating-point arithemetic

- 64-bit Integer arithemetic

#### CPU CONTROL SECTION

- Four Instruction Buffers Each Holding128 16-bit Instruction Parcels

- Instruction Buffers Loaded at 1 Word per Clock Period

- Normal and Interprocessor Interrupt Handling

- Constant Stride Addressing

- Gather/Scatter and Compress Index on all models

- Separate Program and Data Field Protection in Memory

#### CPU COMMUNICATION SECTION

- 9 Clusters of Intercommunications Registers

- 8 Shared Address (32-bit)

- 8 Shared Scalar (64-bit)

- 32 Synchronization (1-bit) semaphores

- Monitor Mode Interprocessor Interrupts

- Hardware Deadlock Detection

- Real-time Clock

- Above hardware Shared by Multiple Processors

Cray Y-MP Simplified Block Diagram

#### FUNCTIONAL UNITS

The functional units in a Y-MP CPU are fully segmented to allow pipelining and chaining. That is, the specific operations required to complete an operation are broken down into one-clock period segments. This allows results to be generated at the rate of one per clock period per CPU. The types of functional units and their uses is as follows:

#### Address functional units

Addition Performs 32-bit Integer addition or subtraction; subtraction is accomplished by a

process that essentially adds the negative of the number to be subtracted

Multiplication Performs 32-bit integer multiplication

Scalar functional units

Addition Performs 64-bit addition or subtraction; subtraction is accomplished in the same

manner as an address add

Shift (single or

double)

Shifts up to 128-bits (two concatenated S registers) to another S register

resulting in a field of up to 64 bits

Logical Performs bit-by-bit manipulation of 64-bit quantities from S registers; it is used to

compare two sets of numbers for things tike matches or differences

Pop/Parity/

Leading Zero

Counts the number of bits in an S register having a value of 1 (population count); it can also report if that sum is odd or even (parity); and it can count the number of

leading bits (from left) which are equal to zero

**Vector Functional Units**

Addition Performs 64-bit addition or subtraction as Scalar Addition, above, except each

operand is just one element of a possible 64 elements in the V register.

Shift Performs a shift like a Scalar Shift, above, but each shift is on one or two elements

of a possible 64 elements within the V register

Logical Performs logical compares like Scalar Logical, above, but works with up to 64

64-bit elements in the V register; there are two vector logical functional units. Due to space constraints, the second vector logical unit uses part of the Floating-point Multiply unit and, thus, has takes longer than the Full Vector

Logical unit

Pop.parity Performs population counts and parity checks like scalar, above, but works

on elements within a vector register; leading zero counting is not performed in

this functional unit

Floating Point functional units (S and V registers only)

Addition Performs 64-bit addition or subtraction on very large or very small numbers and

can represent them using exponential notation and decimal points

Multiplication Performs 64-bit multiplication on the same types of numbers as in floating-point

addition; number rounding is available with this functional unit

assissing in the receipting is available with this functional unit

Reciprocal Performs an equivalent to a floating-point division by utilizing Newton's method of a series of reciprocal multiplications to achieve an "approximate" answer

# TABLE OF FUNCTIONAL UNITS

| UNIT                                   | REGISTER           | CLOCK<br>PERIODS |

|----------------------------------------|--------------------|------------------|

| ADDRESS FUNCTIONAL UNITS               |                    |                  |

| ADDITION<br>MULTIPLICATION             | A<br>A             | 2<br>4           |

| SCALAR FUNCTIONAL UNITS                |                    |                  |

| ADDITION<br>SHIFT                      | s                  | 3                |

| SINGLE                                 | s                  | 2                |

| DOUBLE                                 | S                  | 3                |

| LOGICAL                                | S                  | 1                |

| POPULATION, PARITY<br>AND LEADING ZERO | s_                 | 3 or 4           |

| VECTOR FUNCTIONAL UNITS                |                    | <u> </u>         |

| ADDITION                               | v                  | 3                |

| SHIFT                                  | Į v                | 3 or 4           |

| FULL VECTOR LOGICAL                    | V                  | 2                |

| 2ND VECTOR LOGICAL POPULATION, PARITY  | V                  | 5                |

| FLOATING-POINT<br>FUNCTIONAL UNITS     |                    |                  |

| ADDITION                               | S AND V            | 6 7              |

| MULTIPLICATION<br>RECIPROCAL APPROX.   | S AND V<br>S AND V | 1 4              |

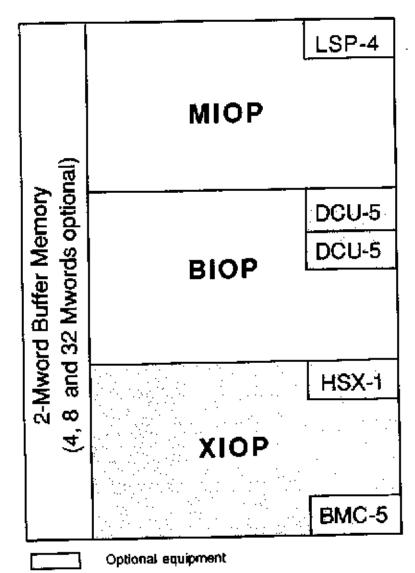

# IOS OPTIONS ON THE Y-MP

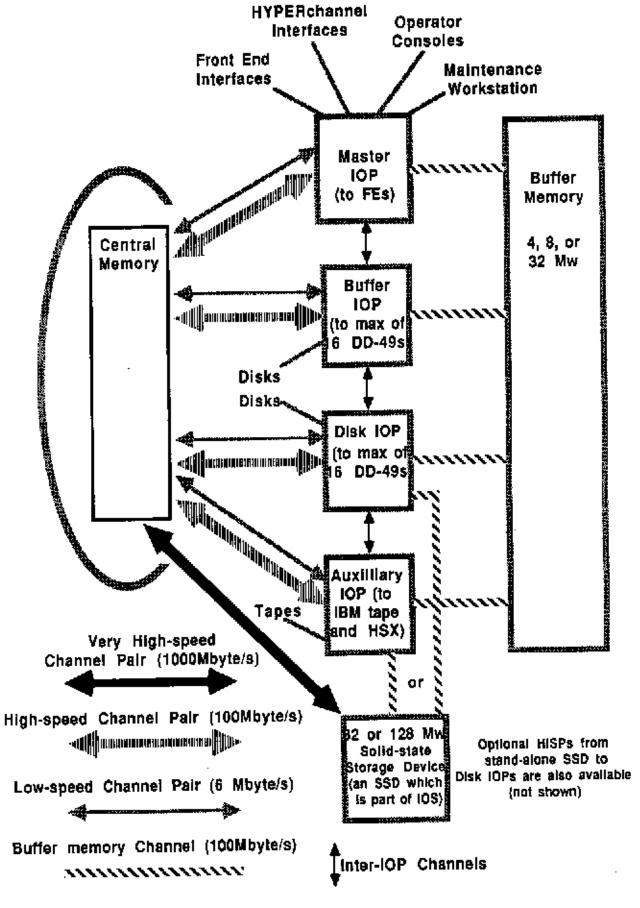

The Model D I/O Subsystem enhances the Y-MP models to enable fast, efficient data access and processing.

- Y-MP2 and Y-MP4 IOS configuration options include:

- one standard I/O subsystem containing an MIOP and a BIOP with expansion to include a DIOP and/or an XIOP

- one standard LSP-4 in the MiOP (which allows connections to the Cray mainframe and up to three front-end interfaces or Network Systems Corp. adapters) with expansion to include an optional LSP-4 (which adds four more FEI/NSC adapter connections)

- the BIOP and DIOP can hold up to three DCU-5 disk controllers each and each of them can drive four disk drives

- the XIOP can contain one HSX-1 (high-speed external channel connection) and up to two BMC-5 tape controllers which can support up to eight IBM tape channels

- 4 Mwords standard buffer memory, with options to expand to 8 or 32 Mwords

The IOS attaches to one side of the Y-MP4 as a "wing". The IOS on a Y-MP2 is situated in front facing the mainframe.

- Y-MP8 IOS configuration options include:

- one standard I/O subsystem containing an MIOP, a BIOP, a DIOP, and an XIOP; this IOS forms a "wing" on the mainframe

- · all of the above mentioned expansion options

- · the addition of a second IOS which faces the mainframe

# I/O Subsystem - Model D

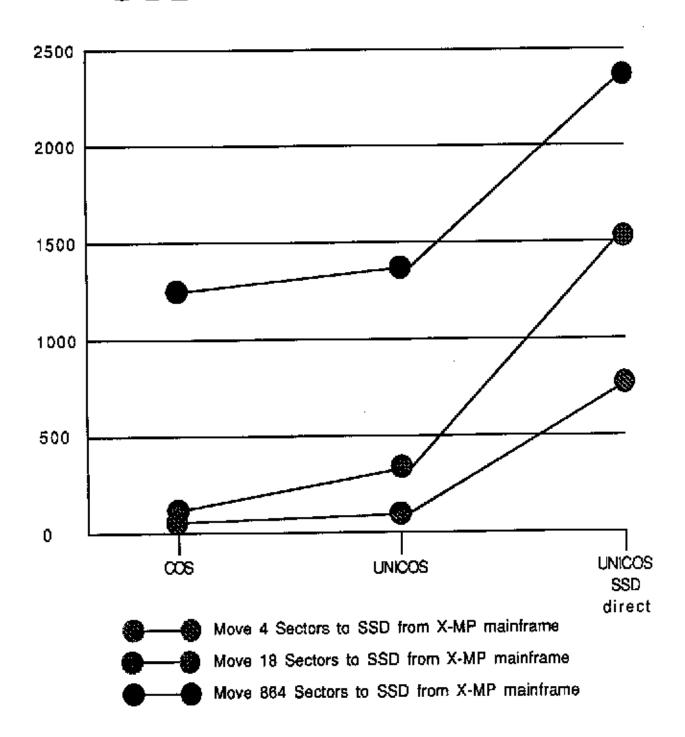

# SOLID-STATE STORAGE DEVICE (SSD) OPTIONS

- The SSD functions as a very high speed secondary memory and is looked at by the operating system and user as another disk drive

- The current memory size options are 128, 256, or 512 Mwords (a 32 or 128 Mword SSD can optionally be located in the I/O subsystem; this is the only option with the Y-MP2)

- The user accesses the SSD via Cray job statements with no changes to the program necessary

- Transfer rates are from 100 to 2000 Mbytes/second; access time is less than 25 microseconds

- Connects to:

CRAY Y-MP4 via one or two 1000 Mbytes/s channel CRAY Y-MP8 via one or two 1000 Mbytes/s channels (The optional 32 or 128 Mword SSD located in the I/O Subsystem is connected via one 1000 Mbytes/s channel.)

- An optional SSD direct connection to the IOS is available which can allow faster throughput of disk data to CRAY central memory

- Provides a significant performance improvement on I/O-bound programs

# SSD PERFORMANCE

#### CRAY Y-MP DISK DRIVE OPTIONS

#### CRAY Y-MP computers support:

- DS-40 disk subsystems

5.2 Gbytes capacity per DD-40 disk storage unit

20.8 Gbytes capacity per DS-40 (5.2 Gbytes x 4 DSUs/subsystem)

9.6 Mbyte/s sustained transfer rate for each DD-40 disk unit

16 ms average access time

DCU-5 controller

- DD-49 disk drives

1.2 Gbytes capacity

9.6 Mbyte/s sustained transfer rate

16 ms average access time

DCU-5 controller

- RDS-5 Disk System

4 Removable HDA Assemblies

1200 Mbyte capacity each

3.0 Mbyte/s transfer rate

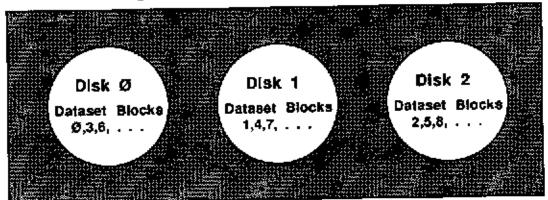

#### **DISK STRIPING**

- Software technique which allows an increase in disk transfer rate (up to a factor of 15 with a second IOS and UNICOS 5.0)

- Multiple disks are treated as one logical device

- Striped groups are limited to like disk types

- · Access via a single command

- Simultaneous I/O on all disks in the group

- Effective I/O rate is multiplied by the number of disks in the group

# History of Cray Disk Storage Devices

Discontinued

**Current Products**

| Model                  | DD-19         | DD-29         | DD-39         | DD-49         | DD-40         |

|------------------------|---------------|---------------|---------------|---------------|---------------|

| Manufacturer           | CDC           | CDC           | Fujitsu       | lbis          | CDC           |

| Storage Capacity       | 303 Mb        | 606 Mb        | 1238 Mb       | 1219 Mb       | 5200 Mb       |

| Transfer Rate<br>(max) | 32<br>Mbits/s | 32<br>Mbits/s | 52<br>Mbits/s | 82<br>Mbits/s | 82<br>Mbits/s |

| Drives per Device      | 1             | 1             | 3             | 1             | 4             |

| Cray systems           | 1,X           | 1,X,2         | X,Y           | X,2,Y         | X,2,Y         |

## Disk Striping

Disk Striping allows a group of disks to be viewed by the operating system and user as a single logical device, but which yields increased I/O performance.

A dataset residing on a striped disk group looks like this:

A read or write request to a dataset residing on a striped group can cause simultaneous I/O to occur on all disks in the group.

In effect, the I/O rate for the dataset is multiplied by the number of disks in the group.

All disks in the striped group must be the same type and must be connected to the I/O Subsystem.

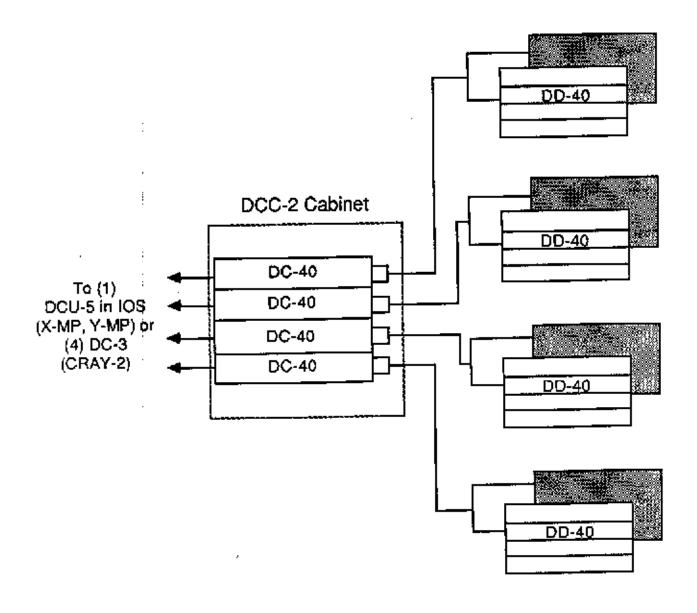

#### DAISY CHAINING

The DS-40 disk subsystem includes a facility to effectively allow doubling the storage capacity. This is known as daisy chaining.

Because each DC-40 disk controller in the DCC-2 chassis contains a dual-ported interface, as many as eight DSUs can be connected to the DCC-2 chassis. Only four DSUs can be active at one time, however.

The effect of daisy chaining a single subsystem doubles capacity from 21 Gbytes to 42 Gbytes (4 x 5200 Mbytes vs. 8 x 5200 Mbytes).

Note that this does not mean twice the performance since the chained devices share a single multiplexed channel to the DCU-5 in the IOS.

A Y-MP8 with two IOS Model Ds could have up to 48 disk storage units. Up to 96 disk storage units are possible with DS-40 daisy chaining yielding 249.6 Gbytes (499.2 Gbytes with daisy chaining).

#### **DS-40 OPTIONS**

|               |           |                     | Capacity               |                        |  |

|---------------|-----------|---------------------|------------------------|------------------------|--|

| CRAY<br>Model | IOS       | DS-40<br>Subsystems | Without daisy chaining | With daisy<br>chaining |  |

| Y-MP          | 1 Model D | 6 (24 DSUs)         | 124.8                  | 249.6                  |  |

| Y-MP          | 2 Model D | 12 (48 DSUs)        | 249.6                  | 499.2                  |  |

Capacity values are in Gbytes.

# DS-40 DISK SUBSYSTEM with daisy chaining

;

# CRAY Y-MP and CRAY X-MP COMPARISON

| <u></u>                                                        |                                                                   |                                                         |

|----------------------------------------------------------------|-------------------------------------------------------------------|---------------------------------------------------------|

| Characteristic                                                 | CRAY Y-MP Mainframe                                               | CRAY X-MP EA Mainframe                                  |

| Memory size<br>Banks                                           | 16, 32, 64, 128 Mwords<br>64, 128, 256                            | 4, 16, 32, 64 Mwords<br>16, 32, 64                      |

| CPUs                                                           | 1, 2, 4, 8                                                        | 1, 2, 4                                                 |

| A register width                                               | 24 bits (X-mode)<br>32 bits (Y-mode)                              | 24 bits (X-mode)<br>32 bits (Y-mode)                    |

| Address register width                                         | Od hite (V)                                                       | 24 bits (X-mode)<br>32 bits (Y-mode)                    |

| SB registers per cluste                                        | 0 v 04 JV marial                                                  | 8 x 24 (X-made)<br>8 x 32 (Y-made)                      |

| Clusters                                                       | 0, 3, 5, 9                                                        | 0, 3, 5                                                 |

| Instruction formats                                            | 1 and 2 parcels (X-mode)<br>1,2, and 3 parcels (Y-mode)           | 1 and 2 parcels (X-mode)<br>1,2, and 3 parcels (Y-mode) |

| Instruction expression (maximum width)                         | 24 bits (X-mode)<br>32 bits (Y-mode)                              | 24 bits (X-mode)<br>32 bits (Y-mode)                    |

| exp =                                                          | ijkm (X-mode)<br>nm (Y-mode)                                      | ijkm (X-mode)<br>nm (Y-mode)                            |

| Program block<br>Maximum size<br>Boundary                      | 4 Mwords<br>256 words                                             | 4 Mwords<br>256 words                                   |

| I/O channels 6 Mbyte/second 100 Mbyte/second 1000 Mbyte/second | 2, 4, 8<br>2, 4, 8<br>1, 2                                        | 1, 2, 3, 4<br>1, 2, 3, 4<br>1, 2                        |

| /O subsystems<br>Maximum IOPs                                  | 2 (1 is std., 1 more opt.<br>on Y-MP8)<br>(4 is std, 4 more opt.) | 1                                                       |

| Maint. workstation                                             | VMEbus system                                                     | VMEbus system                                           |

| rror Logger                                                    | VMEbus system                                                     | VMEbus system                                           |

| Operator workstation                                           | VMEbus system                                                     | VMEbus system                                           |

| Disk drives                                                    | DD-39s, DD-40s, DD-49s                                            | DD-39s, DD-40s, DD-49s                                  |

# CRAY Y-MP PURCHASE PRICES (Made available by instructor)

### SECTION 4

CRAY X-MP EA

**Computer System**

Crey Research, Inc. Software Training Section 200

THIS PAGE IS INTENTIONALLY LEFT BLANK.

#### **CRAY X-MP EA SYSTEMS**

The X-MP series of computers has been a mainstay of the Cray supercomputer product line since its introduction in 1982. Now, however, with the introduction of the new Y-MP models, most of the X-MP EA (as it is now known) models are being discontinued. The only X-MP EA models still being produced will be the "se" models described later in this section.

Below is a recap of the X-MP EA models that have been and will still be available along with some physical characteristics of them.

### CRAY X-MP EA SERIES OF SYSTEMS

| Model         | CPUs | Memory Size<br>(Mwords) | Banks | 10Рв  | Buffer Memory<br>(Mwords) |  |

|---------------|------|-------------------------|-------|-------|---------------------------|--|

| X-MP EA/1496  | 1    | 4                       | 16    | 2/3 g | 2/4/8/32                  |  |

| X-MP EA/18se  | 1    | 8                       | 16    | 2/3 % | 2/4/8/32                  |  |

| X-MP EA/116se | 1    | 16                      | 16    | 2/3 € | 2/4/8/32                  |  |

| X-MP EA/116 ' | 1    | 16                      | 32    | 2/3/4 | 4/8/32                    |  |

| X-MP EA/132 * | 1    | 32                      | 32    | 2/3/4 | 4/8/32                    |  |

| X-MP EA/164 * | 1    | 64                      | 64    | 2/3/4 | 4/8/32                    |  |

| X-MP EA/216 * | 2    | 16                      | 32    | 2/3/4 | 4/8/32                    |  |

| X-MP EA/232 * | 2    | 32                      | 32    | 2/3/4 | 4/8/32                    |  |

| X-MP EA/264 * | 2    | 64                      | 64    | 2/3/4 | 4/8/32                    |  |

| X-MP EA/416 * | 4    | 16                      | 32    | 2/3/4 | 4/8/32                    |  |

| X-MP EA/432 * | 4    | 32                      | 32    | 2/3/4 | 4/8/32                    |  |

| X-MP EA/464 * | 4    | 84                      | 64    | 2/3/4 | 4/8/32                    |  |

<sup>&</sup>quot;Qut of production

### PHYSICAL CHARACTERISTICS

|             | No. of    | Arc in         | 0 - 5    | Т           | KVA          |

|-------------|-----------|----------------|----------|-------------|--------------|

| Model .     | Columns - | <u>Degrees</u> | <u> </u> | <u>Тоŋs</u> | <u>Power</u> |

| X-MP EA/1se | 6         | 135            | 21       | 3.0         | 80           |

| X-MP EA/1   | 8         | 182            | 26       | 3.B         | 80           |

|             | _         | 182            | 26       | 3.8         | 80           |

| X-MP EA/2   | 8         |                | •        | 5.7         | 150          |

| X-MP EA/4   | 12        | 270            | 39       | 3.7         | 150          |

IOS weighs 1.7 tons, occupies 13 sq.ft. SSD weighs 1.7 tons, occupies 13 sq.ft.

<sup>† 1</sup> Mword = 1,048,576 words

# CRAY X-MP EA/se SYSTEMS OVERVIEW

Three models of the X-MP EA/se are now available and are the only X-MP systems still in production.

Each model is a complete system in six columns and contains one CPU. The only options are in the amount of central memory and the IOS options. The models are:

- X-MP EA/14se (4 Mwords of Static MOS memory in 16 banks)

- X-MP EA/18se (8 Mwords of Static MOS memory in 16 banks)

- X-MP EA/116se (16 Mwords of Static MOS memory in 16 banks)

The clock rate of the X-MP EA/se is 8.5 ns. Earlier versions with a 10.0 ns clock rate can be upgraded.

The X-MP EA/se can operate in either X-MP or Y-MP mode.

### CRAY X-MP EA/se

6-columns

Internal IOS

PDU attached

#### X-MP EA/se IOS CONFIGURATION OPTIONS

#### The standard built-in IOS system includes:

- An MIÓP

- A BIOP

- Two Mword buffer memory

- One 100 Mbyte/sec. channel

- · One 6 Mbyte/sec channel

- One LSP-4 for connecting to front-ends and networks

- · One DCU-5 for connecting to disk units

#### Options include:

- · Memory upgrades to 4, 8, or 32 Mwords

- An XIOP

- A BMC-5 for connecting to IBM tape equipment (requires an XIOP)

- One more DCU-5

No SSD options are available with the X-MP EA/se systems.

The X-MP EA/se supports the DD-49 disk units and the DS-40 disk subsystem.

# CRAY X-MP EA/se IOS Diagram

# CRAY X-MP EA/se PURCHASE PRICES (Made available by instructor)

### SECTION 5

Cray Product Familiarization

# CRAY-2

# **Computer System**

Cray Recearch, Inc.

Software

#### THIS PAGE IS INTENTIONALLY LEFT BLANK.

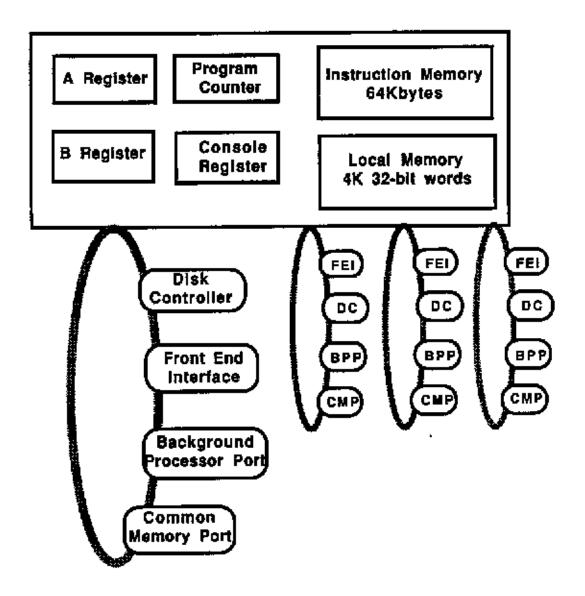

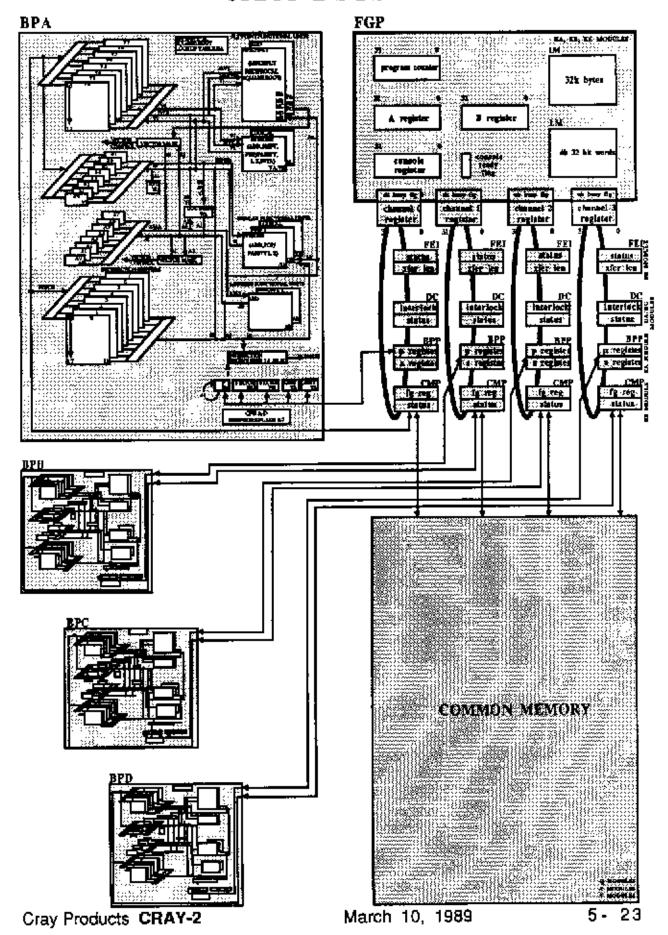

# CRAY-2 SUPERCOMPUTING PHILOSOPHY

- Design simplicity

- Few, very fast processors

High-speed logic circuits

Register-based

Fast scalar processing

Fast vector processing

- Parallel processing

Vector operations

Separate functional units

Multiple processors and multitasking

- Very high performance I/O

- Very large common memory

Highly interleaved memory

Accessible from each processor

- High availability

- Ease of system integration Networks and stations

- Standard software

Fortran

Operating system based on AT&T UNIX\* System V

\*UNIX is a trademark of AT&T Bell Laboratories

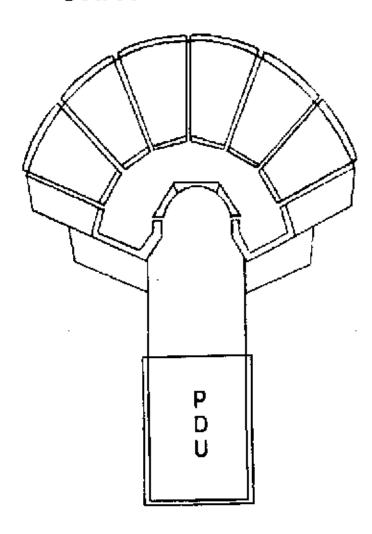

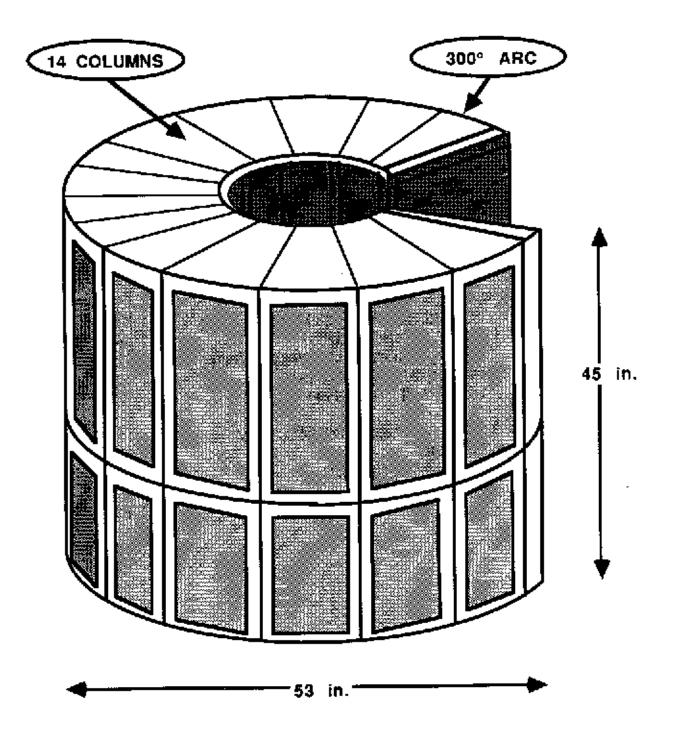

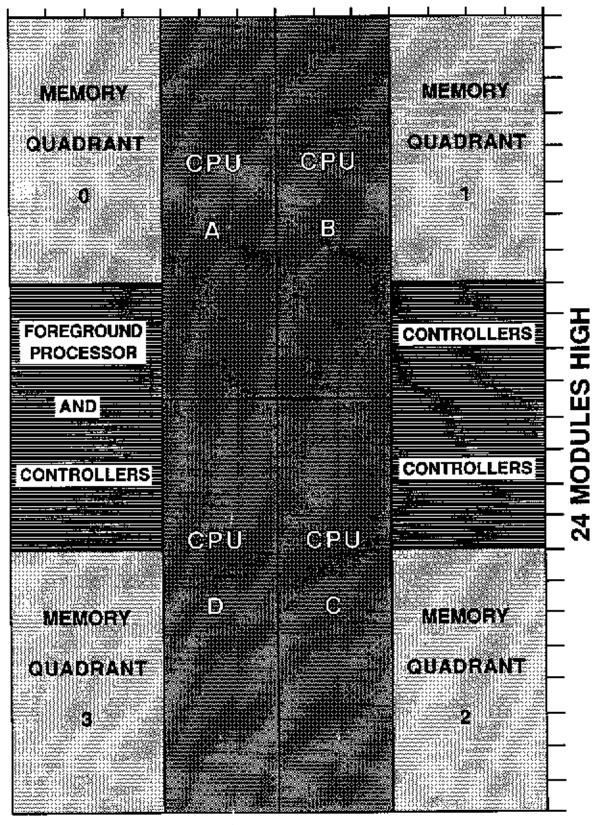

#### PHYSICAL APPEARANCE

- SMALL C-SHAPED CABINET CONTAINING 14 COLUMNS IN A 300° ARC

- COLUMNS ARRANGED IN A PARTIAL CIRCLE WITH A 20° ANGLE BETWEEN COLUMNS

- MODULES COMPRISE THE UPPER 24 INCHES OF EACH COLUMN.

- POWER SUPPLIES COMPRISE THE LOWER 19 INCHES OF EACH COLUMN

#### PHYSICAL CHARACTERISTICS

- 16 SQUARE FEET FLOOR SPACE

- 45 INCHES HIGH.

- 53 INCHES DIAMETER

- 2.75 TONS

5500 POUNDS FILLED 3495 POUNDS DRY (2005 POUNDS WEIGHT OF FLUORINERT)

- 2.96 POUNDS PER SQUARE INCH PRESSURE

- 195 KILOWATTS

- 14 COLUMNS IN 300° ARC 336 MODULES TOTAL

- 36,000 TWISTED PAIR WIRES

10 INCHES AVERAGE LENGTH

25 INCHES LONGEST

2.5 INCHES SHORTEST

5.68 MILES

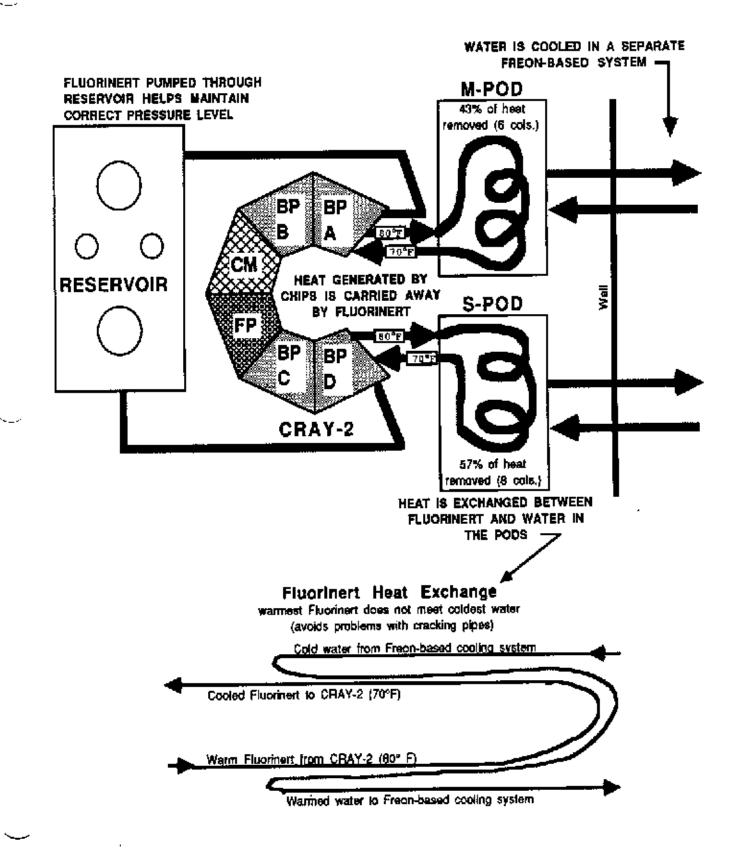

#### COOLING

- LIQUID IMMERSION COOLING ALLOWS DENSELY-PACKED ELECTRONICS

- "VALVELESS" COOLING SYSTEM

FLUOROCARBON FLUID 200 GALLONS

1 INCH/S FLOW RATE

70° F (21° C) CHASSIS ENTRY

80° F (27° C) CHASSIS EXIT

STAND PIPE AND RESERVOIR

SHELL AND TUBE HEAT EXCHANGE

- FLUOROCARBON FLUID (PRIMARY)

COLORLESS AND ODORLESS

INERT AND NONTOXIC

NONFLAMMABLE AND INSULATING

HIGH THERMAL STABILITY

HIGH HEAT TRANSFER

- CHILLED WATER COOLING (SECONDARY)

55 TONS

50° F (10° C) NORMAL

# CRAY-2 TWO-PHASE COOLING SYSTEM UTILIZING A DIELECTRIC SOLUTION (FLUORINERT), WATER, AND FREON

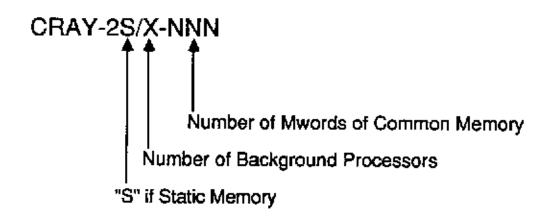

#### **CRAY-2 MODEL NUMBERING SCHEME**

Dynamic Memory Model

CRAY-2/4-256 CRAY-2/4-512 Static Memory Models

CRAY-2S/2-64 CRAY-2S/2-128 CRAY-2S/4-128

### **CRAY-2 OPTIONS**

|         | CRAY-2<br>Model | Number of<br>Background<br>Processors | Common<br>Memory<br>(Mwords) | Number of<br>Memory<br>Banks | Mwords<br>per<br>Bank | Number<br>of<br>I/O Ports |

|---------|-----------------|---------------------------------------|------------------------------|------------------------------|-----------------------|---------------------------|

| DYNAMIC | 4-256           | 4                                     | 256                          | 128                          | 2                     | 40                        |

| DYN,    | 4-512           | 4                                     | 512                          | 128                          | 4                     | 40                        |